#### Authentication and Obfuscation of Digital Signal Processing Integrated Circuits

# ${\bf A~DISSERTATION}$ SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{BY}$

Yingjie Lao

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS $\mbox{FOR THE DEGREE OF }$

**Doctor of Philosophy**

Advisor: Keshab K. Parhi

© Yingjie Lao 2015 ALL RIGHTS RESERVED

## Acknowledgements

First and foremost, I want to thank my advisor Prof. Keshab K. Parhi, for his continuing and fatherly encouragement, tremendous guidance, and financial support throughout my entire Ph.D. study at the University of Minnesota. Throughout the five years that he has been my advisor, he has served as an incredible inspiration and talented mentor in my educational and career development. He also gives me a lot of guidance and advice on my career development. As a student of him, I not only have developed expertise in several areas, but also have learned some important skills in research.

I also would like to thank Prof. Chris Kim, Prof. Marc Riedel, and Prof. Yousef Saad at the University of Minnesota, for their support as members of my Ph.D. committee and kind help throughout my graduate study.

My sincere thank also goes to my research group. I am grateful to Weikang Qian, Manohar Ayinala, Qianying Tang, Saroj Satapathy at the University of Minnesota, for their collaborations and valuable feedback to my research. I also would like to thank Renfei Liu, Te-Lung Kung, Zisheng Zhang, Yin Liu, Sohini Roychowdhury, Sayed Ahmad Salehi, Bo Yuan, Tingting Xu, Jieming Yin, Cong Ma, and Yang Su, for their support in my Ph.D. life.

Last but not the least, I am forever grateful to my mother Yuanfeng Xu, my father Youhong Lao, my mother in law Yajun Di, and my father in law Guolin Yang. Without their support, I would not have earned my Ph.D. degree. I would like to express my

dearest thanks to my wife Yuzhe Yang who has always been extremely understanding and supportive during my studies, and to my little daughter Clover for bringing so much happiness and joy into our life. My career and life are more meaningful because of the love and care that I have been privileged to receive from my whole family.

## Dedication

To my wife, Yuzhe, and my daughter, Clover, for their endless love.

#### Abstract

As electronic devices become increasingly interconnected and pervasive in people's lives, security, trustworthy computing, and intellectual property (IP) protection have notably emerged as important challenges for the next decade. The assumption that hardware is trustworthy and that security effort should only be focused on networks and software is no longer valid given globalization of integrated circuits and systems design and fabrication. In 2011, the Semiconductor Industry Association pegged the cost of electronics counterfeiting at US \$7.5 billion per year in lost revenue and tied it to the loss of 11,000 U.S. jobs [1]. From a national defense perspective, unsecured devices can be compromised by the enemy, putting military personnel and equipment in danger. Therefore, securing integrated circuit (IC) chips, in other words, hardware security, is extremely important.

This dissertation considers the design of highly secure digital signal processing circuits by employing both authentication-based and obfuscation-based approaches. In the first part of the dissertation, we focus on one emerging authentication-based solution: Physical Unclonable Function (PUF). We present novel reconfigurable PUF designs which could simultaneously achieve better reliability and security. We also present a systematic statistical analysis to quantitatively evaluate the performances of various multiplexer (MUX)-based PUFs. The statistical analysis results can be used to predict the relative advantages of various MUX-based PUF designs. These results can be used by the designer to choose a proper type of PUF or appropriate design parameters for a certain PUF based on the requirements of a specific application. Furthermore, a lightweight PUF-based local authentication scheme is also proposed, which eliminates the use of error correcting codes.

In the next part of the dissertation, we consider another hardware protection method: obfuscation. Hardware obfuscation is a technique by which the description or the structure of electronic hardware is modified to intentionally conceal its functionality, which makes it significantly more difficult to reverse engineer. Unlike these prior works, We start to look at Digital Signal Processing (DSP) circuits. In the literature, security aspect of DSP circuits has only attracted little attention. However, high-level transformations of DSP circuit are intrinsically suitable for hardware obfuscation, as these techniques only alter the structure of a circuit, while maintaining the original functionality. Based on this finding, we present a novel design methodology for obfuscated DSP circuits by hiding functionality via high-level transformations. The key idea is to generate meaningful and non-meaningful design variations by using high-level transformations.

In the final part of the dissertation, we consider the design and analysis of True Random Number Generator (TRNG), which is also an important topic in hardware security. We examine the modeling and statistical aspects of the proposed TRNG circuit. According to our model, we show that the performance of the beat-frequency detector based TRNG can be improved by appropriately adjusting design parameters. Motivated by the our analysis, we propose several alternate BFD-TRNG designs which could achieve improved performance. Various post-processing methods which are specific to the proposed designs are also studied.

## Contents

| A            | ckno                   | vledgements                                             | j   |  |  |

|--------------|------------------------|---------------------------------------------------------|-----|--|--|

| D            | edication              |                                                         |     |  |  |

| $\mathbf{A}$ | bstra                  | et                                                      | iv  |  |  |

| Li           | $\operatorname{st}$ of | Tables                                                  | xii |  |  |

| Li           | $\operatorname{st}$ of | Figures                                                 | xiv |  |  |

| 1            | Intr                   | oduction                                                | 1   |  |  |

|              | 1.1                    | Introduction                                            | 1   |  |  |

|              | 1.2                    | Summary of Contributions                                | 3   |  |  |

|              |                        | 1.2.1 Authentication                                    | 3   |  |  |

|              |                        | 1.2.2 Obfuscation                                       | 5   |  |  |

|              |                        | 1.2.3 True Random Number Generator                      | 6   |  |  |

|              | 1.3                    | Outline of the Dissertation                             | 7   |  |  |

| 2            | Nov                    | el Reconfigurable Silicon Physical Unclonable Functions | 9   |  |  |

|              | 2.1                    | Introduction                                            | 9   |  |  |

|              | 2.2                    | Background                                              | 11  |  |  |

|              |                        | 2.2.1 Silicon Physical Unclonable Function              | 11  |  |  |

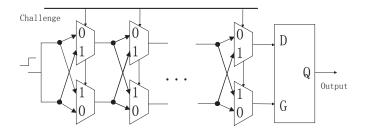

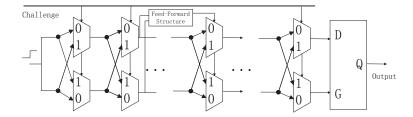

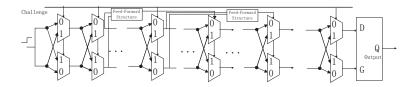

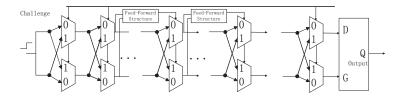

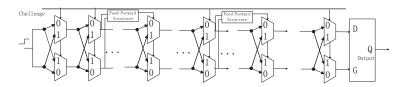

|   |      | 2.2.2    | Feed-Forward Structure                              | 12 |

|---|------|----------|-----------------------------------------------------|----|

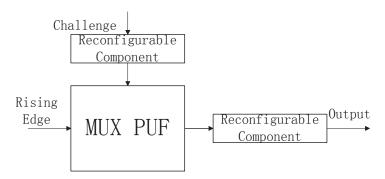

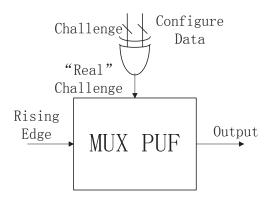

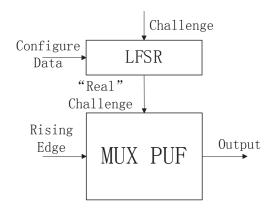

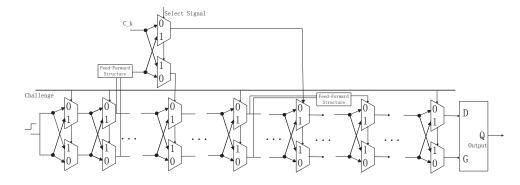

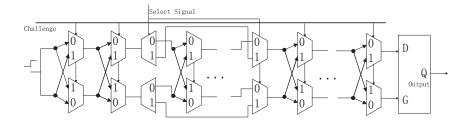

|   |      | 2.2.3    | Reconfigurable PUF                                  | 13 |

|   |      | 2.2.4    | PUF-based Key Generation and Authentication         | 15 |

|   | 2.3  | Metho    | odology                                             | 16 |

|   |      | 2.3.1    | PUF Model                                           | 16 |

|   |      | 2.3.2    | Simulation Model                                    | 18 |

|   | 2.4  | Novel    | Reconfigurable PUFs                                 | 19 |

|   |      | 2.4.1    | Reconfigurable Challenge and/or Response Structure  | 19 |

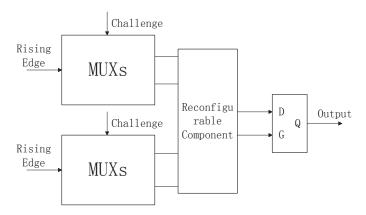

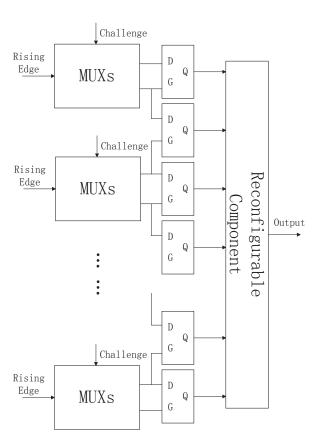

|   |      | 2.4.2    | Reconfigurable Circuit Structure                    | 26 |

|   | 2.5  | Exper    | imental Results                                     | 29 |

|   | 2.6  | Concl    | usion                                               | 33 |

| 3 | Stat | tistical | Analysis of MUX-based Physical Unclonable Functions | 34 |

|   | 3.1  | Introd   | luction                                             | 34 |

|   | 3.2  | Modif    | ied Feed-Forward MUX PUFs                           | 37 |

|   |      | 3.2.1    | Modified Feed-Forward Path                          | 37 |

|   |      | 3.2.2    | Different Types of Modified Feed-Forward MUX PUFs   | 38 |

|   | 3.3  | Defini   | tion of PUF Performance                             | 39 |

|   |      | 3.3.1    | Reliability                                         | 39 |

|   |      | 3.3.2    | Uniqueness                                          | 40 |

|   |      | 3.3.3    | Randomness                                          | 41 |

|   | 3.4  | Perfor   | mance Analysis of the Original MUX PUF              | 41 |

|   |      | 3.4.1    | Physical Component Modeling of MUX-based PUFs       | 41 |

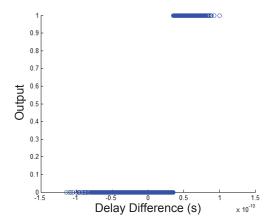

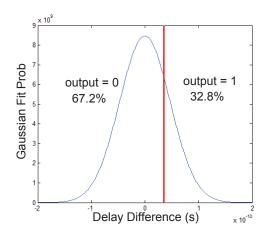

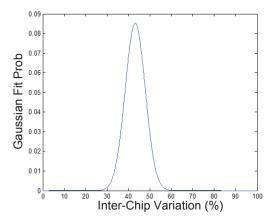

|   |      | 3.4.2    | Probability Distribution of Output Delay Difference | 43 |

|   |      | 3.4.3    | Effect of Number of Stages                          | 45 |

|   |      | 3.4.4    | Statistical Properties of the Original MUX PUF      | 45 |

|   |      | 2 1 5    | Dogian Evennla                                      | 50 |

|   | 3.5 | Perfor | rmance Analysis of Feed-Forward MUX PUFs and MUX/DeMUX             |    |

|---|-----|--------|--------------------------------------------------------------------|----|

|   |     | PUF    |                                                                    | 51 |

|   |     | 3.5.1  | Statistical Properties of Feed-Forward MUX PUF                     | 52 |

|   |     | 3.5.2  | Statistical Properties of Modified Feed-Forward MUX PUF $$         | 53 |

|   |     | 3.5.3  | Statistical Properties of Different Types of Modified Feed-forward |    |

|   |     |        | MUX PUFs                                                           | 59 |

|   |     | 3.5.4  | Statistical Properties of MUX/DeMUX PUF                            | 62 |

|   | 3.6 | Perfor | rmance Comparison of Various MUX-based PUFs                        | 64 |

|   | 3.7 | Exper  | iments                                                             | 65 |

|   |     | 3.7.1  | Experimental Setup                                                 | 65 |

|   |     | 3.7.2  | Results                                                            | 65 |

|   |     | 3.7.3  | Discussion                                                         | 67 |

|   | 3.8 | Concl  | usion                                                              | 67 |

|   |     |        |                                                                    |    |

| 4 |     |        | ht, Secure, and Reliable PUF-based Local Authentication            |    |

|   |     |        | Correction                                                         | 69 |

|   | 4.1 |        | luction                                                            | 69 |

|   | 4.2 | Backg  | ground                                                             | 70 |

|   |     | 4.2.1  | PUF-based Authentication                                           | 70 |

|   |     | 4.2.2  | Error Correction                                                   | 72 |

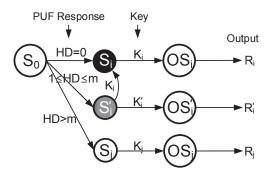

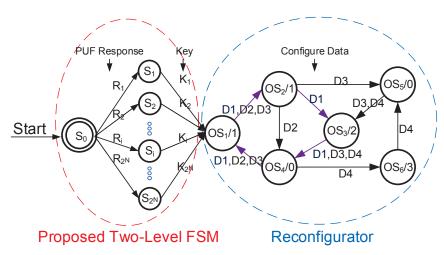

|   | 4.3 | Two-I  | Level FSM Architecture                                             | 74 |

|   | 4.4 | Error  | Correction based on the Two-Level FSM                              | 78 |

|   |     | 4.4.1  | Self-Correcting Functionality                                      | 78 |

|   |     | 4.4.2  | Advantages                                                         | 81 |

|   | 4.5 | Other  | Applications                                                       | 83 |

|   |     | 4.5.1  | Two-Factor Authentication                                          | 84 |

|   |     | 4.5.2  | Signature Generation                                               | 84 |

|   |     | 4.5.3  | Obfuscation                                                        | 86 |

|   |     | 4.5.4   | Correcting Other Errors                                 | 87  |

|---|-----|---------|---------------------------------------------------------|-----|

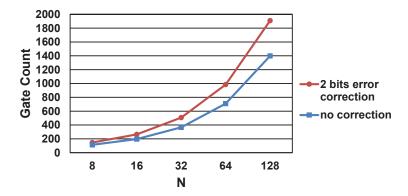

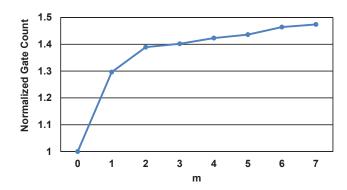

|   | 4.6 | Hardw   | vare Implementation                                     | 87  |

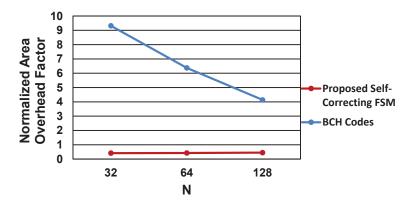

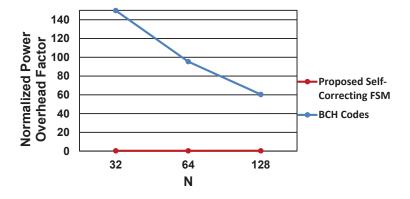

|   |     | 4.6.1   | Area and Power                                          | 87  |

|   |     | 4.6.2   | Comparison to BCH Codes                                 | 90  |

|   | 4.7 | Conclu  | asion                                                   | 92  |

| 5 | Obf | uscatii | ng DSP Circuits via High-Level Transformations          | 93  |

|   | 5.1 | Introd  | uction                                                  | 93  |

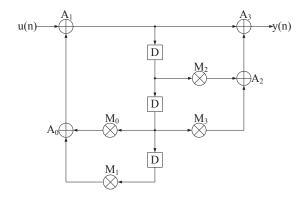

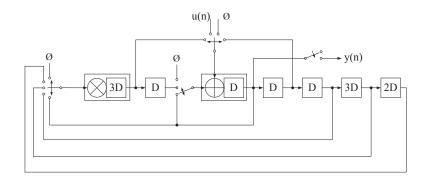

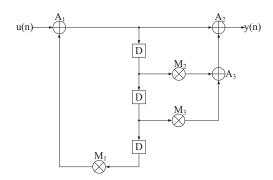

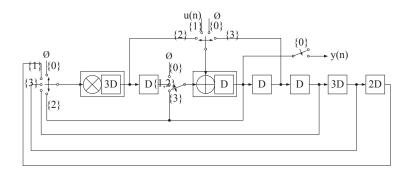

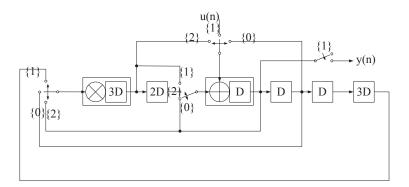

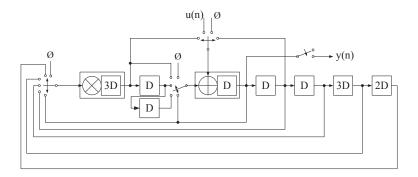

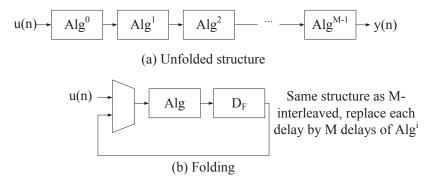

|   | 5.2 | Hiding  | g Functionality by High-Level Transformations           | 95  |

|   | 5.3 | Obfus   | cated Design via High-Level Transformations             | 101 |

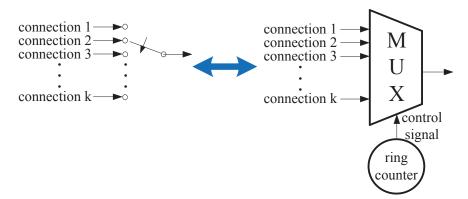

|   |     | 5.3.1   | Secure Switch Design                                    | 101 |

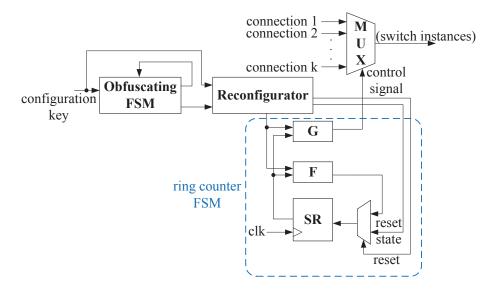

|   |     | 5.3.2   | Reconfigurable Switch Design                            | 102 |

|   | 5.4 | Gener   | ation of Variation Modes                                | 104 |

|   |     | 5.4.1   | Security Perspective of Variation Modes                 | 104 |

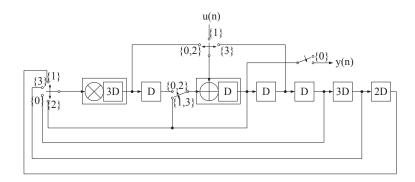

|   |     | 5.4.2   | A Case Study: Hierarchical Contiguous Folding Algorithm | 106 |

|   | 5.5 | Design  | a Flow of the Proposed DSP Circuit Obfuscation Approach | 108 |

|   |     | 5.5.1   | Design Methodology                                      | 108 |

|   |     | 5.5.2   | Architecture of the Obfuscated DSP Circuits             | 109 |

|   | 5.6 | Securi  | ty and Resiliency against Attacks                       | 110 |

|   |     | 5.6.1   | Attacks and Countermeasures                             | 110 |

|   |     | 5.6.2   | Measure of Obfuscation Degree                           | 112 |

|   |     | 5.6.3   | Improving the Security by Key Encoding                  | 114 |

|   |     | 5.6.4   | Security Properties                                     | 114 |

|   | 5.7 | Evalua  | ation of the Proposed Methodology                       | 115 |

|   |     | 5.7.1   | Overhead Impact                                         | 115 |

|   |     | 5.7.2   | Overhead Reduction                                      | 123 |

|   | 5.8 | Comp    | arison to existing obfuscation methods                  | 124 |

|   | 5.9 | Concl   | usion and Future Work                                   | 125 |

| 6 | Bea  | t Freq  | uency Detector based True Random Number Generator         | s:  |

|---|------|---------|-----------------------------------------------------------|-----|

|   | Stat | istical | Modeling and Analysis                                     | 127 |

|   | 6.1  | Introd  | uction                                                    | 127 |

|   | 6.2  | Beat I  | Frequency Detector based TRNG                             | 129 |

|   | 6.3  | Physic  | tal Component Modeling of RO TRNGs                        | 131 |

|   | 6.4  | Statist | cical Analysis of BFD-TRNG                                | 133 |

|   |      | 6.4.1   | BFD Model                                                 | 133 |

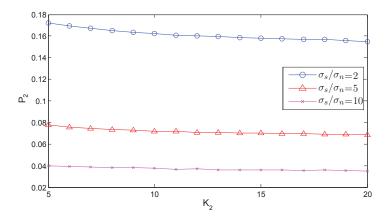

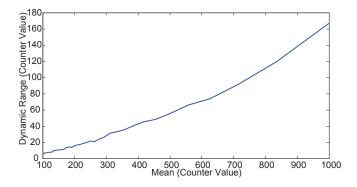

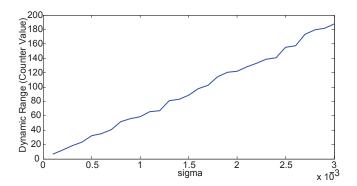

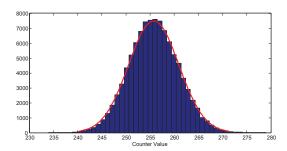

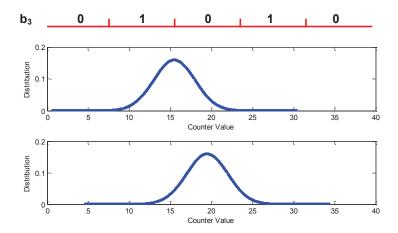

|   |      | 6.4.2   | Effect of Counter Value                                   | 134 |

|   |      | 6.4.3   | Bounds on Bias of Each Bit                                | 139 |

|   |      | 6.4.4   | Post-Processing                                           | 145 |

|   |      | 6.4.5   | Online Test and Feedback Control                          | 147 |

|   | 6.5  | Altern  | ate BFD-TRNG Architectures                                | 148 |

|   |      | 6.5.1   | Parallel Structure                                        | 148 |

|   |      | 6.5.2   | Cascade Structure                                         | 149 |

|   |      | 6.5.3   | Parallel-Cascade Structure                                | 151 |

|   | 6.6  | Compa   | arison with Other Existing ROSC based TRNGs               | 153 |

|   |      | 6.6.1   | Two-Oscillator TRNG                                       | 153 |

|   |      | 6.6.2   | ROSC TRNG with XOR Tree                                   | 154 |

|   |      | 6.6.3   | Comparison                                                | 156 |

|   | 6.7  | Conclu  | asion and Future Work                                     | 160 |

| _ | ~    |         |                                                           |     |

| 7 |      |         | and Future Directions                                     | 161 |

|   | 7.1  | Conclu  | sion                                                      | 161 |

|   | 7.2  | Future  | e Directions                                              | 162 |

|   |      | 7.2.1   | Evaluate and Attack PUFs                                  | 162 |

|   |      | 7.2.2   | Obfuscation CAD Tool                                      | 163 |

|   |      | 7.2.3   | DSP Circuit Reverse Engineering                           | 164 |

|   |      | 7.2.4   | Security in Emerging Technologies based Computing Systems | 165 |

References 167

## List of Tables

| 2.1 | Simulation Results: Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Simulation Results: Reconfigurability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33 |

| 3.1 | Notation Used in the Chapter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

| 3.2 | Predicted Performance of the Original MUX PUFs for Different Number of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|     | Stages (N) Obtained by Statistical Analysis Using the Model Derived from Ex-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

|     | perimental Results with N=100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 51 |

| 3.3 | Performances of Different Feed-Forward MUX PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54 |

| 3.4 | Theoretical Performance Indicators Comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 64 |

| 3.5 | Results of Inter-Chip and Intra-Chip Variations for 100-Stage PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66 |

| 3.6 | Results of Performance Indicators for 100-Stage PUFs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67 |

| 4.1 | Key Values Can Successfully Authenticate the Corresponding PUF Response $% \left( 1\right) =\left( 1\right) +\left( 1\right) +\left($ | 76 |

| 4.2 | Key Values Can Successfully Authenticate the Corresponding PUF Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

|     | with Self-Correction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 80 |

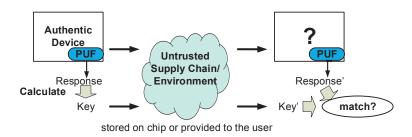

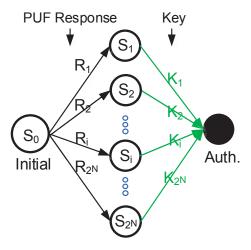

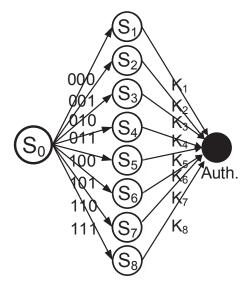

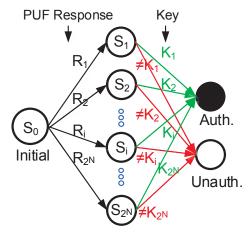

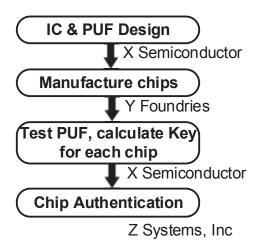

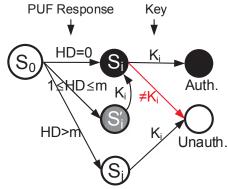

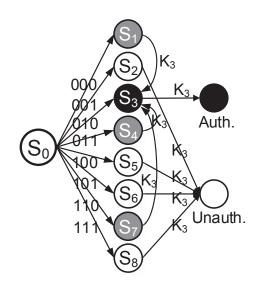

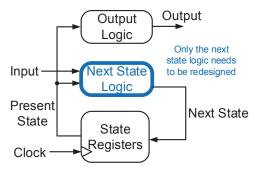

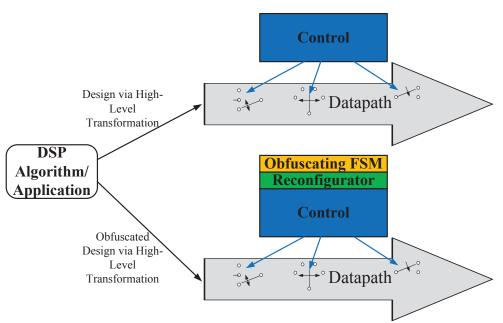

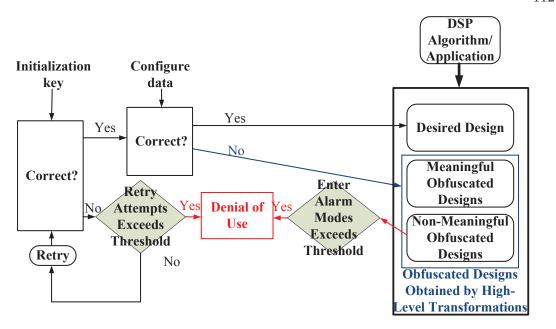

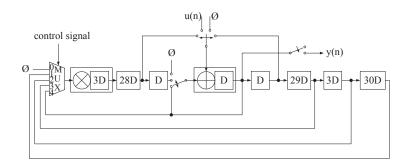

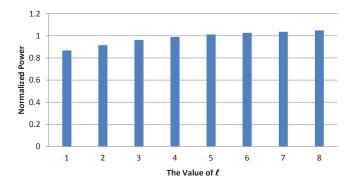

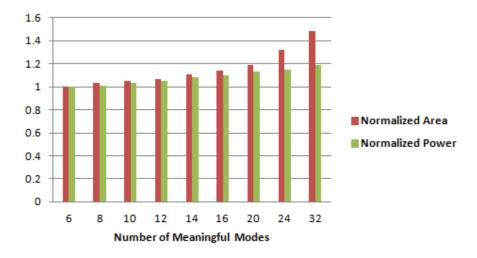

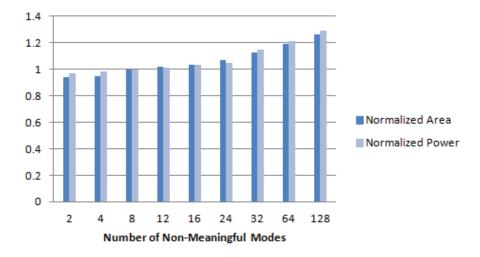

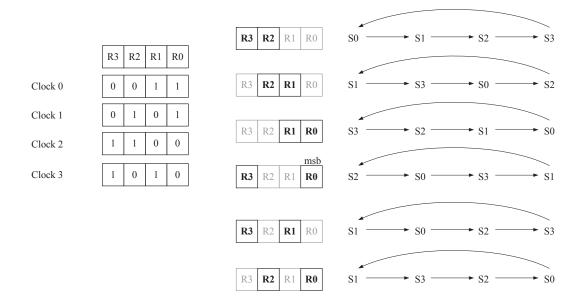

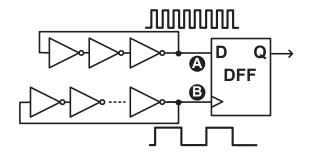

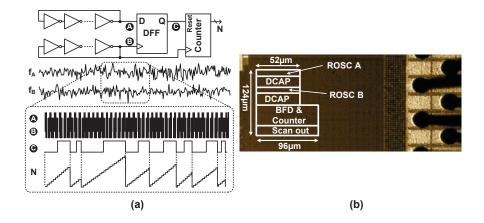

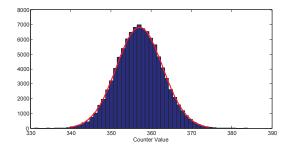

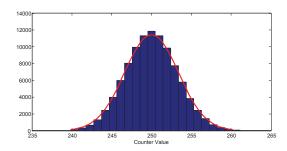

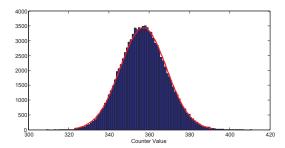

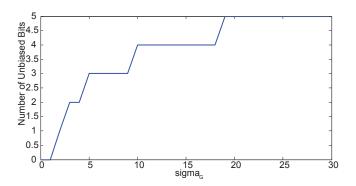

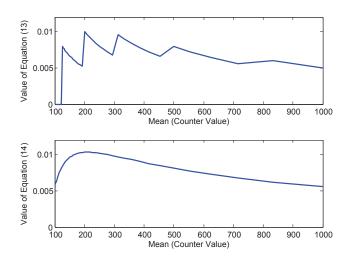

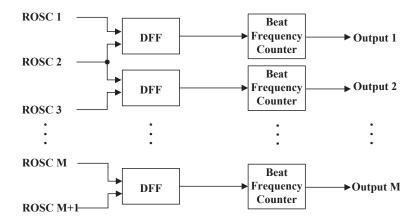

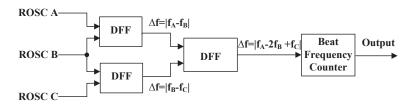

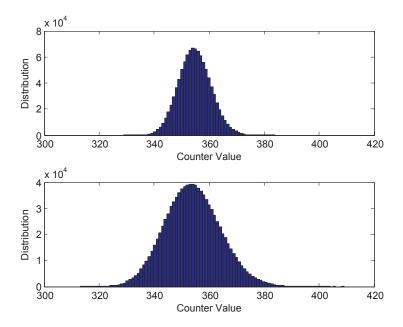

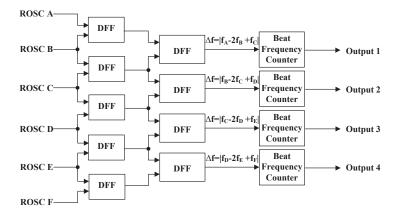

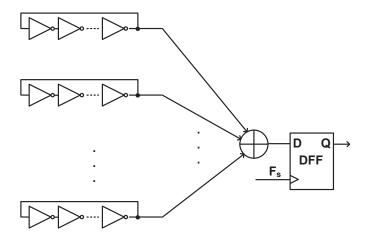

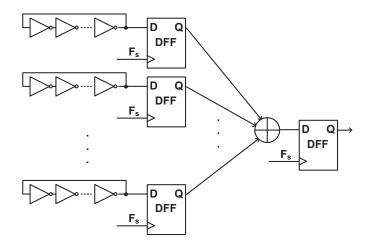

| 4.3 | Key Values Can Successfully Authenticate the Corresponding PUF Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |