## Scalable LO Distribution Schemes For Building Large-scale Phased Arrays

A THESIS

## SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

Ruixing He

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

## FOR THE DEGREE OF

## DOCTOR OF PHILOSOPHY

October, 2022

© Ruixing He 2022

ALL RIGHTS RESERVED

## Acknowledgements

First and foremost I am extremely grateful to my supervisor Professor Yahya Tousi for his invaluable advice, continuous support, and patience during my Ph.D. study. His immense knowledge and plentiful experience have encouraged me in all the time of my academic research and daily life. I would like thank the members of my dissertation committee including Professor Ramesh Harjani, Professor Rhonda Franklin, Professor Roger Rusack and again my advisor, Professor Yahya Tousi - not only for their time and extreme patience, but for their intellectual contributions to my development as a researcher.

Getting through my dissertation required more than academic support, and I have many, many people to thank for listening to and, at times, having to tolerate me over the past few years. I cannot begin to express my gratitude and appreciation for their friendship. Vijay Panda, Jitesh Poojary, Wen Zhou, Diba Dehmeshki and Alireza Rouhafza have been unwavering in their personal and professional support during the time I spent at the University. For many memorable evenings out and in, I must thank everyone above as well as Vinuth Nagendra and Tao He. Finally, I must express my very profound gratitude to my parents for providing me with unfailing support and continuous encouragement throughout my years of study and through the process of researching and writing this thesis. This accomplishment would not have been possible without them. Thank you.

#### Abstract

Facing the increasing demands of mmWave communication systems nowadays and the inherent adversity of higher signal attenuation in mm-wave wireless transmission, there is a continuous effort towards building larger scale phased arrays to achieve better effective isotropically radiated power (EIRP) and directivity. One of the critical challenges in array design is how to achieve frequency and phase synchronization in a scalable manner, which requires not only cell-level circuit optimizations but more importantly innovations at the architecture level.

In this thesis, we present three scalable schemes towards building large-scale active arrays with multiple local oscillators (LOs). First, a coupled oscillator array (COA) scheme based on unidirectional coupling is proposed. We derive the equilibrium states for the COA and demonstrate that our scaling scheme will preserve the steady state modes during scaling resulting in a predictable phase profile. We further evaluate the stability condition using the perturbation method. Based on the simulation results, we find that as long as the mismatches in the free-running frequencies are below a theoretical threshold, the scaled array could tolerate the presented element-to-element variations and could achieve frequency synchronization in a scalable manner.

Next, we present a two-dimensional coupled phase-locked loop array (CPLLA) scheme using type-II phase locked loop (PLL) as unit cell. Beside the concept of phase locking between multiple oscillators, we implement a chip prototype of the PLL array at 28GHz. The chip performance is characterized by on-wafer probing. The measurement indicates that the out-of-band phase noise of the distributed array does not depend on the number of elements. However, we find several undesired issues including in-band phase noise degradation and stability issue with the taped out chip. In order to identify the reason behind the flawed performance, a theory of phase control conflicting between PLL loop and injection locking is proposed. We later verify our theory with the post-taped-out simulation which achieves consistent results with the measured data.

Finally, We adjust the method of mm-wave signal generation and distribution, and propose a new phase self-aligning array architecture. A prototype is made to demonstrate the phase self-aligning between a  $1 \times 2$  array. The measured results verify our theoretical analysis, and show accurate phase control and a fast switching time with high spectral purity. As a result, we believe that the presented element-to-element selfalignment method is applicable for distributed tuning and control of scalable phased arrays without the need of extensive baseband calibration.

## Contents

| A             | ckno               | wledgements                                      | i  |

|---------------|--------------------|--------------------------------------------------|----|

| A             | Abstract           |                                                  |    |

| $\mathbf{Li}$ | List of Tables vii |                                                  |    |

| $\mathbf{Li}$ | st of              | Figures                                          | ix |

| 1             | LO                 | Distribution of Large-scale Phased Arrays        | 1  |

|               | 1.1                | mmWave Phased Arrays and The Scaling Challenges  | 1  |

|               | 1.2                | Coupled Oscillator Array                         | 5  |

|               | 1.3                | Coupled PLL Array                                | 7  |

|               | 1.4                | Drawbacks in Conventional mmWave Phase Control   | 9  |

| 2             | Sca                | lable Oscillator Array Using Unilateral Coupling | 13 |

|               | 2.1                | Introduction                                     | 14 |

|               | 2.2                | Steady-state Analysis: A Case Study              | 16 |

|   | 2.3 | Stability Analysis: A Case Study                       | 19 |

|---|-----|--------------------------------------------------------|----|

|   | 2.4 | Scalable Array Analysis: The General Model             | 22 |

|   |     | 2.4.1 Analysis of steady-state modes                   | 22 |

|   |     | 2.4.2 Transient Simulation                             | 24 |

|   | 2.5 | Summary                                                | 31 |

| 3 | Cou | pled PLL Array                                         | 32 |

|   | 3.1 | Introduction                                           | 32 |

|   | 3.2 | Array Architecture and Stability Analysis              | 34 |

|   | 3.3 | Circuit Design and Implementation                      | 37 |

|   | 3.4 | Prototype Measurement                                  | 41 |

|   |     | 3.4.1 Stability Analysis Considering Magnetic Coupling | 46 |

|   | 3.5 | Summary                                                | 51 |

| 4 | Aut | conomous Array of Phase Self-alignment                 | 53 |

|   | 4.1 | Introduction                                           | 53 |

|   | 4.2 | Interferometer-based Phase Sensing                     | 55 |

|   | 4.3 | mm-Wave Phase Detector                                 | 61 |

|   | 4.4 | Array Architecture                                     | 65 |

|   | 4.5 | Circuit Design and Implementation                      | 69 |

|   |     | 4.5.1 Interferometer and Peak Detector                 | 69 |

|   |     | 4.5.2 Frequency Multiplier Chain                       | 73 |

| $\mathbf{R}$ | References |         |                                              | 104 |

|--------------|------------|---------|----------------------------------------------|-----|

| 5            | Cor        | nclusio | n and Future Direction                       | 101 |

|              | 4.7        | Summ    | ary                                          | 98  |

|              | 4.6        | Proto   | type Measurement                             | 85  |

|              |            | 4.5.6   | Phase Inaccuracy in The Presence of Mismatch | 82  |

|              |            | 4.5.5   | Noise Analysis                               | 79  |

|              |            | 4.5.4   | Stability Analysis                           | 77  |

|              |            | 4.5.3   | Phase Control                                | 75  |

## List of Tables

| 3.1 | Measured phase noise for different array configurations at 28GHz | 45  |

|-----|------------------------------------------------------------------|-----|

| 4.1 | Comparison with the state-of-art prior work.                     | 100 |

# List of Figures

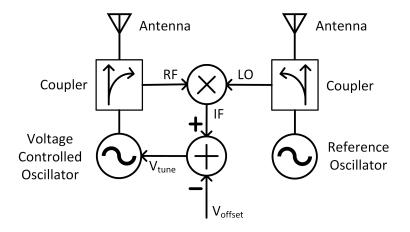

| 1.1 | PLL applied to a $1 \times 2$ oscillator array                                                                                                       | 8  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

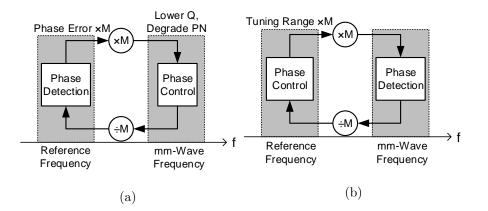

| 1.2 | Two schemes for mm-wave signal generation: (a) The conventional scheme                                                                               |    |

|     | detects phase at the reference frequency and controls it at the mm-wave                                                                              |    |

|     | frequency. (b) The scheme proposed in chapter four detects phase at the                                                                              |    |

|     | mm-wave frequency and controls it at the reference frequency                                                                                         | 10 |

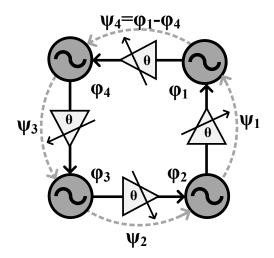

| 2.1 | The diagram of ring made of four unilateral coupled oscillators                                                                                      | 15 |

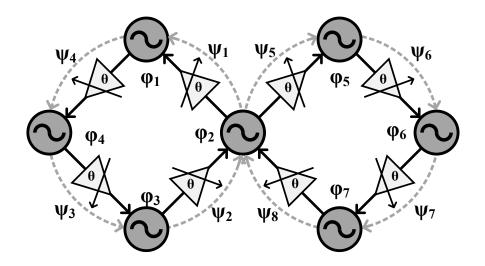

| 2.2 | The diagram of the example array made of two ring array sharing one                                                                                  |    |

|     | oscillator at the vertex.                                                                                                                            | 16 |

| 2.3 | Gershgorin circles and the distribution of eigenvalues for (a) four-oscillator $% \left( {{\left( {{{\bf{n}}} \right)} \right)_{\rm{cons}}} \right)$ |    |

|     | ring and (b) two-ring array.                                                                                                                         | 20 |

| 2.4 | All non-zero $\operatorname{Re}\{\lambda\}$ for the two-ring array across different modes of op-                                                     |    |

|     | eration. The shaded areas represent stable regions. $\ldots$                                                                                         | 21 |

| 2.5 | Proposed scheme for expanding the coupled array structure. The dimen-                                                                                |    |

|     | sions scale using the shared-vertex technique                                                                                                        | 23 |

| 2.6  | All non-zero $\operatorname{Re}\{\lambda\}$ for the 4×4 array across different modes of operation. |    |

|------|----------------------------------------------------------------------------------------------------|----|

|      | The shaded areas in green color represent stable regions                                           | 25 |

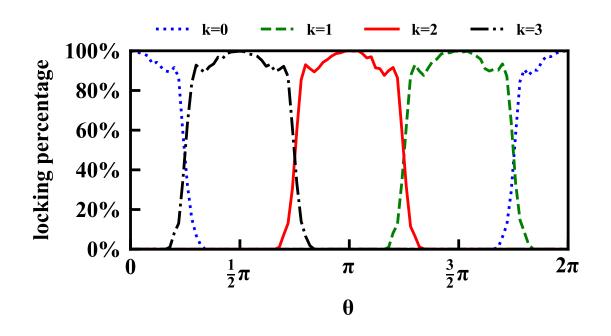

| 2.7  | Probability density distribution associated with four fundamental stable                           |    |

|      | modes $(\psi_i^0 = k\pi/2, \ k = 0, 1, 2, 3)$ in the 4×4 array. For each $\theta$ , we run         |    |

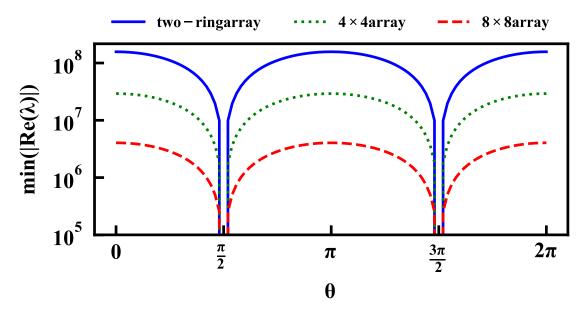

|      | 500 iterations with random initial phases to get the statistical result                            | 26 |

| 2.8  | Array time constant derived from $\min(  \operatorname{Re}\{\lambda\}  )$ . Each plot represents a |    |

|      | particular array size                                                                              | 27 |

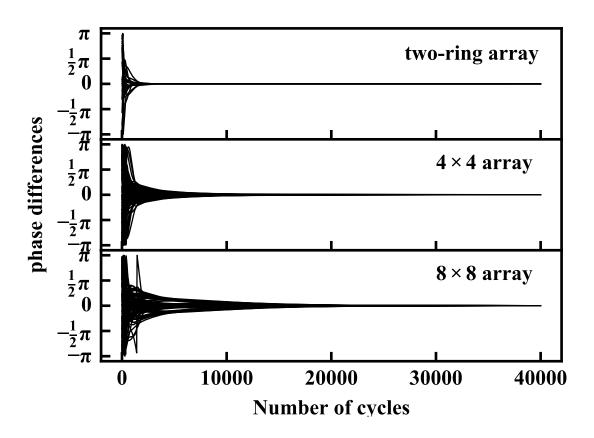

| 2.9  | Transient response of individual elements when the coupled array is set-                           |    |

|      | tling to $\boldsymbol{\psi} = 0.$                                                                  | 28 |

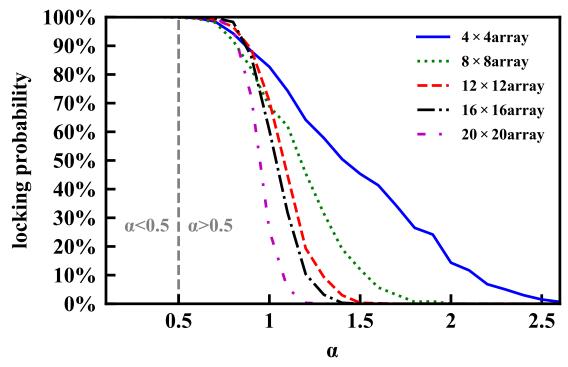

| 2.10 | Probability of synchronization in the presence of element-to-element vari-                         |    |

|      | ation in the array. $\alpha$ represents random frequency variation relative to                     |    |

|      | the locking bandwidth. For each array size, we run 500 iterations with                             |    |

|      | random initial phases at a fixed $\theta~(\theta=0)$ to get the statistical result                 | 30 |

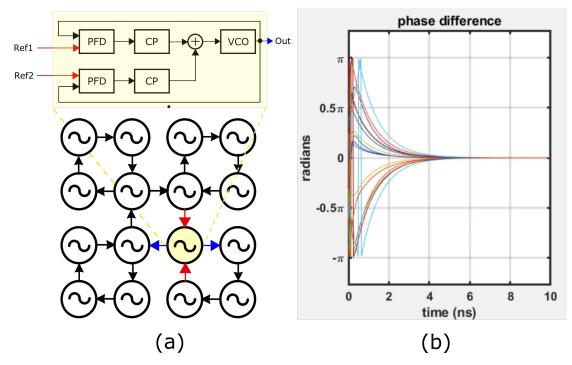

| 3.1  | (a) Top: structure of the unit PLL, Bottom: a PLL array example. (b)                               |    |

|      | Simulated phase locking of the distributed array                                                   | 35 |

| 3.2  | Top level block diagram of the distributed PLL with re-configurable in-                            |    |

|      | terconnects.                                                                                       | 39 |

| 3.3  | Unit PLL circuit.                                                                                  | 40 |

| 3.4  | Chip microphoto                                                                                    | 42 |

| 3.5  | Measured spectrum and reference spurs in the stand-alone PLL                                       | 43 |

х

| 3.6  | Measured phase noise plot for 6 different array configurations: direct        |    |

|------|-------------------------------------------------------------------------------|----|

|      | connection, 3x daisy chains, triangular and rectangular loops                 | 44 |

| 3.7  | (a) EM modeling of two adjacent on-chip inductors in SONNET. (b)              |    |

|      | Equivalent circuit model.                                                     | 47 |

| 3.8  | The coupling coefficient, $k$ , is inversely depended on the distance between |    |

|      | the adjacent inductors                                                        | 48 |

| 3.9  | (a) Transient phase of element 1-4 inside a $1\times 4$ CPLLA after the array |    |

|      | settles into steady state. The magnetic coupling is not included in the       |    |

|      | simulation. (b) Transient phase of VCO element 1-4 inside a $1\times 4$ array |    |

|      | after the array settles into steady state. The magnetic coupling are mod-     |    |

|      | eled between each pair of adjacent inductors with $k=0.007$ , but all PLL     |    |

|      | control loops are disabled                                                    | 49 |

| 3.10 | Transient waveform at the control node of each PLL inside a $1\times4$ CPLLA. |    |

|      | (a) PLL operates without the magnetic coupling. (b) The magnetic cou-         |    |

|      | pling is included besides the PLL operation.                                  | 52 |

| 4.1  | Two schemes for mm-wave signal generation: (a) The conventional scheme        |    |

|      | detects phase at the reference frequency and controls it at the mm-wave       |    |

|      | frequency. (b) The scheme proposed in chapter four detects phase at the       |    |

|      | mm-wave frequency and controls it at the reference frequency                  | 54 |

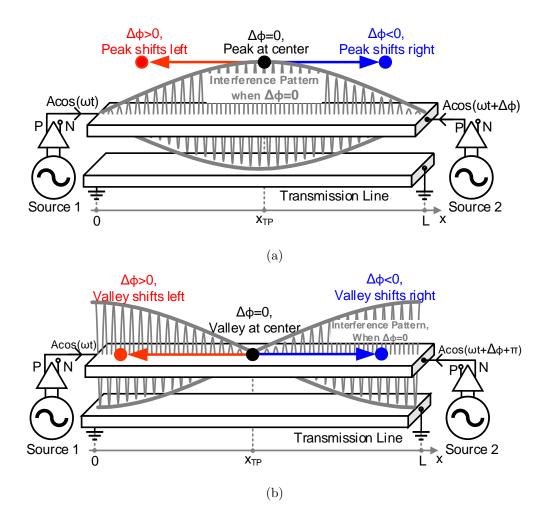

| 4.2 | Proposed interferometer: (a) Connected with the same polarity, two mm-                                   |    |

|-----|----------------------------------------------------------------------------------------------------------|----|

|     | wave sources would generate an interference pattern with a peak on the                                   |    |

|     | transmission line. (b) Connected with the opposite polarity, the gener-                                  |    |

|     | ated interference pattern has a valley. The position of the peak or valley                               |    |

|     | shifts along the line as a function of $\Delta \phi$                                                     | 56 |

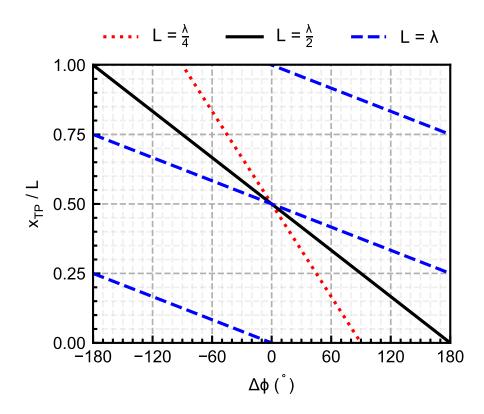

| 4.3 | The normalized location of the turning point as a function of $\Delta\phi$ for three                     |    |

|     | different lengths of the transmission line: $\lambda/4$ , $\lambda/2$ , and $\lambda$                    | 57 |

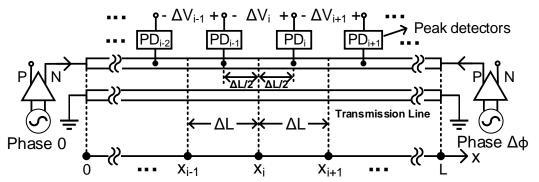

| 4.4 | Diagram of the proposed phase detector based on multiple peak detectors                                  |    |

|     | distributed along a transmission line                                                                    | 60 |

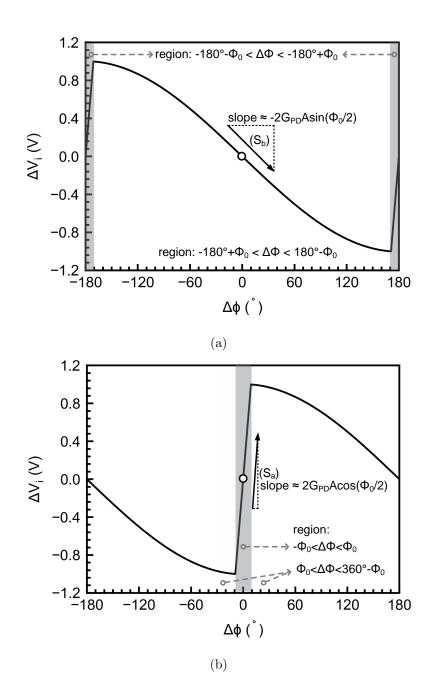

| 4.5 | Characteristic of the proposed phase detector: (a) The theoretical rela-                                 |    |

|     | tionship between $\Delta \phi$ and $\Delta V_i$ in the same-polarity scenario when $x_i = \frac{L}{2}$ . |    |

|     | (b) Theoretical relationship between $\Delta \phi$ and $\Delta V_i$ in the opposite-polarity             |    |

|     | scenario when $x_i = \frac{L}{2}$                                                                        | 62 |

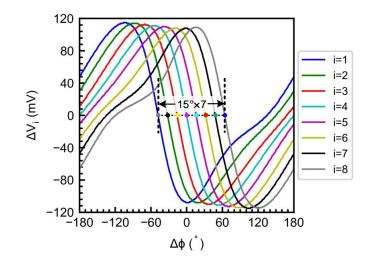

| 4.6 | The simulated $\Delta V_i$ as a function of $\Delta \phi$ with opposite polarity connection,             |    |

|     | where $i$ represents a specific pair of peak detectors                                                   | 63 |

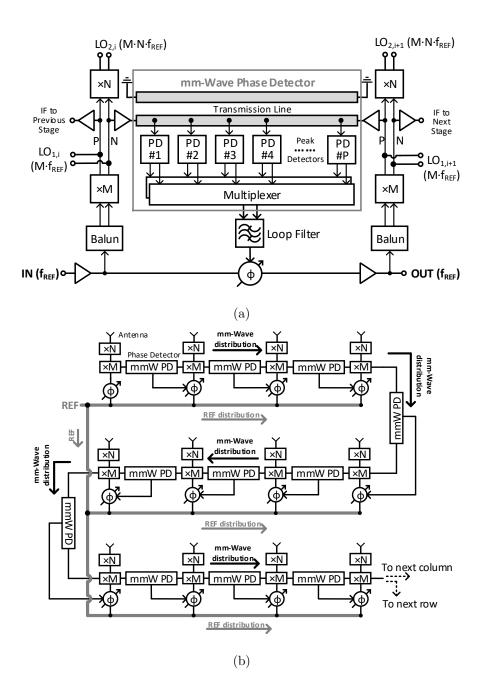

| 4.7 | (a) The architecture of a $1\times 2$ array with phase self-alignment. (b) A                             |    |

|     | scalable phased array based on this concept                                                              | 66 |

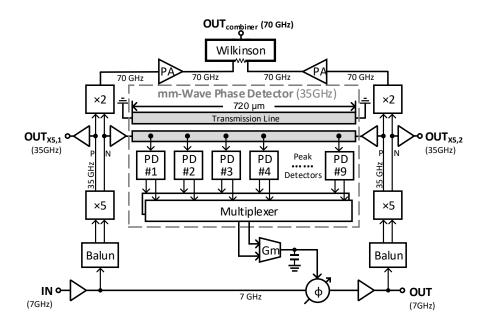

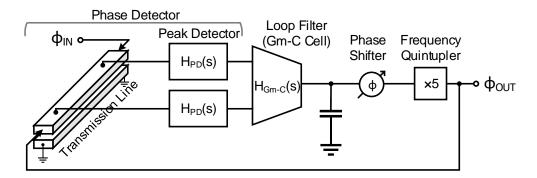

| 4.8 | Block diagram of the prototyped two-element array.                                                       | 69 |

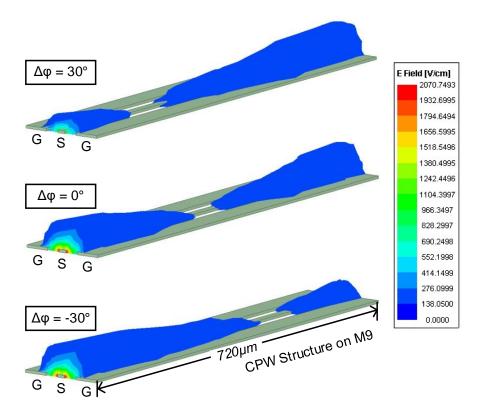

| 4.9 | EM simulation of the electric field distribution on the CPW line as a                                    |    |

|     | function of $\Delta \phi$ .                                                                              | 70 |

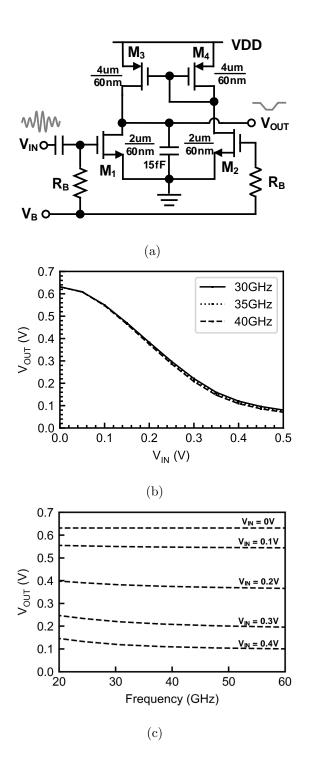

| 4.10 | (a) Schematic of the peak detector. (b) Simulated output voltage of the           |    |

|------|-----------------------------------------------------------------------------------|----|

|      | peak detector as a function of the input signal amplitude. (c) Simulated          |    |

|      | RF-to-DC response vs. frequency                                                   | 71 |

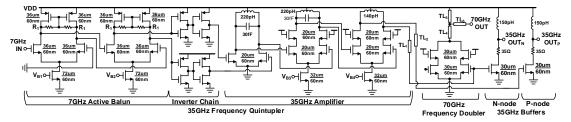

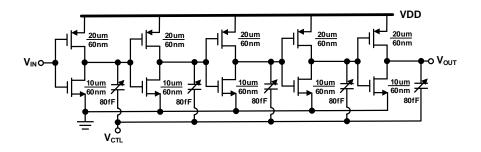

| 4.11 | Schematic of the frequency multiplier chain consisting of the active balun,       |    |

|      | the inverter chain, the 35GHz frequency quintupler, the 70GHz frequency           |    |

|      | doubler, and two 35GHz buffers                                                    | 72 |

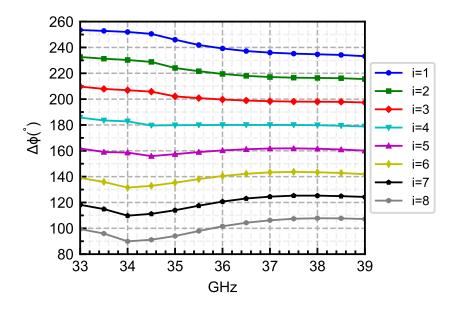

| 4.12 | Schematic of the phase-shifter.                                                   | 75 |

| 4.13 | Simulated phase differences between the left and right sources across             |    |

|      | frequency for different phase settings                                            | 76 |

| 4.14 | Linear model of the phase self-aligning feedback loop. $\ldots$                   | 77 |

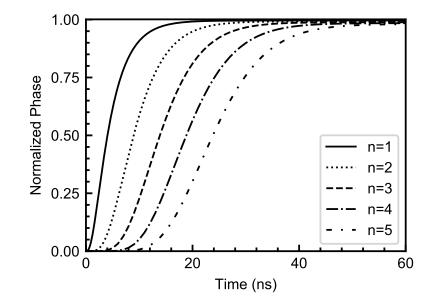

| 4.15 | Closed-loop step response for different number of stages, $n$                     | 79 |

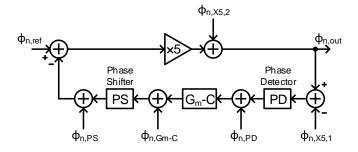

| 4.16 | Noise analysis model and the individual noise sources. $\ldots$ $\ldots$ $\ldots$ | 80 |

| 4.17 | Magnitude of the output noise transfer function at $OUT_{X5,2}$ , with respect    |    |

|      | to each sub cell                                                                  | 81 |

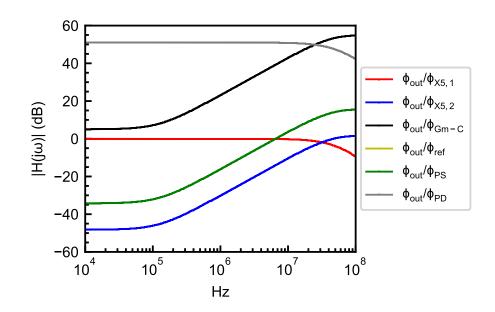

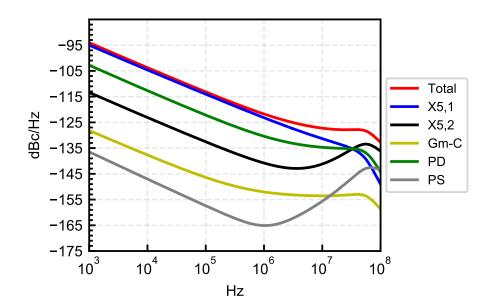

| 4.18 | Simulated closed-loop phase noise at $OUT_{X5,2}$ with individual sub cell        |    |

|      | noise contribution.                                                               | 81 |

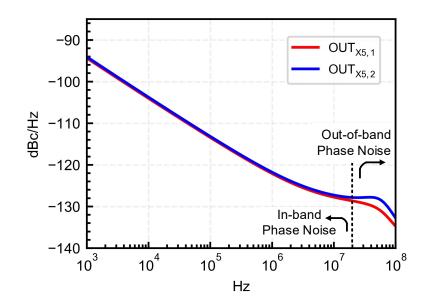

| 4.19 | Simulated closed-loop phase noise at $OUT_{X5,1}$ and $OUT_{X5,2}$                | 82 |

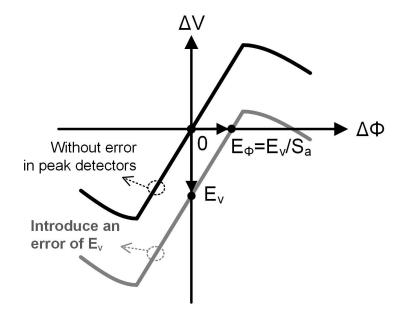

| 4.20 | Translation of mismatch from $E_v$ to $E_{\phi}$                                  | 83 |

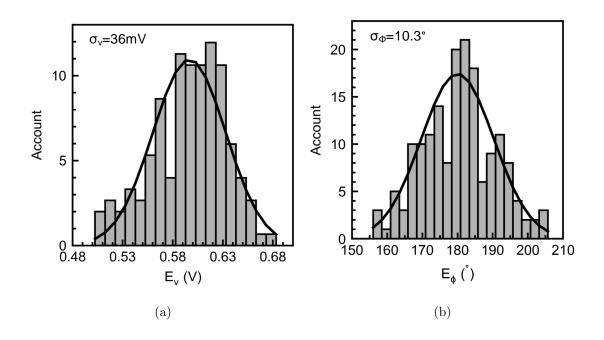

| 4.21 | (a) Monte Carlo simulation of the peak detector output when the input      |    |

|------|----------------------------------------------------------------------------|----|

|      | amplitude is chosen to represent the valley of the interference pattern.   |    |

|      | (b) System-level Monte Carlo simulation of the settled phase difference    |    |

|      | between the two sources                                                    | 84 |

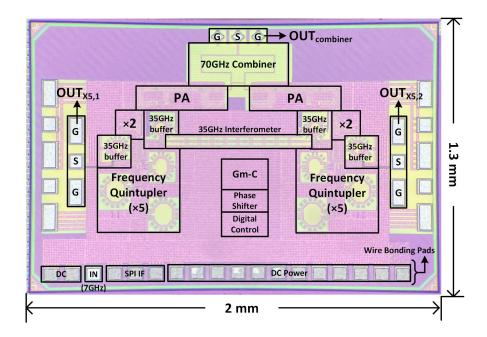

| 4.22 | Chip microphoto                                                            | 85 |

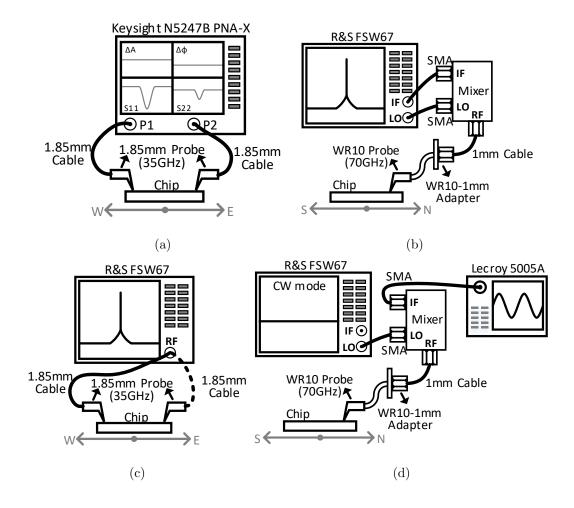

| 4.23 | Measurement setups for (a) phase and amplitude of the 35GHz out-           |    |

|      | puts, (b) the combiner output at 70GHz, (c) phase noise performance        |    |

|      | at 35GHz, and (d) transient response at the combiner output                | 86 |

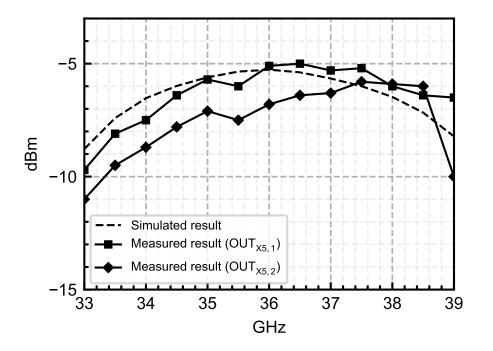

| 4.24 | Simulated and measured quintupler output power                             | 87 |

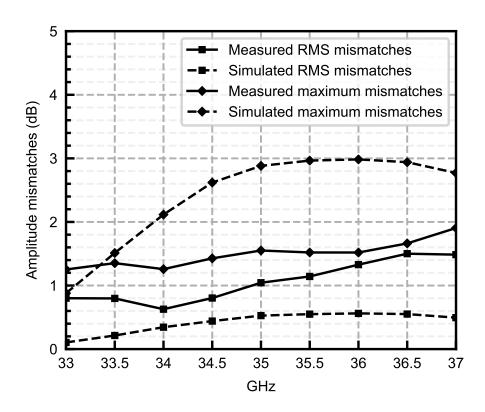

| 4.25 | Simulated vs. measured amplitude mismatch between two frequency            |    |

|      | quintuplers across frequency and phase settings.                           | 88 |

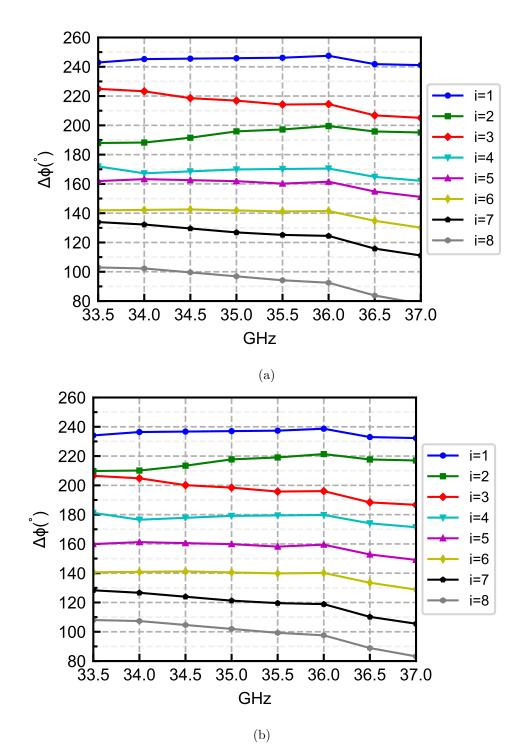

| 4.26 | (a) Measured phase difference between frequency quintuplers before the     |    |

|      | mismatch calibration. (b) Phase difference after the mismatch calibration. | 90 |

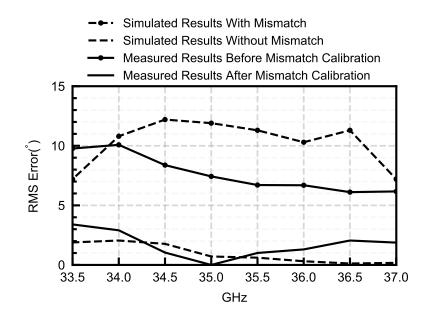

| 4.27 | Comparison between measured RMS phase error and results from Monte         |    |

|      | Carlo simulations.                                                         | 91 |

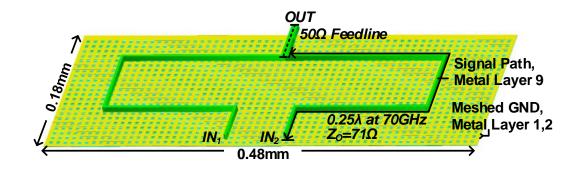

| 4.28 | The 70GHz Wilkinson power combiner. A $100\Omega$ resistor between port    |    |

|      | $\mathrm{IN}_1$ and $\mathrm{IN}_2$ is not shown in the figure             | 92 |

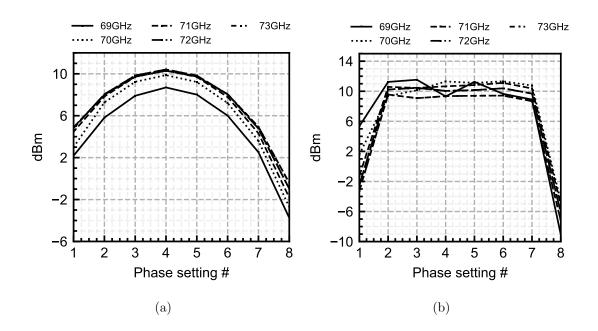

| 4.29 | (a) Simulated and (b) measured power at the output of the Wilkinson        |    |

|      | combiner                                                                   | 92 |

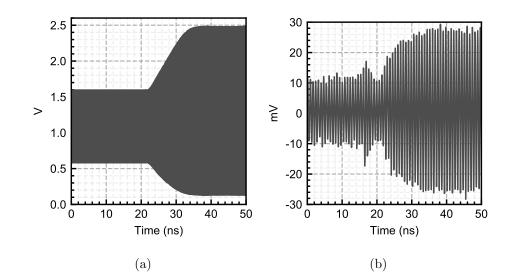

| 4.30 | (a) Simulated and (b) measured transient switching response at the com-    |    |

|      | biner output.                                                              | 93 |

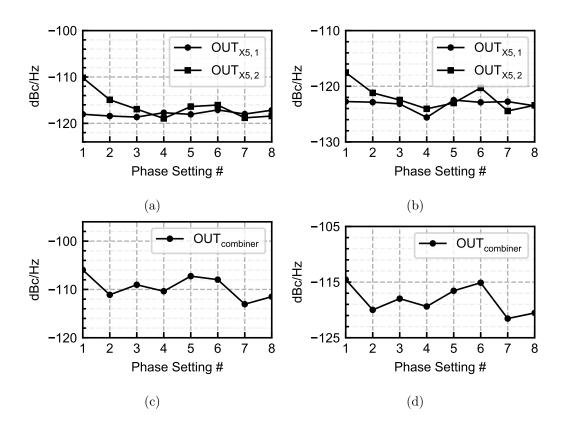

| 4.31 | Measured phase noise of the two 35GHz quintupler buffered outputs at                     |    |

|------|------------------------------------------------------------------------------------------|----|

|      | (a) 1MHz offset and (b) 10MHz offset. Measured phase noise of the                        |    |

|      | 70GHz Wilkinson combiner output at (c) 1MHz offset and (d) 10MHz                         |    |

|      | offset                                                                                   | 94 |

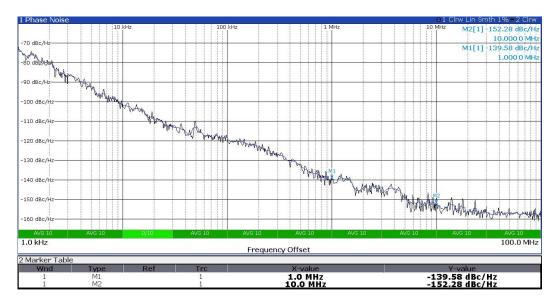

| 4.32 | Measured phase noise spectrum of the input reference signal. $\ldots$ .                  | 95 |

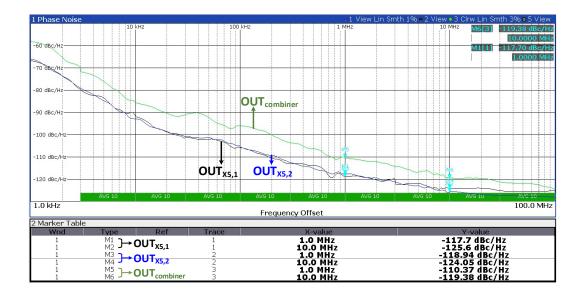

| 4.33 | Measured phase noise spectrum of the two $35 \text{GHz}$ outputs and the $70 \text{GHz}$ |    |

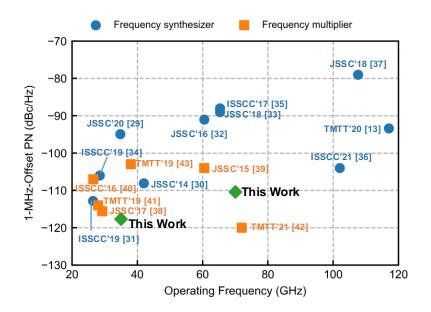

|      | output for the $i = 4$ phase setting                                                     | 95 |

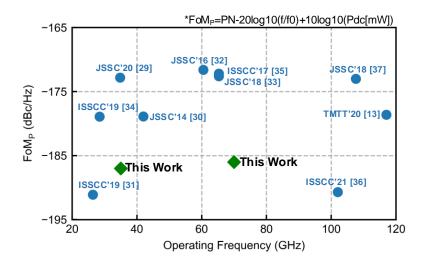

| 4.34 | Phase noise of the proposed signal source compared to state-of-art mm-                   |    |

|      | band signal generators                                                                   | 97 |

| 4.35 | FoM of the proposed signal source compared to state-of-art mm-band                       |    |

|      | signal generators.                                                                       | 98 |

## Chapter 1

# LO Distribution of Large-scale Phased Arrays

### 1.1 mmWave Phased Arrays and The Scaling Challenges

Millimeter waves band occupies the frequency spectrum from 30GHz to 300GHz. The mm-wave band integrated circuits are expected to have larger bandwidths, smaller components, better resolution and lower interference, than their radio counterparts that operate in the lower frequency band (K band and below) [1]. This has encouraged the development of new applications in wireless systems, including broadband newgeneration wireless communication, and high-resolution sensing and imaging. However, there are several limitations presented with radios operating at mm-wave frequencies. First, the signals generally suffer from higher atmospheric and molecular absorption at higher frequencies [2]. This means that there is a higher signal attenuation at mm-wave frequencies and shortening the transmission range in these bands, especially at the "attenuation peak" bands, like those at 60GHz and 120GHz. Secondly, as the mm-wave integrated circuits are moving closer to the trans-conductance cut-off frequency, performance of semiconductor components are limited in terms of power generation, which further limits the transmission range. In order to increase the radiating power, III-V compound devices could be used in integrated mmWave radios because of their superior power generation abilities, compared to silicon components [3, 4]. However, III-V compound devices are more expensive compared to silicon devices. Also, III-V devices have a relatively lower level of integration density, inferior yield and functionality compared to a silicon device with the same footprint [5]. Therefore, engineers continue to explore the potential of silicon-based mmWave system through circuit optimization and architecture innovation [6, 7, 8].

To improve the performance of mmWave communication systems, antenna array architectures, known as phased arrays, are used because they provide the ability to program the propagating beams in both power and direction through array scaling and beam steering, respectively [9]. During normal operation, phased arrays engage multiple antenna elements and maintain a tuned phase profile across the array. The antenna elements would radiate together and combine power coherently over the air at the beam angle. In other directions, the congregated power are at null due to phase interference from different elements. Besides higher output power, phased arrays also have a higher radiating efficiency compared to single radiators because the effective isotropically radiated power(EIRP) of N-element phased array is  $N^2 P_o$ , when each element outputs power level of  $P_o$ . It is N times higher than a single-antenna radiator that consumes the same amount of dc power [7]. Since increasing N awards higher EIRP and radiation efficiency, it is not surprising that there has been an increasing focus on the design of phased arrays with more and more antennas [10, 11, 12, 13, 14]. Silicon-based phased arrays at scale comes with extra points in low cost advantage and high integration features [15, 16, 17].

However, scaling the size of phase arrays raises challenges. Since the local oscillator (LO) signal quality is crucial to the performance of wireless communication systems, maintaining the LO spectrum purity and phase consistency across array are quintessential for advanced array system. The conventional H-tree LO distribution network is not suitable for large-scale phased array because of the following reason. First, such global distribution network need to sustain identical phase delay and amplitude attenuation across routes from the center LO to each element, indicating a increasing layout difficulty as array scales up. It is reasonable to assume that such a distribution network is likely to be implemented on several substrates including chips, packages and boards with complex interface like flip-chip bonds or bonding wires which are difficulty to model accurately at mm-wave frequencies.

Compared to the use of a single LO source and a global distribution network, LO system with multiple sources could be more suitable to develop large-scale phased arrays because it does not require a complicated global distribution network design. However, additional frequency and phase synchronization scheme are required to ensure a stable phase profile for coherent power combining over-the-air. For example, multiple phase-locked loops (PLLs) could coexist and form the top-level LO systems sharing the reference clock so that they are frequency locked to each other. However, the phase of each PLL would be in total random initially and would require additional calibration during the initialization process prior to the regular wireless communication sequences. However, since the phase profile are subject to any transient disturbance like the temperature drift in the active circuit blocks, such calibration would be a periodic requirement. The calibration process would require relatively long head-time periodically because frequency down-conversion are commonly involved in baseband calibration and each calibration practice would be time-consuming. Therefore, we identify the frequency and/or phase synchronization to be a critical challenge in the multi-LO system, placing a severe barrier ahead of scaling multi-LO array. The engineering solution to build large-scale mm-wave phased array demands innovations at fundamental level including array architectures and/or LO distribution schemes. Recently, people have proposed innovative multi-LO arrays based on coupled oscillator arrays (COA) [18, 7] and coupled PLL arrays (CPLLA) [19, 8]. However, more research works are still necessary in the topic of array scaling where new ideas are much welcomed because the reported prototypes so far haven't successfully demonstrated the scalability of the existing typologies (for example, arrays with >1000 elements).

In the following sections of this chapter, we will review several multi-LO array schemes including COA, CPLLA and an interferometry-based autonomous array.

## 1.2 Coupled Oscillator Array

Distributed LO network could compensate the signal loss along the mm-wave band signal paths [20]. To meet the requirement of power combing and beam steering during phased array operation, distributed LOs have to achieved frequency and phase synchronization. The injection locking feature of oscillators have been applied to build coupled oscillator array and achieve synchronization across elements [18, 21, 22, 23]. The phase dynamic analysis of the coupled oscillator arrays are necessary to predict the settled phase modes and the corresponded stability conditions, and it starts with understanding the basics of the injection locking.

The injection locking refers to the phenomenon that the oscillator frequency tend to be locked to an external signal source when the external source inject power to the oscillator. Several models are presented to analyze and predict the oscillator behavior under injection [22, 23, 24]. The well-accepted model proposed by Adler [24] describes the phase dynamics of the oscillator as:

$$\frac{d\theta}{dt} = \omega_0 + \frac{\omega_0}{2Q} \frac{A_{inj}}{A} \sin(\theta_{inj} - \theta).$$

(1.1)

A is the amplitude of oscillator under injection,  $A_{inj}$  is the amplitude of the injected signal,  $\theta$  is the instantaneous phase of oscillator,  $\theta_{inj}$  is the phase of the injected signal,  $\omega_0$  is the transient frequency of the free-running oscillator, Q is the quality factor of the oscillator. If the oscillator is injection locked to the external source, we will have  $\frac{d\theta}{dt} = \omega_{inj}$ , where  $\omega_{inj}$  is frequency of the injecting signal. This means that the second terms on the right hand side of the equation in (1.1) should equal to  $\omega_{inj} - \omega_0$ . Therefore, the range limit on the circuit parameters and Sine function defines a finite range of the injecting frequency that the injected oscillator could be locked to. The locking range is:

$$|\omega_{inj} - \omega_0| \le \frac{\omega_0}{2Q} \frac{A_{inj}}{A}.$$

(1.2)

Using vector summation method, we can extend the equation (1.1) to represent the multiple sources injection conditions in equation (1.3).

$$\frac{d\theta}{dt} = \omega_0 - \frac{\omega_0}{2Q} \sum_{j=1}^N \epsilon_j \frac{A_{inj,j}}{A} \sin(\Phi_j + \theta - \theta_{inj,j}).$$

(1.3)

In a coupled N-oscillator array, each oscillator could be injected by the rest N-1 oscillators. The phase relationships could be represented in the form of Adler's equations:

$$\frac{d\theta_i}{dt} = \omega_i - \frac{\omega_i}{2Q} \sum_{j=1}^{N-1} \epsilon_{ij} \frac{A_j}{A_i} \sin(\Phi_{ij} + \theta_i - \theta_j)$$

$$i = 1, 2, ..., N.$$

(1.4)

$\epsilon_{ij}$  represents the coupling coefficient from  $j^{th}$  oscillator to  $i^{th}$  oscillator.

Equation (1.4) describes a general model and have been used to study COAs of different structures which we assort into two categories: (1) bilateral coupled- and (2) unidirectional coupled- oscillator arrays. The first coupling method, first proposed in 1990s [22], is the conventional method to build COA. Many works have studied the phase dynamics and stability conditions for LO generation in beamforming applications [20, 22, 23]. However, there is a known feature of bilateral COAs that the probability of locking for one- and two- dimensional arrays with randomly distributed frequencies will drop to zero as the number of oscillators increases [22]. To ensure that a COA of N element would be frequency locked, the coupling strength must increase at the rate of  $\sqrt{N}$  [25]. As a result, the bilateral COA is not suitable for scalable phased arrays because the coupling strength is within a finite range. The second coupling method is a relative new scheme with a few reports with mmWave beamformer prototypes [7, 18]. More theoretical works on the unilateral COA are required to have a deeper understand about its potential in LO scheme for phased arrays at scale.

## 1.3 Coupled PLL Array

PLL uses a feedback loop to force a targeted oscillator to track the frequency of a reference signal. The loop operation results in a fixed phase difference between the oscillator and the reference signal. The settled phase difference could be further controlled by adding a DC offset voltage into the loop [26]. The phase tracking and tuning feature of this control method could be used to couple multiple PLLs together and form beamsteering active oscillator arrays. Fig. 1.1 shows a diagram of a CPLLA for a  $1 \times 2$  array. Here a mixer is served as phase detector which determines the sinusoidal relationship between phase difference and control voltage [26]:

Figure 1.1: PLL applied to a  $1 \times 2$  oscillator array.

$$\phi = \sin^{-1}\left(\frac{V_{tune} + V_{offset}}{K_{\phi}}\right) \tag{1.5}$$

where  $\phi$  is the phase difference between two antennas and  $K_{\phi}$  represents mixer's gain. Equation (1.5) also indicates that the PLL can generate a phase difference between antennas within range from  $-90^{\circ}$  to  $+90^{\circ}$ . There are more works of the CPLLA including [27, 28, 29, 19]. There are two limitations in this type of CPLLA. First, to the best of the author's knowledge, the reported arrays could only be scaled in one dimension using daisy-chain topology. New coupling techniques are needed to scale CPLLA in two dimensions. Second, the array structure shown in the Fig. 1.1 uses unit PLL element with finite loop gain [30]. The finite loop gain comes with the advantage of tunable settled phase by controlling  $V_{offset}$ , however, it also translates mismatches of oscillator free-running frequencies to phase errors between array elements.

PLL with infinite loop gain such as type-II PLL could be used as LO elements in CPLLA as well. Type-II PLL consists of frequency/phase detectors, charge pump, loop filter, voltage-controlled oscillator and frequency divider chain. The open-loop transfer function of type-II PLL has infinite loop gain at DC [30]. When the CPLLA uses type-II PLL as unit elements, the mismatches in oscillator free-running frequencies won't be transferred to phase errors. However, new coupling topology is required in order to build CPLLA in two dimensional because the reported prototypes are mainly limited to one-dimensional topology [19].

#### 1.4 Drawbacks in Conventional mmWave Phase Control

In the conventional mmWave signal generation and phase control method, the mm-wave LO signal is generated and controlled through a PLL. In this scheme, a voltage-controlled oscillator (VCO) generates the mm-wave signal. At the same time, a phase detector compares the phase of the VCO with an input reference clock by indicating whether the source is leading or lagging behind the reference. Subsequently, the output of the phase detector connects to a loop filter which adjusts the control voltage of the VCO until the phase is locked. The phase detector is typically based on flip flops and digital gates so a frequency divider chain is necessary to down-convert the VCO frequency to the input reference [30].

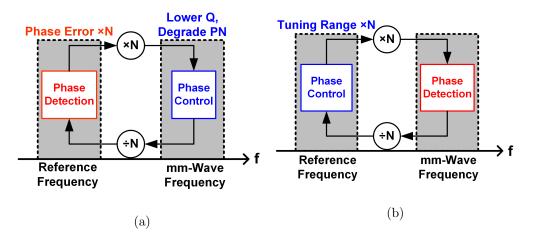

The typical VCO is tunable using analog varactors and/or digitally controlled capacitor banks placed inside the LC resonator. Hence as shown in Fig. 1.2a, the PLL control loop consists of two main sections: (1) phase detection and comparison at the reference frequency, and (2) phase control that applies to the mm-wave source. While such

Figure 1.2: Two schemes for mm-wave signal generation: (a) The conventional scheme detects phase at the reference frequency and controls it at the mm-wave frequency.(b) The scheme proposed in chapter four detects phase at the mm-wave frequency and controls it at the reference frequency.

topology has been widely adopted in RF frequency generation, it is limited by underlying weaknesses when applied to mm-wave multi-source generation and synchronization. First, tuning the frequency and phase of a mm-wave oscillator involves tunable analog varactors or switch-based components in the resonator. At mm-wave frequencies, the varactor would dominate the quality factor of the LC tank and limit the phase noise and power efficiency [31]. The use of capacitor banks of metal-insulator capacitors alleviates this issue to some extent. However, even using this technique, the limited quality factor of the capacitor and switch eventually leads to the same degradation in the resonator and limits the frequency of operation [32]. As result, many recent high-frequency synthesizers have turned toward frequency multiplication to scale up the output frequency [33]. However, such methods provide no control over the phase of the signal. The second issue with the traditional loop topology is that the phase detector operates at the low frequency of the reference signal. Therefore, any phase error inside the control loop is multiplied by the frequency division factor when examining the output of the VCO. As a result, the oscillator phasor would be locked to the reference signal but with a significant and unpredictable phase error. Sub-sampling PLLs can overcome this phase error multiplication issue within a single source [34]. However, in a multi-source array scenario, this architecture is still blind to random phase variation between adjacent elements.

Based on this discussion, we believe in Fig. 1.2b presents a scheme that is fundamentally more suitable for signal generation and synchronization at mm-wave and THz frequencies. In this scheme, we detect the phase at the target mm-wave frequency while phase control occurs at the lower frequency of the input reference. By effectively switching the location of detection and control we simultaneously avoid both above challenges: First, by controlling phase at the reference frequency, we avoid direct control of the resonator resulting in optimal frequency and spectral purity. Second, by directly measuring the phase at the mm-wave band, we prevent phase ambiguity and enable accurate phase alignment.

The rest of the thesis is organized as follows: In chapter two, we propose a scalable COA scheme based on unidirectional coupling method [35]. As a theoretical work, we analytically derive the stable modes for the scaled COA and demonstrate that the coupling behaviour is stable and predictable regardless of the array dimension. In order to study the stability of the proposed array, we analyze the transient dynamics and the scalability of the structure in the presence of element-to-element variations. We believe the proposed scheme is a promising LO solution for large scale phased arrays.

In chapter three, we propose a two-dimensional CPLLA scheme using type-II PLLs as LO elements. We present the concept of phase locking between multiple oscillators and present a chip prototype of the PLL array at 28GHz. The measurements verify that out-of-band phase noise of the distributed array does not depend on the number of elements in the array. The measured results indicate that there are several limitations of the proposed scheme, including in-band phase noise degradation and stability issue. Through post-tape-out investigation, we find the underlying reason is due to the conflicting between the PLL phase control and magnetic injection coupling.

In chapter four, we use the method of mm-wave signal generation and distribution based on the topology shown in Fig. 1.2b [36]. We demonstrate the concept with a chip prototype showing accurate phase control and a fast switching time with high spectral purity. The presented element-to-element self-alignment method is applicable for distributed tuning and control of scalable phased arrays without the need of extensive baseband calibration.

Finally, we summarize the three projects in chapter five. In addition, we discuss about the future works in the author's perspective and mention two directions for the following up research. Chapter 2

# Scalable Oscillator Array Using Unilateral Coupling

### 2.1 Introduction

There is an increasing demand for high-speed wireless communication based on Siliconbased radio front-ends with mm-wave and sub-mm-wave carrier frequencies [10, 37, 38, 39]. At these frequency bands, however, a single-antenna front-end would inevitably suffer from limited output power and propagation loss. In order to achieve practical power levels, RF engineers commonly employ phased arrays to coherently combine power from many individual sources and radiators, and there is an effort to significantly increase the number of elements in such an array [40, 20].

There are several challenges that limit very large scale arrays particularly at mmwave frequencies. One of the fundamental limits is to achieve even distribution of the RF or LO signal across many elements [41]. The increasing loss and inter-element coupling places a crucial limit on global distribution of such high frequency signals. Coupled oscillator arrays have been introduced as an alternative to this traditional distribution [23]. The idea behind this approach is that instead of only having a single source, each element has its own local oscillator (LO). As a result, the new array would have multiple LOs synchronized by the coupling network. This new scheme promises two main benefits: first, the synchronization network only relies of adjusting local coupling between neighboring element resulting in seamless scaling of the network. Second, the coherent combining of many independent oscillators, can increase the purity of the signal source far beyond what is achievable with a single source [28, 19].

Recent work has shown that such a coupled oscillator array can operate at small

Figure 2.1: The diagram of ring made of four unilateral coupled oscillators.

number of elements [42]. Tousi presents the phase dynamics analysis of a  $2\times 2$  array using active unidirectional coupling between adjacent elements [6], as shown in Fig. 2.1. Later, he presents a  $4\times 4$  beamformer constructed upon the previous  $2\times 2$  unit blocks, and promotes a scalable scheme for phased arrays [7]. In order to have insight of this scaling scheme, more investigations on the scaled arrays are needed regarding phase dynamics and stability conditions. In this chapter, we analyze the scaling arrays using the  $2\times 2$  array as cell block, and propose a general theoretical framework as a method to scale the coupled-oscillator array.

The rest of this chapter is organized as follows: Section 2.2 starts with a case study, analyze the equilibrium modes of the example array. The stability analysis of the case study is continued and carried out in Section 2.3. Section 2.4 extents the conclusion drawn from the case study to the general condition. We will demonstrate that the array

Figure 2.2: The diagram of the example array made of two ring array sharing one oscillator at the vertex.

could be scaled without compromising the stability. This chapter is concluded with a discussion of the settling dynamics and resilience to variation of the scaled arrays.

## 2.2 Steady-state Analysis: A Case Study

Based on the prior study [6], we know that a  $2 \times 2$  array as shown in Fig.2.1 only has four fundamental modes  $\psi = k\pi/2$ , k = 0, 1, 2, 3 where  $\psi$  is the phase difference between adjacent oscillators. In order to expand the array we propose to use this four-oscillator ring as a unit block and construct larger arrays by connecting the rings through a common vertex which we call the "shared-vertex" technique. This is contrast to sharing a common edge between two unit blocks and we shall see how this technique is beneficial in scaling up the size of coupled oscillators. Fig. 2.2 shows the smallest-expanded array by connecting two unit rings at a common oscillator. In this scheme, oscillator 2 is the common vertex and receives dual injection from both loops while all other oscillators only receive a single injection. As a result, in order to balance the coupling intensity across all elements, the intensity of injection to the shared oscillator is half compared to regular elements. To analyze the dynamics, we define the phase of the  $i^{th}$  oscillator as  $\phi_i$ , i = 1, 2, ..., 7 and the phase difference between adjacent oscillators as  $\psi_i$ . Based on Adler's equation [24], we derive the phase dynamics of the array elements as:

$$\dot{\psi}_{1} = \frac{K}{2}\sin(\psi_{2}+\theta) + \frac{K}{2}\sin(\psi_{8}+\theta) - K\sin(\psi_{1}+\theta)$$

$$\dot{\psi}_{2} = K\sin(\psi_{3}+\theta) - \frac{K}{2}\sin(\psi_{2}+\theta) - \frac{K}{2}\sin(\psi_{8}+\theta)$$

$$\dot{\psi}_{3} = K\sin(\psi_{4}+\theta) - K\sin(\psi_{3}+\theta)$$

$$\dot{\psi}_{4} = K\sin(\psi_{1}+\theta) - K\sin(\psi_{4}+\theta)$$

$$\dot{\psi}_{5} = \frac{K}{2}\sin(\psi_{2}+\theta) + \frac{K}{2}\sin(\psi_{8}+\theta) - K\sin(\psi_{5}+\theta)$$

$$\dot{\psi}_{6} = K\sin(\psi_{5}+\theta) - K\sin(\psi_{6}+\theta)$$

$$\dot{\psi}_{7} = K\sin(\psi_{6}+\theta) - K\sin(\psi_{7}+\theta)$$

$$\dot{\psi}_{8} = K\sin(\psi_{7}+\theta) - \frac{K}{2}\sin(\psi_{8}+\theta) - \frac{K}{2}\sin(\psi_{2}+\theta), \qquad (2.1)$$

where  $\theta$  is the extra phase delay from the phase shifter, and K is the intensity of the injection to the oscillator.

Furthermore, we apply the following boundary conditions based on the phase consistency:

$$\psi_1 + \psi_2 + \psi_3 + \psi_4 = 2m\pi, \qquad m = 1, 2, \dots$$

$\psi_5 + \psi_6 + \psi_7 + \psi_8 = 2n\pi, \qquad n = 1, 2, \dots$  (2.2)

The system arrives at the steady state when  $\dot{\psi}_i = 0$ , for i = 1, 2, ..., 8. This equilibrium solution,  $\psi_i^0$ , represents a constant phase difference between oscillators because every oscillators operates at the same frequency if the array settles successfully. By applying the steady state condition to (2.1), we arrive at the following relations:

$$\sin(\psi_1^0 + \theta) = \sin(\psi_j^0 + \theta), \quad j \in \{3, 4, 5, 6, 7\},$$

(2.3a)

$$\sin(\psi_1^0 + \theta) = \frac{1}{2}\sin(\psi_2^0 + \theta) + \frac{1}{2}\sin(\psi_8^0 + \theta).$$

(2.3b)

The solution of (2.3a),  $\psi_j^0$  can be either  $\psi_j^0 = \psi_1^0$  or  $\psi_j^0 = \pi - \psi_1^0 - 2\theta$ . This ends up in  $2^5 = 32$  possible results as the solution of (2.3). Considering all 32 conditions for both (2.2) and (2.3) and solve them one by one, we find out that  $\psi_1^0$  could be one of the following values:

$$\psi_1^0 \in \{\frac{k\pi}{2}, \ \theta \pm \frac{\pi}{2}, \ -\theta \pm k\pi, \ -3\theta + \frac{\pi}{2} \pm k\pi\}, \ k = 0, 1, 2, 3.$$

(2.4)

This includes every possible equilibrium states of the phase difference  $\psi_1^0$ . Once  $\psi_1^0$  is known, we can easily find out the phase differences of the rest oscillator pairs as  $\psi_j^0, j = 2, 3, ..., 8$ . As the next step, we look into the stability of these steady-state conditions.

### 2.3 Stability Analysis: A Case Study

In order to find out the physically realizable modes, we use the perturbation method [43] to analyze the stability of solutions listed in (2.4). Using this method, we can tell whether a steady state solution is stable by inspecting whether perturbations around it would decay over time. Equation (2.1) consists of multiple nonlinear differential equations, however, in order to manage the complexity of the following analysis, we use the first order linear approximation of the equation sets and introduce perturbations to the steady state solution,  $\psi_i^0$ .

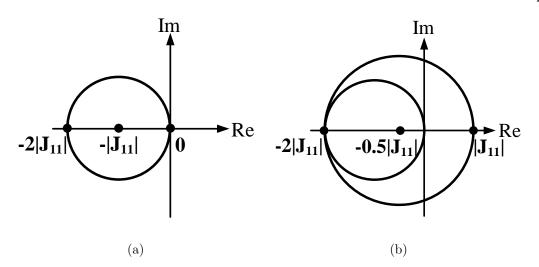

We define  $\boldsymbol{\psi} = [\psi_1^0 \dots \psi_8^0]^T$  and rewrite (2.1) as  $\boldsymbol{\dot{\psi}} = J\boldsymbol{\psi}$ , where J is the Jacobian matrix. To ensure the decay of any perturbation, the real part of all eigenvalues in J have to be non-positive [44]. Prior study has successfully employed Gershgorin theorem to study the eigenvalues of a four-oscillator ring structure using unidirectional coupling between neighbor elements and identify its four stable modes [6]. According to the Gershgorin theorem, eigenvalues should be inside a set of Gershgorin circles in the complex plane [43]. Here we first approach the stability inquiry of our case study with a similar method.

As shown in Fig. 2.3a, the four-element ring structure has all of its eigenvalues residing in a circle on the left hand side of the imaginary axis. This distribution of the eigenvalues indicates that the each corresponded steady state solution would be stable. However, as shown in Fig. 2.3b, when plotting the distribution of the eigenvalues of the two-ring system, these circles contain both positive and negative real values. As a result,

Figure 2.3: Gershgorin circles and the distribution of eigenvalues for (a) four-oscillator ring and (b) two-ring array.

the eigenvalue signs of a two-ring system are still uncertain following the same analytical process of the previous single-ring case. Therefore, we choose to directly compute the eigenvalues associated with each solution in (2.4) and examine the stability one by one.

The modes corresponding to  $\psi_i^0 = k\pi/2$ , lead to the following eigenvalues:

$$\lambda_1 = \lambda_2 = \lambda_3 = \frac{\lambda_4}{2} = -Ka_1$$

$$\lambda_5 = \lambda_6 = -Ka_1(1-i)$$

$$\lambda_7 = \lambda_8 = 0,$$

(2.5)

where  $a_1 = \cos(k\pi/2 + \theta)$ . Since K is positive, in this mode, all  $\lambda_i$ 's are non-positive for  $a_1 > 0$ . Hence the equilibrium solution  $\psi_1^0 = k\pi/2$ , is stable when:

$$-\frac{\pi}{2} - \frac{k}{2}\pi + 2n\pi < \theta < \frac{\pi}{2} - \frac{k}{2}\pi + 2n\pi.$$

(2.6)

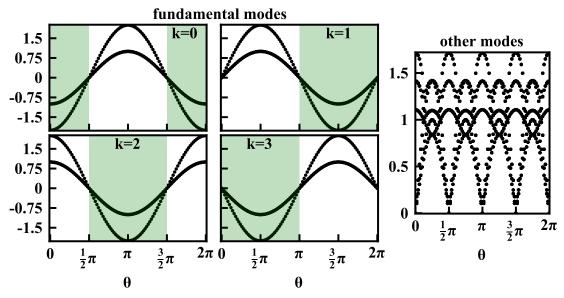

Figure 2.4: All non-zero  $\operatorname{Re}\{\lambda\}$  for the two-ring array across different modes of operation. The shaded areas represent stable regions.

Fig. 2.4 shows all of the non-zero Re{ $\lambda$ } for each mode of  $\psi_i^0 = k\pi/2$ , k = 0, 1, 2, 3, and green rectangular areas denote stable regions with respect to  $\theta$ .

Beside  $\psi_i^0 = k\pi/2$ , we also investigate the rest of the solutions corresponding to other values in (2.4). These solutions turn out to be unstable as they always contain a positive eigenvalue. The right figure in Fig. 2.4 shows max(Re( $\lambda_i$ )) for each of these equilibrium solutions. This demonstrates that there is always at least one positive eigenvalue, hence none of these modes are stable. This means that the fundamental modes are the only stable modes of the two-ring array. It is worth mentioning that the stability condition in (2.6) is identical to the stable solutions derived for the single ring structure in [18]. This demonstrates the benefit of shared-vertex expansion of the single loop which maintains the fundamental stable coupling modes without adding extra modes.

#### 2.4 Scalable Array Analysis: The General Model

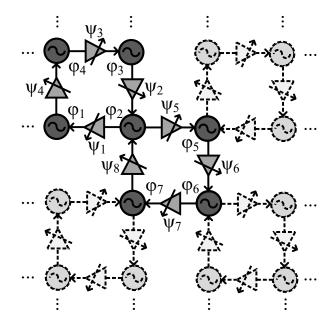

In this section we analyze the stable modes of operation as we further scale the array using the shared-vertex technique. Fig. 2.5 shows the proposed scaling scheme with an example of a  $4 \times 4$  array. For the general array we observe that there are three distinct types of connections. If we name the oscillator with two injected paths as the "center" and regular oscillators as "vertex" there are: (1) the center-to-center connection, (2) the vertex-to-center connection and (3) the vertex-to-vertex connection. Next, we derive the stable modes as a result of these three different connections.

#### 2.4.1 Analysis of steady-state modes

In Fig. 2.5, we can use the connection between oscillators 2 and 5 as an example of a center-to-center connection with the following dynamical equation:

$$\dot{\psi}_{5} = \frac{K}{2}\sin(\psi_{2} + \theta) + \frac{K}{2}\sin(\psi_{8} + \theta) - \frac{K}{2}\sin(\psi_{5} + \theta) - \frac{K}{2}\sin(\psi_{9} + \theta).$$

(2.7)

Similarly, we use the connection between oscillator 3 and 2 as an example of the vertexto-center connection:

$$\dot{\psi}_2 = K\sin(\psi_3 + \theta) - \frac{K}{2}\sin(\psi_2 + \theta) - \frac{K}{2}\sin(\psi_8 + \theta).$$

(2.8)

Figure 2.5: Proposed scheme for expanding the coupled array structure. The dimensions scale using the shared-vertex technique.

Finally, the connection between oscillator 4 and 3 is an example of the vertex-to-center connection:

$$\dot{\psi}_3 = K\sin(\psi_4 + \theta) - K\sin(\psi_3 + \theta). \tag{2.9}$$

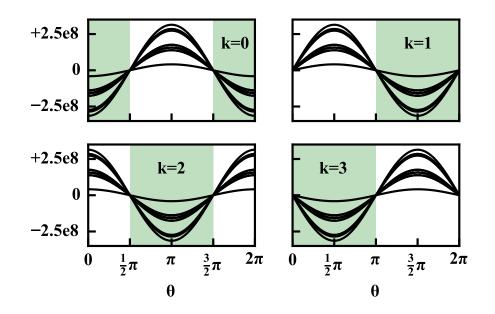

When  $\psi_i = k\pi/2$ , the right hand side of the above three types of equations is zero. This is true regardless of the size of the array. Hence the fundamental modes derived in section II permeates throughout the expanded array. To ensure the stability of these fundamental modes in the expanded array, we test  $\text{Re}\{\lambda\}$  across  $\theta$  for different array sizes. Next, we exam the stability of equilibrium of the expanded array similarly as the previous section. For instance, Fig. 2.6 demonstrates the distribution of all nonzero  $\text{Re}\{\lambda\}$  for an  $4 \times 4$  array. We verify the stability of these modes up to a  $16 \times 16$ array. Verifying this for larger arrays becomes computationally prohibitive, however we anticipate this conclusion to hold for any array size.

#### 2.4.2 Transient Simulation

In this section we study the array dynamics, its transient behaviour, and synchronization in the presence of physical imperfections in a scaled array. Without losing generality<sup>1</sup> we use the following circuit parameters in simulations: Free running frequency  $f_0 =$ 50GHz, Q = 20, and injection intensity  $(I_{inj}/I_{core}) = 2\%^2$ .

<sup>&</sup>lt;sup>1</sup> The choice of specific numerical values does not affect the conclusions in the work.

<sup>&</sup>lt;sup>2</sup> The assumption for modeling injection-locked oscillators with Adler's equation is that the coupling strength is weak, i.e.,  $I_{inj} \ll I_{core}$ .

Figure 2.6: All non-zero  $\operatorname{Re}\{\lambda\}$  for the 4×4 array across different modes of operation. The shaded areas in green color represent stable regions.

#### Stable modes and settling speed

To study the stable modes we start all oscillators from random initial phases. Fig. 2.7 shows the settling possibilities of the four fundamental modes across large volume repetitive tests. The density of each fundamental mode agrees with the stable regions predicted in (2.6).

According to nonlinear theory [45], the eigenvalues appear at the exponential part of the transient trajectories, so each real part of all non-zero eigenvalues is inversely proportional to the time constant of a transient mode. Therefore the minimum value of all non-zero real parts determines the dominant(largest) time constant which predicts the settling speed of the array. For this reason, we use  $\min(||\operatorname{Re}\{\lambda\}||)$  as an indicator

Figure 2.7: Probability density distribution associated with four fundamental stable modes ( $\psi_i^0 = k\pi/2$ , k = 0, 1, 2, 3) in the 4×4 array. For each  $\theta$ , we run 500 iterations with random initial phases to get the statistical result.

Figure 2.8: Array time constant derived from  $\min(||\operatorname{Re}\{\lambda\}||)$ . Each plot represents a particular array size.

of settling speed and compare it between different array sizes. As Fig. 2.8 shows, this  $\min(||\operatorname{Re}\{\lambda\}||)$  decreases as the size of the array scales which indicates that a larger array needs a longer time to settle. We can observe this transient behaviour in Fig. 2.9.

Furthermore, in a given array size, (2.5) indicates that the settling speed is a function of the coupling coefficient K and the active phase delay  $\theta$ . As a result, it is possible to reduce the settling time by temporarily reducing the Q of the oscillator or increasing the injection current [24].

Figure 2.9: Transient response of individual elements when the coupled array is settling to  $\psi = 0$ .

#### Resilience to element-to-element variation

Physical variations including PVT introduce random and systematic drifts across arrays in two places: oscillator free-running frequency  $f_0$  and injection intensity K. In this work, we focus on the  $f_0$  mismatch since it would disrupt frequency synchronization in the coupled array when such mismatch exceeds the maximum locking range. The K mismatch is outside the scope of this thesis which requires future work to further study its effect.

For passive coupled oscillators, Strogatz shows that in order to maintain synchronization for an N-element structure, coupling strength should increase proportional to  $\sqrt{N}$  [25]. This imposes a practical limit on such a coupled array [22].

However, in an actively coupled array, due to the modular structure of the network we anticipate a better resilience to random variation. This is because in the sharedvertex technique, as long as the sub-arrays are synchronized, we can expect the combined structure to operate in the same stable mode as the sub-arrays. According to Adler's equation the smallest block is guaranteed to synchronize as long as the frequency difference is within the maximum locking range, i.e.  $\pm \frac{K}{2}$ . As a result, even a much larger array should synchronize as long as all its elements are within this range.

To verify this we perform statistical transient simulation by randomly varying the center frequency of array elements. In this simulation, the frequency drift is a uniform random variable with bounds of  $\pm \alpha K$ . Fig. 2.10 shows the probability of synchronization as a function of  $\alpha$  for different sizes of the array. This simulation verifies that 1)

Figure 2.10: Probability of synchronization in the presence of element-to-element variation in the array.  $\alpha$  represents random frequency variation relative to the locking bandwidth. For each array size, we run 500 iterations with random initial phases at a fixed  $\theta$  ( $\theta = 0$ ) to get the statistical result.

for  $\alpha \geq 0.5$ , the probability of synchronization in the combined array is smaller than the sub-arrays, as for the combined array to operate, all sub-arrays need to synchronize concurrently, and 2) for  $\alpha < 0.5$ , the array is synchronized regardless of the size. As a result, this proposed array guarantees synchronization for any array size as long as all variations are within  $\pm \frac{K}{2}$ .

Besides PVT variances in  $f_0$  and K, other practical issues exist such as undesired

inter-coupling and across-chip interference. As a result, for future realistic hardware implementation, we need to co-design the chip-package solution, extract the high-frequency EM model, and incorporate the extra delays due to interconnects both on-chip and offchip within the coupling model.

#### 2.5 Summary

In this chapter, we present a novel technique for expanding the size of an array of actively coupled oscillators. We analytically derive the stable modes for an expanded network and demonstrate that the coupling behaviour is stable and predictable in a deliberately large array. Furthermore, we analyze transient dynamics and the scalability of the structure in the presence of element-to-element variations. We offer a promising solution for large scale signal distribution in phased arrays.

## Chapter 3

# **Coupled PLL Array**

#### 3.1 Introduction

The growing interest in millimeter-wave phased arrays and massive MIMO, both part of the new wave of radios in 5G demand the deployment of large arrays for transmitters and receivers. Spatial diversity and multiplexing becomes effective when the number of elements in such arrays can scale to large numbers. While this is desirable, such benefits would only grow by size as long as the individual elements and their front end radios maintain their performance throughout this scaling. One of the most crucial components of both the transmitter and receiver with critical effect on overall system performance is the reference frequency, i.e. the LO. It is fundamentally difficult to share LO with a large number of elements without an inevitable degradation of the quality of the signal. This is a challenge that deepens as the number of elements and the physical dimensions of the system increase [42]. The challenge of LO network design in mmwave frequencies is two-fold: 1) creating low noise sources at higher frequencies and 2) distributing the source throughout the array with minimal degradation. Recently there is an increasing interest in developing mm-wave LO designs with focus on enhancing the phase noise of the source [46]. However, the challenge of LO distribution remains a major issue.

In the previous chapter, we approach this challenge by employing the injection locking of oscillators and propose a scalable COA scheme. We demonstrate that the COA could achieve frequency synchronization automatically despite of certain level of mismatches in oscillator free-running frequencies. However, the frequency calibration is still necessary in order to eliminate settled phase errors coming from frequency mismatches. Therefore, we would like to investigate alternative coupling methods for both frequency and phase synchronization. Besides injection-locked oscillators, prior studies have considered coupled PLL arrays (CPLLA) as an alternative solution to build scalable arrays as well [27, 28, 29, 19]. Those works commonly use type-I PLL as array element. Type-I PLL consists of phase detector, loop filter, voltage-control oscillator and frequency divider [30]. The open-loop transfer function of type-I PLL has finite gain at DC. Because of this finite loop gain, there is a monotonic relationship between the oscillator frequency and the phase difference between divided oscillator output and the reference. When multiple PLLs are connected in series and form a one-dimensional CPLLA, tuning the oscillator free-running frequency changes the phase difference between adjacent oscillators in the chain. Although this type of CPLLA has desirable phase-tuning feature for beamformers, it has the following drawback. The frequency mismatch between oscillators from process, voltage and temperature (PVT) variance will be translated to phase error. In the presence of mismatch between different array elements, it can be shown that first order locking can compensate frequency mismatch but only at the expense of considerable phase mismatch between the elements.

In this chapter, we address this drawback from finite loop gain by employing type-II PLL as the array element due to its infinite dc loop gain. We propose a distributed phase locking mechanism where each PLL synchronizes with one of its nearest neighbors, alleviating the need to use a common reference. We introduce an architecture that 1) enables synchronization of frequency and phase locking at the presence of such non-idealities and 2) provides 2-dimensional scaling of the distributed PLL. The rest of the chapter is organized as follows: Section 3.2 presents the theoretical foundation of the proposed distributed PLL concept. Section 3.3 presents the circuit implementation of the architecture. Section 3.4 provides the prototype measurement result.

#### 3.2 Array Architecture and Stability Analysis

The proposed system of distributed sources is based on a collection of independently operating local oscillators. In such a system, in the absence of proper synchronization, each of the sources will operate at their own free-running frequency and phase

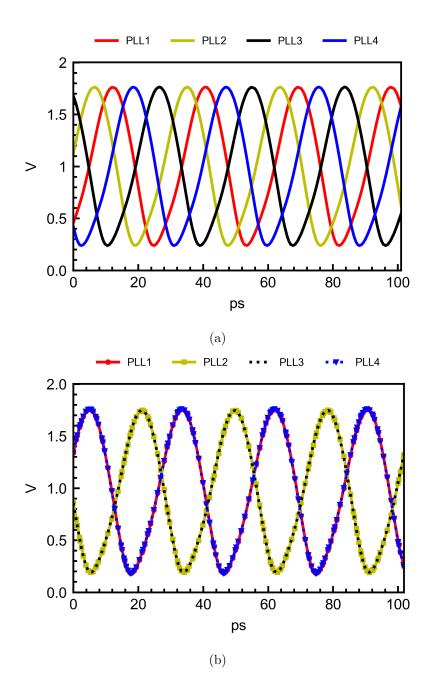

Figure 3.1: (a) Top: structure of the unit PLL, Bottom: a PLL array example. (b) Simulated phase locking of the distributed array.

undermining the coherent operation of the array. It is crucial to provide a mechanism to guarantee proper frequency synchronization between all the elements. One way to produce such synchronous behavior is by connecting all the units to a common external reference. However, such a method would also require distribution of such a reference across the entire array. Such a distribution would suffer from signal degradation effects similar to what we discussed earlier about normal LO distribution. Thus, we propose a frequency and phase locking method that would also scale with the structure in order to maintain scalability of the entire array. The proposed distributed PLL as shown in Fig. 3.1.a is composed of a collection oscillators that connect to their nearest neighbor through local interconnects. Each oscillator unit is connected to its own local PLL. At the same time neighboring PLL's can connect to each other to provide phase and frequency synchronization between neighboring elements. Such method is merely based on local connections and would not require the reference signal to connect throughout the array. However, such a network of phase locking modules could result in an increasingly complex and unpredictable dynamic. We study how the locking mechanism is affected by the way PLL's connect to each other. Next we propose the interconnect structure that achieves desired locking dynamics in the network.

In order to understand the locking mechanism Fig. 3.1.a shows the linear model of a type II PLL that contains two separate inputs as the reference signal. We will demonstrate how two input references enable two-dimensional extension of the distributed array. At the presence of two inputs we can write the phase dynamics of the PLL as:

$$\ddot{\phi_{out}} = k_1 \dot{\phi_{out}} + k_2 \phi_{out} - \frac{k_1}{2} (\dot{\phi_1} + \dot{\phi_2}) - \frac{k_2}{2} (\phi_1 + \phi_2),$$

where,  $\phi_{out}$  is the output phase of the unit PLL and  $\phi_1$  and  $\phi_2$  are the input phases to the unit.  $k_1$  and  $k_2$  are coefficients that depend on the circuit parameters of the oscillator, charge pump and filter. Based on this equation we can derive the dynamical equations of the array. The dynamics of the array including the position of the poles depend on the way the individual elements of the array are connected to each other.

Based on this model, we can show that when the blocks are connected in particular

orientations, the entire system maintains stable regardless of the size of the array. Fig. 3.1.b demonstrates the time-domain simulations of the 2-D distributed structure in Fig. 3.1.a. As the results indicate when the phases start from random initial conditions the phase and frequency of all oscillators lock to a common value.

As the array size increases, the poles in the transfer function of the system proportionally increase. Due to the new poles, the settling dynamics of the array change with the number of elements. However, beside the transient response, at steady state all the LO's are phase locked and frequency locked to the desired reference. While the in-band noise performance does depend on the specifics of the PLL position in the array, outof-band phase noise of the oscillators all follow the free-running frequency of the VCO regardless of the size of the array and the position of a particular oscillator inside the array. This ensure the array can scale while maintaining the same LO quality across all elements.

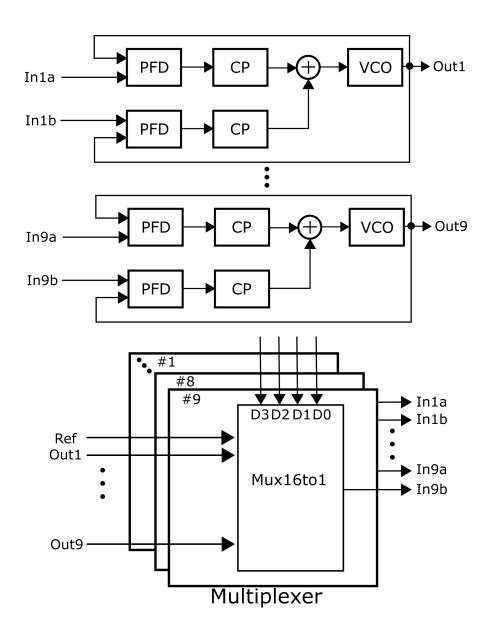

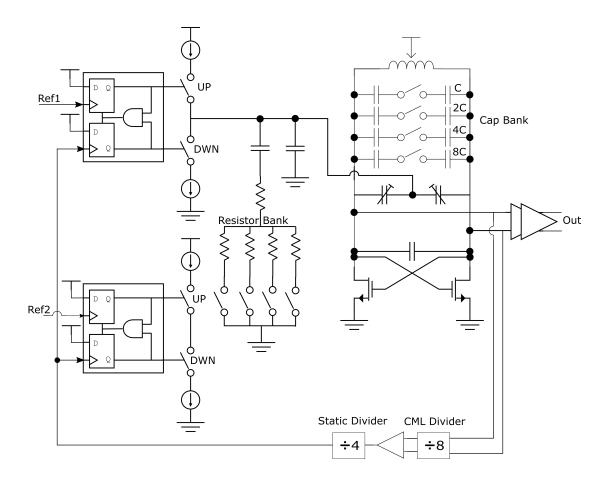

#### **3.3** Circuit Design and Implementation

In order to demonstrate the proposed concept we consider a design that includes multiple independently controlled unit PLLs that connect together in various configurations. Fig. 3.2 demonstrates the proposed architecture. The outputs of the divider chain in all the unit blocks connect to a common multiplexer. The multiplexer has twice as many outputs as inputs. This ensures that each unit cell gets two different input references from this block. Digital control of the multiplexer enables the output from a unit cell to connect to any input of any other unit cell.

An external reference also connects to the input of this mux to provide frequency control of the entire array. The digital interface enables the unit cells to configure in various forms. In the simplest form, both inputs of all PLLs can connect to the external reference. This reduces the array into a collection of standard phase locking units. Furthermore, it is possible to connect the output of this unit to the two inputs of the next unit. This becomes a basic 'daisy chain' configuration of the distributed PLL. It is also possible to connect the inputs of the PLL from two different outputs. For instance the inputs can be coming from two other PLLs or from one PLL and external reference. As we show in the next section this enables 2-dimensional array structures.

The VCO is designed to operate at 28GHz based on the standard cross-coupled pair. Continuous frequency tuning is achieved by adjusting the size of the varactor in the LC tank. A capacitor bank with 16 different configurations ensures that the oscillator frequency can tune by more that 10% around its center frequency. This tuning range ensures that all oscillators can lock together despite any undesired mismatch between them.

Fig. 3.3 shows the circuit details of the unit PLL. The output of the VCO connects to a buffer which is used for monitoring the output. A second buffer connects this output to the front-end of the divider chain. The high frequency dividers are designed based on common source master-slave D type flip flops. In order to ensure optimum power consumption, the lower frequency dividers are scaled in size and power.

Figure 3.2: Top level block diagram of the distributed PLL with re-configurable interconnects.

Figure 3.3: Unit PLL circuit.

Each PLL module contains two phase and frequency detectors (PFD's) followed by two charge pumps. The charge pump and PFD are designed to operate up to 1GHz. Proper sizing of the charge pump devices and adjusting the delay paths in the PFD ensure minimum phase error throughout the operation. Digitally controlled resistors in the loop filter enable digital control over the damping factor of the PLL. The outputs of the charge pumps add together in current mode and are then fed into the loop filter in accordance with the diagram in Fig. 3.1.a.

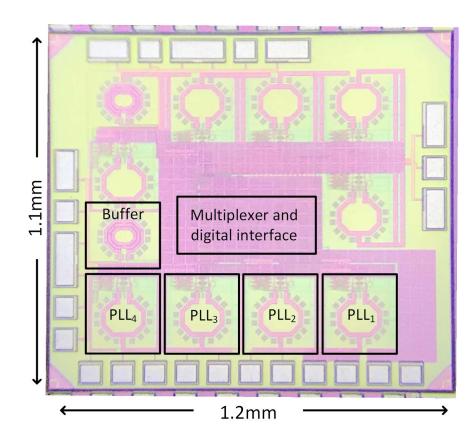

#### **3.4** Prototype Measurement

The chip is fabricated in the TSMC 65nm CMOS process. The die photo of chip is shown in Fig. 3.4. To measure the chip, the digital interface and the supplies are wirebonded to a QFN package. The external reference for the array is centered around 875MHz and is fed through RF probes to the digital multiplexer. The chip contains 9 oscillators, however due to measurement limitations we simultaneously measure a maximum 4 oscillators in any configuration which we label as  $PLL_1$  to  $PLL_4$ . The output of  $PLL_4$  is connected through RF probes to an R&S FSW67 spectrum analyzer for measurement.

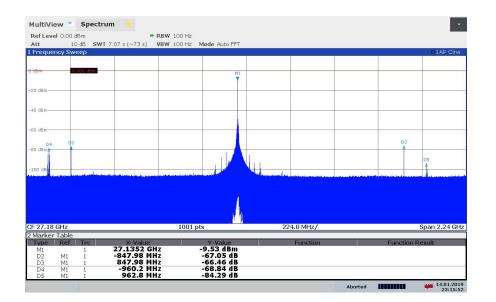

Each PLL consumes a total of 37mW where the VCO consumes 17mW and the divider chain including the input buffer consume 20mW. The power consume by the multiplexer and the rest of the blocks are negligible. Fig. 3.5 shows the measured spectrum of PLL<sub>4</sub> when all other PLL's are separated and are operating independently.

Figure 3.4: Chip microphoto.

Figure 3.5: Measured spectrum and reference spurs in the stand-alone PLL.

The reference spur is -66.5dBc with respect to the carrier frequency.

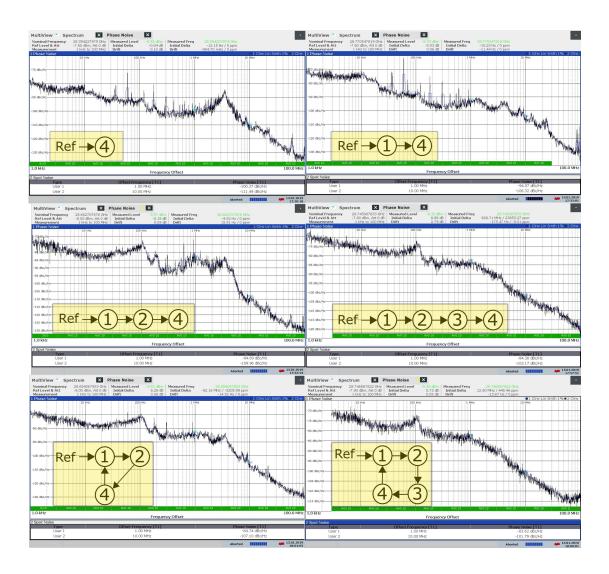

The chip is configured in several different structures and the spectrum and phase noise are measured accordingly. The six structures that we report include 1) stand alone PLL's connected to the reference, 2) three different daisy chain configurations with different length, and 3) two 2-dimensional structures with 3 and 4 PLL's. Fig. 3.6 plots the measured phase noise of the six different configurations. The second category (daisy chain) and the third category (triangular and rectangular loops) are the basic building blocks that can further extend the array in one dimension and two dimensions, respectively.

When all the PLL's are connected to the external reference (first configuration), the phase noise at 1MHz and 10MHz offset are -100.3 dBc/Hz and -111.4 dBc/Hz

Figure 3.6: Measured phase noise plot for 6 different array configurations: direct connection, 3x daisy chains, triangular and rectangular loops.

| Array configuration   | PN@1MHz             | PN@10MHz |

|-----------------------|---------------------|----------|

| and no. of PLLs       | $(\mathrm{dBc/Hz})$ | (dBc/Hz) |

| Unit PLL              | -100.3              | -111.4   |

| 2 element daisy chain | -94.1               | -106.3   |

| 3 element daisy chain | -84.7               | -109.9   |

| 4 element daisy chain | -84.3               | -103.2   |

| Triangular loop       | -84.7               | -107.1   |

Table 3.1: Measured phase noise for different array configurations at 28GHz.

respectively. The the measured phase noise of all the configuration are summarized in Table. 3.1. Since the simulated bandwidth of the PLL is 2.6MHz, the 1MHz offset measurement corresponds to in-band phase noise while the 10MHz represents out-of-band phase noise.

We observe that the in-band phase noise is the lowest when the PLL's are directly connected to the reference and increase with more number of PLL's connected to each other in the different configurations. This is expected as the quality of the reference signal degrades as it passes through multiple units. However, as opposed to regular daisy chaining, the out-of-band phase noise doesn't show significant degradation among the different configurations. In other words, the out-of-band noise (beyond 2.6MHz offset frequency) is not affected by the number of elements in the distributed array structure. The demonstrated daisy chaining and triangular structures are basic building blocks that can further extend to large 1D and 2D array structures.

While the in-band noise degradation does degrade the integrated noise across the entire frequency band, it is worth noting that for a mm-wave signal source at 28GHz, the signal bandwidth is at least two orders of magnitude larger than the designed PLL bandwidth of 2.6MHz. As a result, at high date rates with more that 100MHz bandwidth, the out-of-band phase noise is the dominant factor in determining the performance of the wireless system.

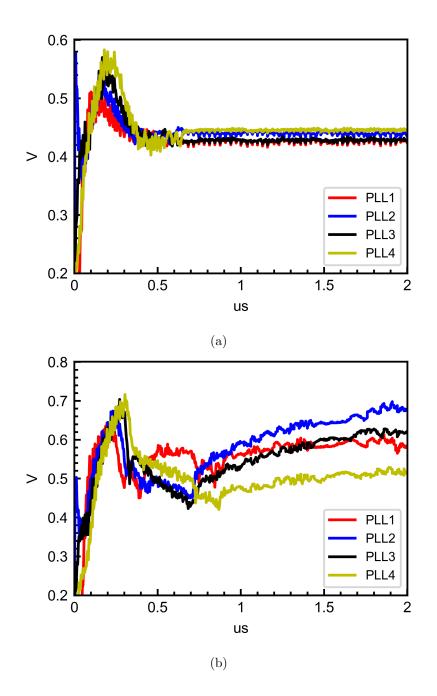

#### 3.4.1 Stability Analysis Considering Magnetic Coupling

In measurement, we observe the degradation of phase noise when we integrate more PLL elements into the CPLLA. The array eventually lost frequency locking when the number of elements is larger than four. This chip measurement result contrasts with the expectation from the circuit simulations. The reason is that magnetic coupling between inductors is not included as part of the considerations during the design phase. The coupling between oscillators introduces the additional phase tuning mechanism besides the prior phase control by the PLL loop. The two mechanisms have conflicting effects on phase, and introduce unsettling of the voltage level on the oscillator control node. As a result the phase noise is degraded, and furthermore, the array might not able to be frequency locked at all.

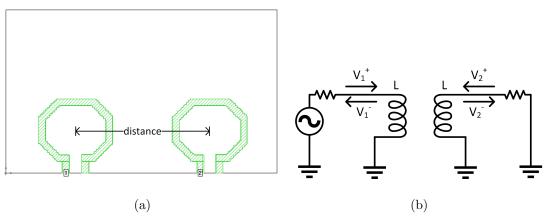

Figure 3.7: (a) EM modeling of two adjacent on-chip inductors in SONNET. (b) Equivalent circuit model.

To examine this explanation, we study the magnetic coupling effect quantitatively. First, the coupling between inductors is estimated by modeling the mutual inductance, as shown in Fig. 3.7a. In this test bench, inductors have the same dimension, spacing and substrate stack up with the inductors used in the chip design. Assuming the inductance of each inductor is L, and the coupling coefficient is k. Based on the equivalent circuit model as shown in Fig. 3.7b, we can calculate k by:

$$k = \frac{kL\frac{dI_1}{dt}}{L\frac{dI_1}{dt}} = \frac{V_2}{V_1}.$$

(3.1)

Further, we can calculate the value of k based on S parameters:

$$k = \frac{V_2}{V_1} = \frac{V_2^-}{V_1^+ + V_1^-} = \frac{S_{21}V_1^+}{V_1^+ + S_{11}V_1^+} = \frac{S_{21}}{1 + S_{11}}.$$

(3.2)

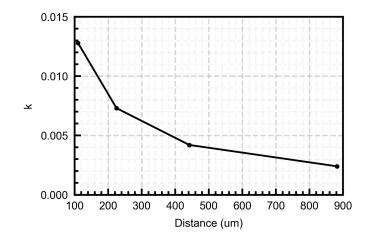

Based the simulated S parameters and equation (3.1), we calculate the coupling coefficient as a function of the distance between the centers of adjacent inductors, as shown

Figure 3.8: The coupling coefficient, k, is inversely depended on the distance between the adjacent inductors.

in Fig. 3.8. Consistent with intuition, the coupling coefficient is inversely dependent on the distance, and the drop of k roughly follows an exponential curve as the distance increases. As a result, the on-chip magnetic coupling is dominant between inductors of the neighboring oscillators. Since the distance between the on-chip neighboring inductors is  $250\mu$ m, we estimate that k is around 0.007.

To study the system-level effect of the magnetic coupling, we perform the top-level circuit simulation of a  $1 \times 4$  CPLLA. Since there are two phase control mechanism coexisting in the array: (1) magnetic coupling and (2) PLL control loop, we study their effect separately to learn their effect distinctively. Fig. 3.9a presents the settled transient phase of each PLL element fully controlled by the PLL loop, which means