# Design and Characterization Techniques for Reliable and Secure

**Integrated Circuits**

A DISSERTATION

## SUBMITTED TO THE FACULTY OF

## UNIVERSITY OF MINNESOTA

BY

Qianying Tang

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

## FOR THE DEGREE OF

# DOCTOR OF PHILOSOPHY

Advisor: Chris H. Kim

Februray 2017

© Qianying Tang 2017

# Acknowledgements

Firstly, I would like to express my sincere gratitude to my advisor, Prof. Chris H. Kim, for his patience, motivation, and constant support throughout my PhD study. For the past four and half years that he has been my advisor, I have learnt and benefitted a lot from his knowledge and expertise in circuit design. His enthusiasm and creativities in research has inspired me to explore all the possibilities and never give up trying new things. I could not have imagined having a better advisor for my Ph.D. study.

Next, I would like to thank Prof. Keshab K. Parhi for his guidance and constructive advising throughout my research. I also would like to than Prof. Kia Bazargan and Prof. Hubert H. Lim, for their insightful comments and guidance in writing this thesis. I appreciate their contribution of time to serve on my committee.

I am also thankful to China Scholarship Council and SRC for funding my study and research.

My sincere thanks also goes to Dr. Sungjae Lee for providing me an opportunity to join his team as intern in IBM. I also would like to Dr. Hongmei Lee, who mentored and helped me fulfill my project during the internship.

I'm deeply grateful to my labmates, for the encouraging discussions and plenty of joys we have had in the lab. I especially thank Xiaofei Wang, Bongjin Kim, Won Ho Choi, Yingjie Lao (Prof. Parhi's group), Chen Zhou and Saurabh Kumar for their devotional collaboration and valuable suggestions. My thanks also goes to the group senior alumni, Ki Chul Chun, Pulkit Jain, John Keane, for their valuable research legacy that I have learnt a lot from. Also I thank Seung-hwan Song, Xiaofei Wang, Bongjin Kim, Ayan Paul, Won Ho Choi, Hoonki Kim, Jongyeon Kim, Weichao Xu, Somnath Kundu, Paul Mazanec, Muqing Liu, Luke Everson, Po-Wei Chiu, Gyusung Park, Nakul Pande, Minsu Kim and Jeehwan Song.

Last but not the least, I would like to thank my parents Jun Tang and Fan Yang for supporting my pursuits and everything else in my life in general. Without them, I may never have gotten to where I am today. This dissertation is dedicated to the memories of my grandfather Zesheng Tang who led me to the wonderland of science and research.

# Abstract

For the past decades of years, device feature size has continued to shrink for achieving better performance at faster speed, lower power and higher circuit density. However, going to a smaller feature sizes also brings in reliability issues such as greater process variations and more aggressive performance degradation. To address these issues, circuits are designed with certain guard-band to avoid probable failures. In order to determine an appropriate guard-band, it is imperative to develop accurate and efficient methods for characterizing and collecting these reliability metrics. This dissertation considers two important circuit reliability issues: Random Telegraph Noise (RTN) and Radiation induced Soft Error. For characterizing the realistic impact of RTN on logic circuit, we proposed two on chip monitors using a 65nm and a 32nm process respectively based on a Beat Frequency Detection (BFD) technique. The impact of RTN on logic and SRAM performance was analyzed based on the measured data. In the chapter 3, a compact 2 Transistor (2T) radiation sensor with tunable measurement sensitivity implemented in a 65nm LP bulk process is presented. The 2T sensor array exhibits a 117X higher sensitivity as compared to a 6T SRAM cell under an alpha particle radiation test.

Meanwhile, with the electronic devices become increasingly ubiquitous and interconnected, demand for secure system design has also increased. In particular, hardware-oriented security has emerged as a new solution to provide another dimension of security in additional to the conventional software-oriented security. Many of the hardware security primitives seek to leverage the process variation, in contrast to suppress it for the sake of performance, to against post-silicon attacks. For example, hardware security building blocks such as true random number generators (TRNGs) and physical unclonable functions (PUFs) employ the CMOS devices inherent variation to extract entropy: the former one takes advantage of the time-variant random noise and latter one is based on the manufacturing induced random variation. In this dissertation, one TRNG and two lightweight PUFs are presented. The TRNG measures the frequency difference between two free-running ring oscillators to extract random frequency jitter. Benefitted from the differential structure, the proposed circuit fabricated in 65nm TRNG test chips passed all 15 NIST tests without the use of any feedback or tracking scheme in a supply voltage range from 0.8V to 1.2V. The final part of the dissertation presents two lightweight PUFs that are based on existing Dynamic Random-Access Memory (DRAM) and Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC) blocks respectively.

# **Table of Contents**

| Abstract       | iv                                                                   |

|----------------|----------------------------------------------------------------------|

| Table of Con   | tentsvi                                                              |

| List of Figure | esix                                                                 |

| Chapter 1.     | Backgrounds1                                                         |

| 1.1.           | Circuit Reliability1                                                 |

| 1.1.1          | . Random Telegraph Noise1                                            |

| 1.1.2          | . Soft Error4                                                        |

| 1.2.           | Hardware Security                                                    |

| 1.2.1          | . True Random Number Generator (TRNG)8                               |

| 1.2.2          | . Physical Unclonable Function (PUF)9                                |

| Chapter 2.     | On chip RTN Monitors                                                 |

| 2.1.           | Introduction13                                                       |

| 2.2.           | Beat Frequency Technique for RTN Monitoring15                        |

| 2.3.           | Characterizing RTN with a Single Array Structure on a 65nm Process17 |

| 2.3.1          | . RTN Monitor Design17                                               |

| 2.3.2          | . RTN Induced Frequency Shift Measurements on 65nm Test Chip19       |

| 2.4.           | Characterizing RTN with a Dual Array Structure on a 32nm HKMG        |

| Process        |                                                                      |

|      | 2.4.1   | . Dual Ring Oscillator Array Technique                        | 27 |

|------|---------|---------------------------------------------------------------|----|

|      | 2.4.2   | 2. RTN Induced Frequency Shift Measurements on 32nm Test Chip | 30 |

|      | 2.4.3   | 8. RTN Impact on Logic Timing                                 | 36 |

|      | 2.4.4   | RTN Impact on SRAM Stability and Timing                       | 41 |

|      | 2.5.    | Conclusion                                                    | 44 |

| Chaj | pter 3. | Compact High-Sensitivity Radiation Sensor Array               | 46 |

|      | 3.1.    | Introduction                                                  | 46 |

|      | 3.2.    | 2T Sensor Array                                               | 47 |

|      | 3.3.    | Alpha Particle Experiment                                     | 50 |

|      | 3.4.    | Single Event Upset Simulation                                 | 57 |

|      | 3.5.    | Conclusion                                                    | 60 |

| Chaj | pter 4. | True Random Number Generator                                  | 61 |

|      | 4.1.    | Introduction                                                  | 61 |

|      | 4.2.    | Beat Frequency Detector based TRNG                            | 63 |

|      | 4.2.1   | . Test Chip Implementation                                    | 65 |

|      | 4.2.2   | 2. Measurement Data                                           | 66 |

|      | 4.3.    | Simulation and Modeling                                       | 74 |

|      | 4.4.    | Multi-phase TRNG for Enhancing the TRNG Generation Efficiency | 75 |

|      | 4.4.1   | . Circuit Implementation                                      | 75 |

|      | 4.4.2   | 2. Measurement Data                                           | 77 |

|      | 4.5.    | Conclusion                                                    | 79 |

| Chapter 5. | Physical Unclonable Function                                  | 80      |

|------------|---------------------------------------------------------------|---------|

| 5.1.       | Introduction                                                  | 80      |

| 5.2.       | Conventional PUFs                                             | 81      |

| 5.3.       | DRAM based PUF for Chip Authentication                        | 83      |

| 5.3.1      | . Proposed DRAM PUF Design                                    | 86      |

| 5.3.2      | 2. Improving DRAM PUF Reliability                             | 90      |

| 5.3.3      | 3. Test Chip Measurement                                      | 93      |

| 5.4.       | Charge-redistribution based PUF for Chip Authentication using | ; a SAR |

| ADC Circ   | uit                                                           | 99      |

| 5.4.1      | . Background                                                  | 99      |

| 5.4.2      | 2. Charge-redistribution PUF Design                           | 104     |

| 5.4.3      | 3. Test Chip Measurement Result                               |         |

| 5.5.       | Conclusion                                                    | 114     |

| Chapter 6. | Conclusion                                                    | 116     |

| References |                                                               | 119     |

# **List of Figures**

| Figure 1.1: Random trapping and de-trapping of carriers causes fluctuation in Vt, resembling a random telegraph signal                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: Distribution of emission times at 95K and Vgs = 1.15V, showing that the time is Poisson distributed [1]                                                                                                                                                                                       |

| Figure 1.3: Frequency-domain representation of the RTN signal [2]4                                                                                                                                                                                                                                        |

| Figure 1.4: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion [19]                                                                                                                                          |

| Figure 1.5: A typical authentication protocol involves utilization of TRNG and PUF circuit                                                                                                                                                                                                                |

| Figure 1.6: (a) Conventional authentication scheme stores keys in NVM. (b) Using strong PUF for direct authentication [53]                                                                                                                                                                                |

| Figure 1.7: Intra-chip and inter-chip HD under (a) secure condition and (b) unsecure condition [40]                                                                                                                                                                                                       |

| Figure 2.1: Comparison of different RTN characterization techniques14                                                                                                                                                                                                                                     |

| Figure 2.2: Beat frequency detection circuit adopted in this work for measuring RTN induced delay shifts at sub-0.5V supply voltages with high resolution. The output count N represents the number of $f_B$ clock cycles that can fit within a single beat frequency (i.e. $f_A$ - $f_B$ ) clock period. |

| Figure 2.3: ROSC array test chip for RTN measurements comprising an on-chip beat frequency detection                                                                                                                                                                                                      |

| Figure 2.4: Comparison of three ROSC based RTN measurement techniques18                                                                                                                                                                                                                                   |

| Figure 2.5: Single trap RTN waveforms measured from different ROSCs19                                                                                                                                                                                                                                     |

| Figure 2.6: (b) Single and multi-trap RTN waveform from two different ROSCs. (b)                                                                                                                                                                                                                          |

| Time Lag Plot (TLP) of the two traces                                                                                                                                                                                                                                                                     |

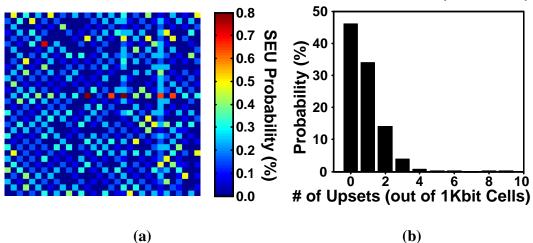

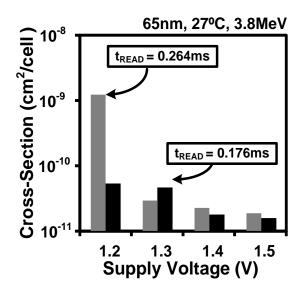

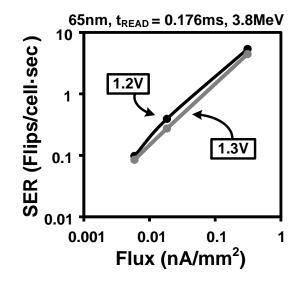

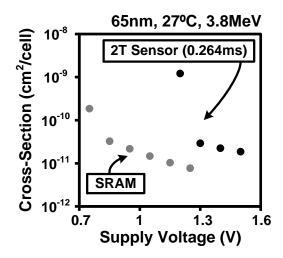

| Figure 3.7: Measured cross-section increases with lower supply voltage                                                                                                                                                                                                                            |

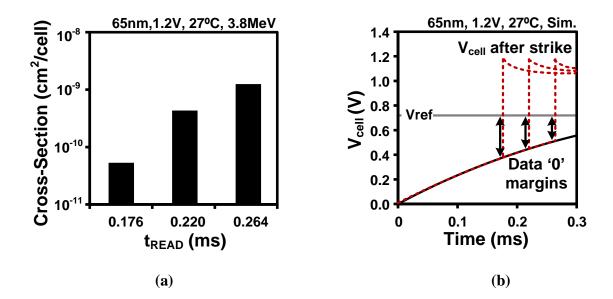

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.8: (a) Measured cross-section increases with longer $t_{READ}$ due to the reduced data read margin as shown in (b)                                                                                                                                                                       |

| Figure 3.9: Measured SER is proportional to alpha particle flux                                                                                                                                                                                                                                   |

| Figure 3.10: Measured cross-section of 2T cell and SRAM at different supply voltages. 57                                                                                                                                                                                                          |

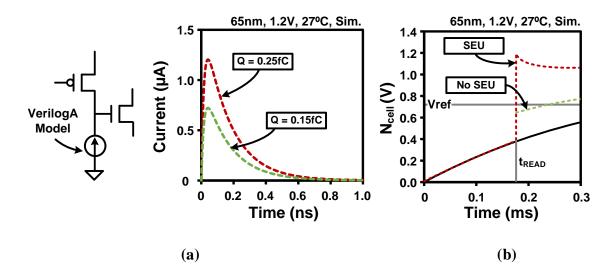

| Figure 3.11: (a) Simulated current pulse using double exponential model and (b) 2T sensor transient response with $Q_{total}$ equal to 0.25fC and 0.15fC respectively                                                                                                                             |

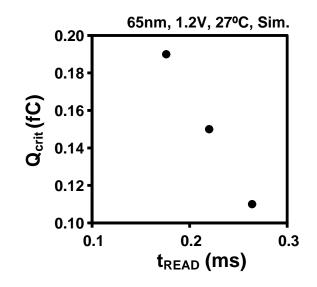

| Figure 3.12: Q <sub>crit</sub> decrease with a longer t <sub>READ</sub>                                                                                                                                                                                                                           |

| Figure 3.13: Simulated Qcrit for inverter, 6T SRAM, and 2T sensor                                                                                                                                                                                                                                 |

| Figure 4.1: A conventional meta-stability based TRNG [38]63                                                                                                                                                                                                                                       |

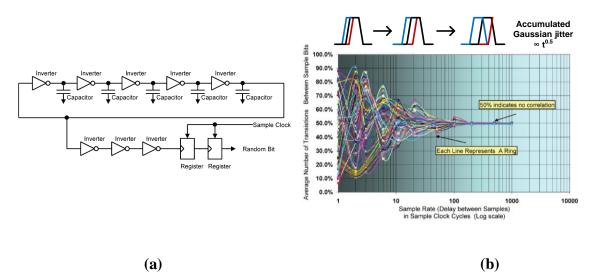

| Figure 4.2: (a) ROSC based TRNG employed in IBM POWER7+. (b) Probability of two consecutive bits being different as a function of sampling period (=wait time) for IBM's ring oscillator TRNG. Jitter accumulation time must be >200 ROSC cycles for the sampled bit to be considered random [40] |

| Figure 4.3: Basic principle of the proposed beat frequency based TRNG circuit                                                                                                                                                                                                                     |

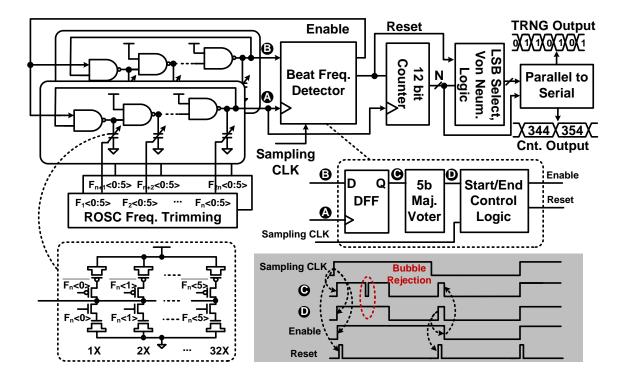

| Figure 4.4: TRNG circuit with trimming caps and power saving mode                                                                                                                                                                                                                                 |

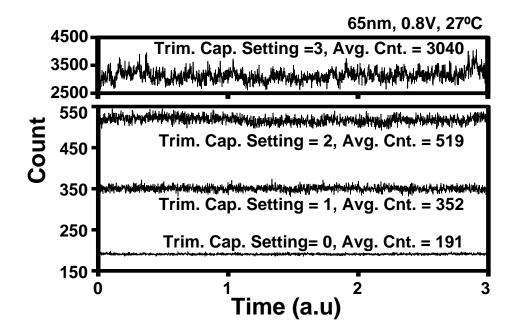

| Figure 4.5: Measured beat frequency count for different trim capacitor settings                                                                                                                                                                                                                   |

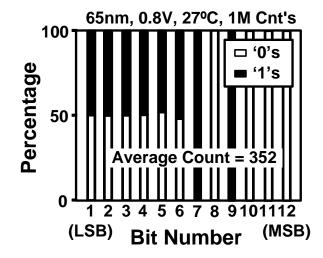

| Figure 4.6: Percentage of '1's and '0's for each bit of the beat frequency count output. The lower significant bits (e.g. bits 1, 2, 3) have better randomness compared to the higher bits                                                                                                        |

| Figure 4.7: NIST test verifies the randomness of 1st ~3 <sup>rd</sup> LSBs69                                                                                                                                                                                                                      |

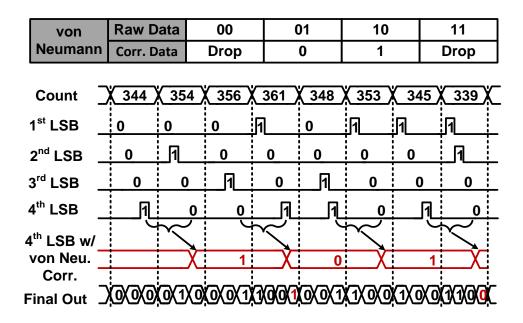

| Figure 4.8: Concatenating LSBs to generate the final TRNG output bit stream. 4th LSB can be used after von Neumann correction                                                                                                                                                                     |

| Figure 4.9: Concatenated 1st~4th LSBs passes all NIST test after applying Von Neumann correction on the 4th LSB71                                                                                                                                                                                 |

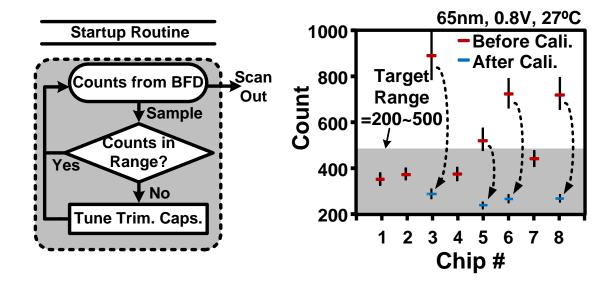

| Figure 4.10: One-time calibration of average count during start up                                                                                                                                                                                                                                |

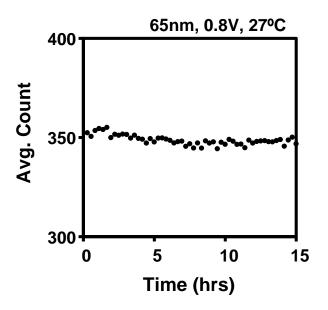

| Figure 4.11: Stability under continuous operation73                                                                                                                                                                                                                                               |

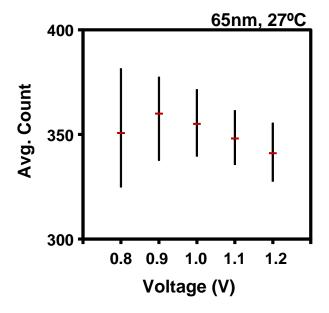

| Figure 4.12: Measured count under different voltages                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

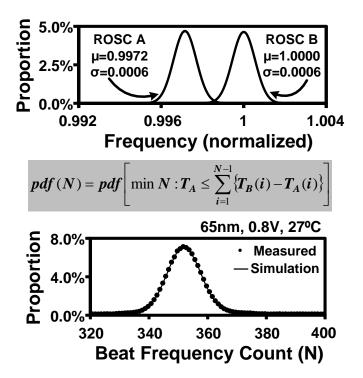

| Figure 4.13: (Upper) Individual ROSC frequency distributions estimated using statistical model and measured data. (Lower) Measured count distribution shows good agreement with simulated data |

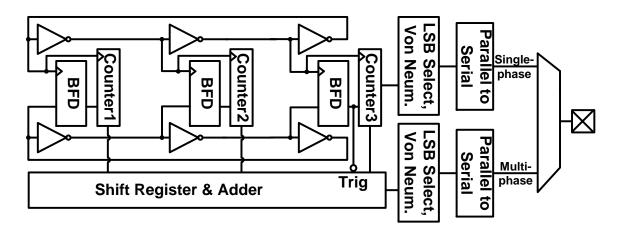

| Figure 4.14: Multi-phase TRNG implementation (3 phase example)76                                                                                                                               |

| Figure 4.15: The number of LSBs with good randomness increases under the same sampling time as compared to the single-phase version                                                            |

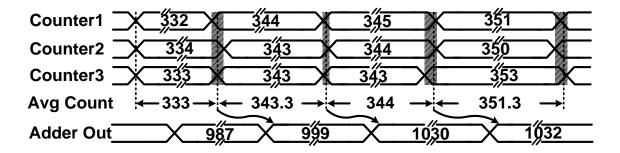

| Figure 4.16: Measured count output from single-phase and multi-phase TRNGs                                                                                                                     |

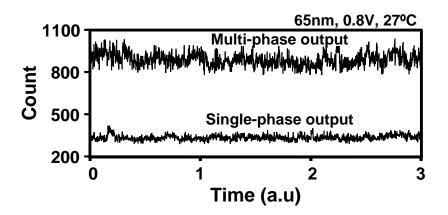

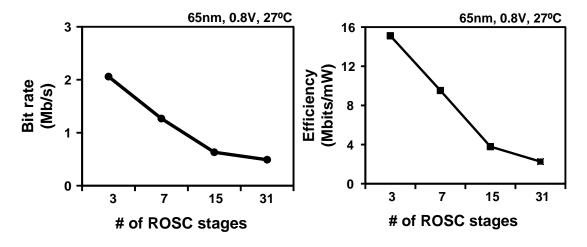

| Figure 4.17: The number of random bits per output that passes all NIST test as well as the TRNG generation efficiency improves using the proposed multi-phase structure                        |

| Figure 4.18: Multi-phase TRNG utilizing fewer ROSC stages shows improved bit rate and efficiency                                                                                               |

| Figure 4.19: Single-phase and multi-phase TRNG chips in 65nm79                                                                                                                                 |

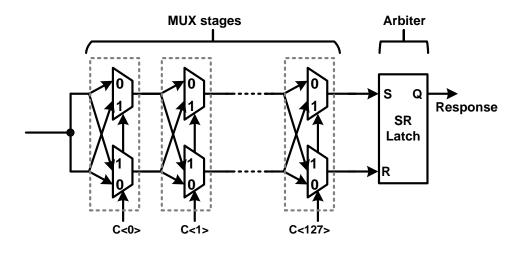

| Figure 5.1: Schematic of an arbiter PUF                                                                                                                                                        |

| Figure 5.2: SRAM based PUF83                                                                                                                                                                   |

| Figure 5.3: Qualitative comparison between SRAM PUF and DRAM PUF85                                                                                                                             |

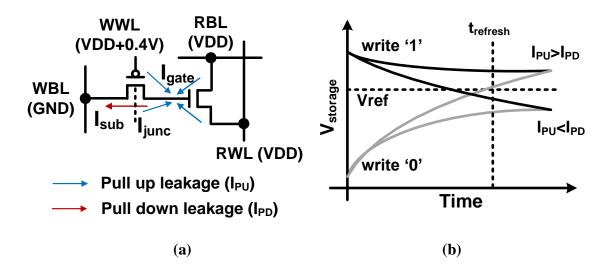

| Figure 5.4: (a) 2T DRAM cell schematic and leakage components in hold mode. (b) A DRAM cell generates a different response depending on the write data and retention time.                     |

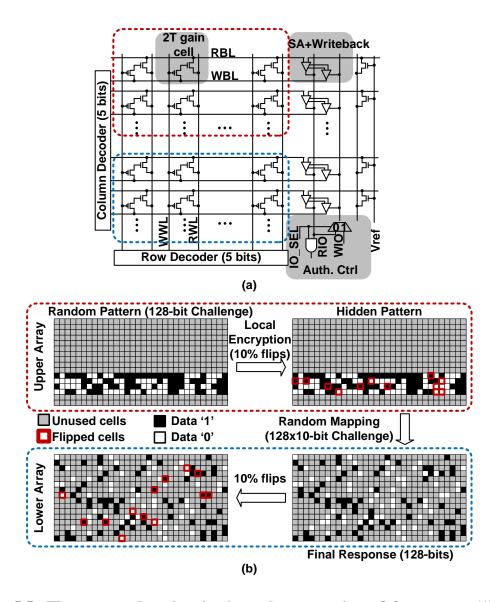

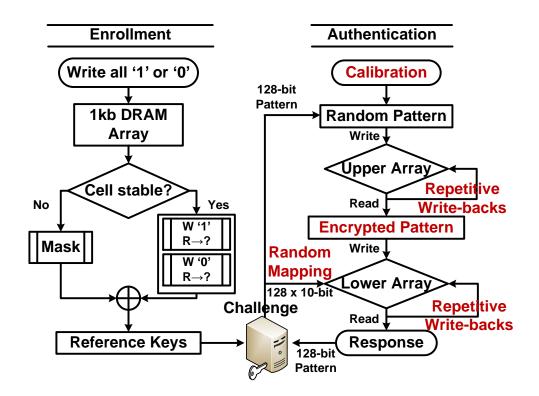

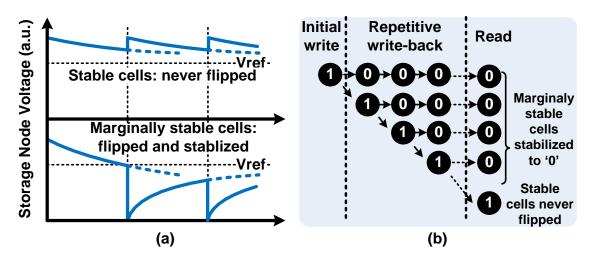

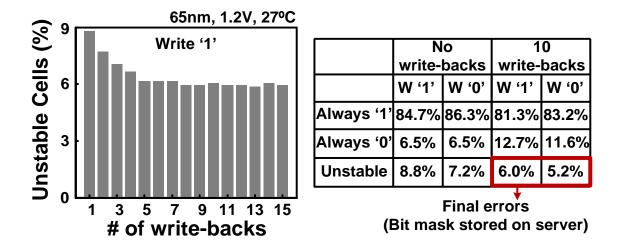

Figure 5.5: The proposed authentication scheme consists of four steps: (1) write random 128 bit challenge to DRAM upper array, (2) allow 10% of bits to flip due to retention failure, (3) transfer data to lower array according to random mapping info from server, and finally (4) repeat step (2). The inherent DRAM retention failure rate is utilized for generating a unique and secure response. For the chip demonstration, we chose a 128-bit random input pattern, a 128 x 10 bit random address mapping info (=128+128x10=1,408 total challenge bits) and a 128-bit response.

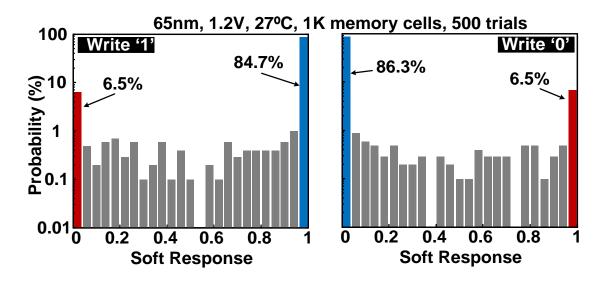

Figure 5.7: DRAM PUF soft response distribution for data '1' and data '0'. Soft response is defined as the average response value over 500 trials. For example, if the output for a

Figure 5.10: 65nm DRAM PUF chip micrograph and summary table......94

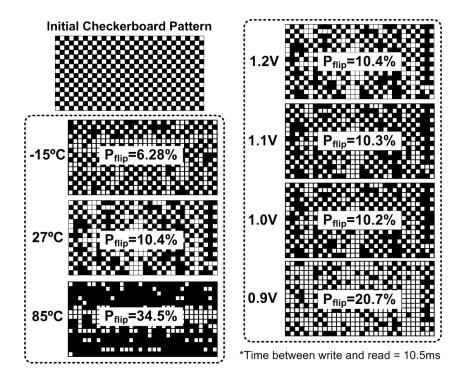

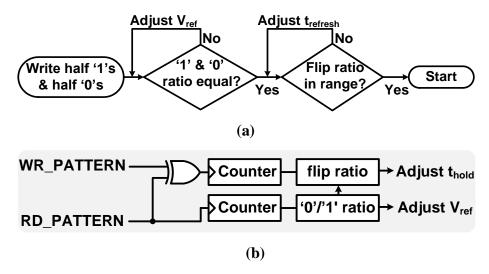

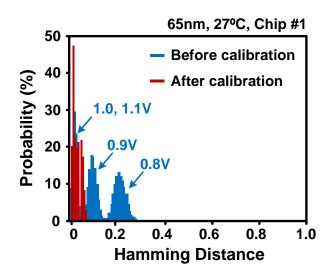

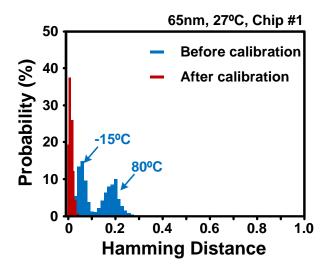

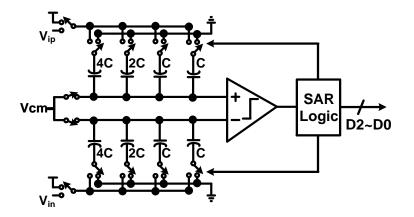

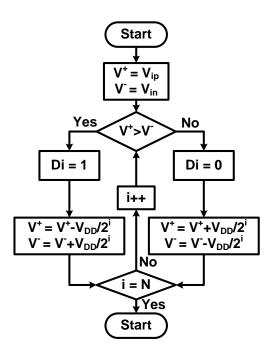

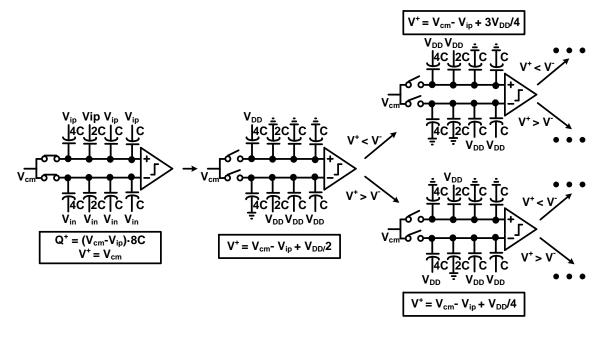

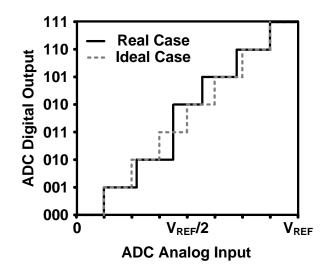

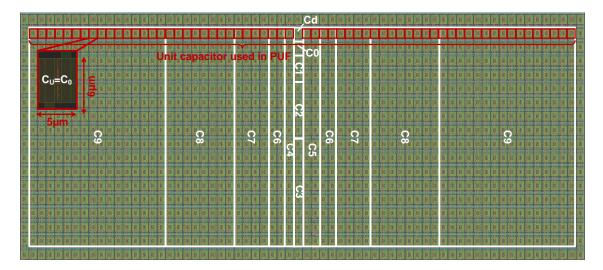

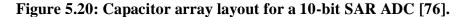

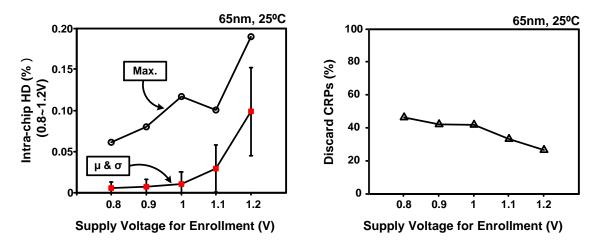

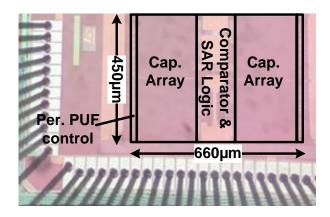

Figure 5.12: DRAM retention failure map measured under different supply voltages and temperatures. The failure probability can be kept within the desired range of 9.5% < P < 11% before each authentication test using the calibration scheme described in Figure 5.13: A pre-authentication calibration scheme to mitigate the V, T drifts induced Figure 5.14: Distributions of Hamming distance measured at different supply voltages Figure 5.15: Distributions of Hamming distance measured at different temperatures Figure 5.16: Comparison between conventional arbiter, memory and the proposed charge sharing PUFs. .....101 Figure 5.17: 3-bit SAR ADC architecture. .....101 Figure 5.18: (a) SAR algorithm; (b) DAC switching procedures [74]. .....103 Figure 5.19: Transfer curve for a 3-bit SAR ADC with and without capacitor mismatch. Figure 5.20: Capacitor array layout for a 10-bit SAR ADC [75].....105 Figure 5.21: (a) Schematic and (b) timing diagram of the proposed charge redistribution

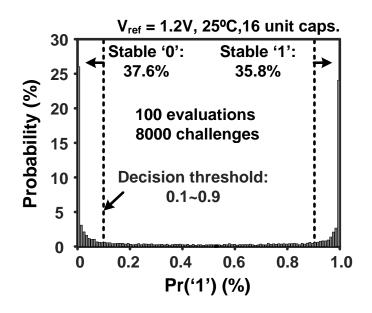

Figure 5.22: Measured soft response distribution for the charge redistribution PUF.....109

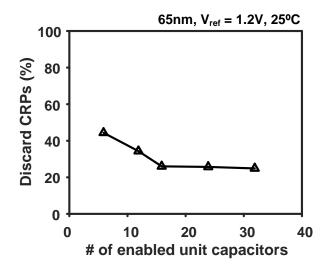

Figure 5.24: Percentage of discard CRPs for different # of enabled unit capacitors. .....111

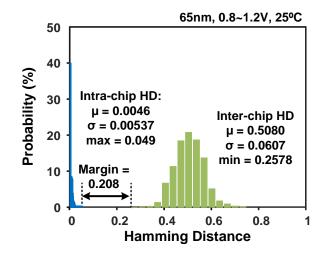

| Figure  | 5.26:   | Measured | inter-chip | and | intra-chip | Hamming | Distance | distributions | and  |

|---------|---------|----------|------------|-----|------------|---------|----------|---------------|------|

| evaluat | tion co | nditions |            |     |            |         |          |               | .113 |

|         |         |          |            |     |            |         |          |               |      |

Figure 5.27: 65nm charge-redistribution based PUF chip micrograph. .....114

# **Chapter 1. Backgrounds**

# **1.1. Circuit Reliability**

#### 1.1.1. Random Telegraph Noise

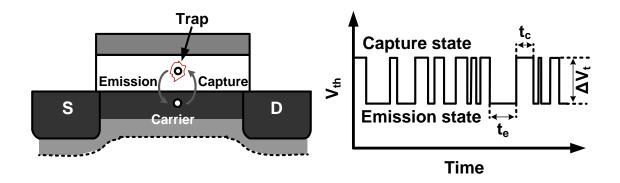

Parametric shifts caused by temporal random trapping and de-trapping of carriers in the channel, also known as Random Telegraph Noise (RTN), have become a growing concern in extremely scaled CMOS. RTN coupled with Random Dopant Fluctuation (RDF) is predicted to have a detrimental effect on SRAM cell stability beyond 15nm. These traps are believed either be defects created during the fabrication process or generated by voltage stress during normal operation. This situation has spurred a number of studies focusing on the characterization and mitigation of RTN effects. Conventional defect models assume that the defect can exist in two states, one is charged and the other is discharged. Defects capture and emit carriers in a random pattern as shown in Figure 1.1(a). As a consequence, the threshold voltage would switch between two discrete voltage levels, consistent with a two-state Markov process, as shown in Figure 1.1(b).

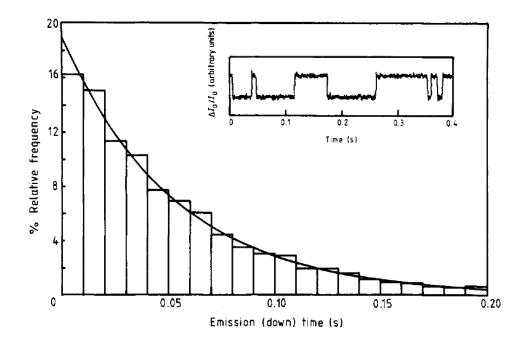

A typical single trap RTN impact on CMOS devices can be characterized by three parameters: the capture time (t<sub>e</sub>), the emission time (t<sub>c</sub>) and the amplitude  $\Delta V_{th}$ . The capture and emission times are randomly distributed while the amplitude is usually fixed. By collecting the RTN data for a sufficiently long period of time, it can be observed that the probability of  $t_e$  and  $t_c$  appear to be Poisson distributed as shown in Figure 1.2. The distribution is described as follow [1]:

$$\Pr(t) = \frac{1}{\tau} \exp\left(-\frac{t}{\tau}\right)$$

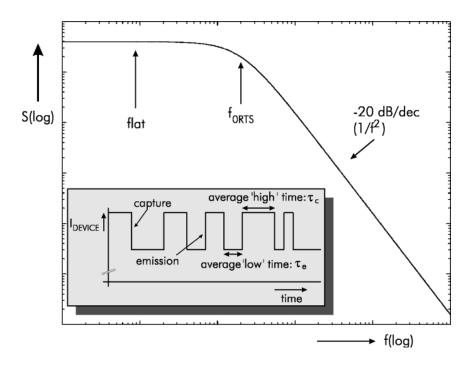

where  $\tau$  is the RTN time constant defining the average time a trap site stays in the captured state or in the emission state. The capture and emission time constants ( $\tau_c$  and  $\tau_e$ ) then can be extracted separately from the collected data. It is reported that RTN time constants range from microseconds to seconds which depends on both the operation conditions, i.e. supply voltage, temperature, and defect locations. For circuits operated at a frequency higher than the RTN time constant (e.g. >1MHz), a capturing event induced threshold voltage increase can be treated as a constant parametric shift which may induce errors that are un-recoverable within one clock period. By applying a Fourier transform of the stationary two-level signal, the corresponding power spectrum is a Lorentzian as shown in Figure 1.3 [2]. The corner frequency of such noise spectrum is determined only by  $\tau_c$  and  $\tau_e$  defining as:

$$f_{0RTN} = \frac{1}{2\pi} \left( \frac{1}{\tau_c} + \frac{1}{\tau_e} \right)$$

Figure 1.1: Random trapping and de-trapping of carriers causes fluctuation in Vt, resembling a random telegraph signal.

Figure 1.2: Distribution of emission times at 95K and Vgs = 1.15V, showing that the time is Poisson distributed [1].

Figure 1.3: Frequency-domain representation of the RTN signal [2].

#### 1.1.2. Soft Error

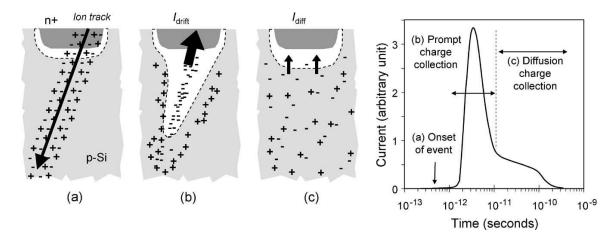

Another concern in the field of circuit reliability is soft error, which is referred to the type of errors that are uncontrollable, random and usually not catastrophic. These errors are induced by particle strikes, either from the radioactive atoms released by the package material or interaction between cosmic rays and the atmosphere. One of the most commonly seen particles is the alpha particle, which is essentially a helium nucleus that carriers a +2 charge, written as He<sup>2+</sup>. Compared to other radiation particles, alpha particle is heavy (two protons and two neutrons) and highly ionized therefore has the lowest penetration depth. The interaction between particles and silicon device is shown in Figure 1.4. When a charged particle strikes at the reverse-biased p-n junction, it creates an ionized path through the penetration track. Under the effect of electric field, carriers

created by the strike are collected by the diffusion region resulting in a large transient current pulse. If the current pulse is sufficiently large, a soft error may occur. Nondestructive soft errors can be categorized into two types: (1) Single Event Transient (SET) which generates a voltage glitch propagating through a combinational logic path and (2) Single Event Upset (SEU) which causes a data flip of a memory cell or register.

Figure 1.4: Charge generation and collection phases in a reverse-biased junction and the resultant current pulse caused by the passage of a high-energy ion [1].

### **1.2. Hardware Security**

With the development of the Internet of Things (IoTs), achieving secure and trustworthy communication and computation is becoming increasingly challenging. Protections from software level alone is proven to be insufficient, especially against physical attacks such as fault injection, micro-probing and cloning [58]-[62]. Hardware security, aims at providing a silicon solution towards those physical attacks, has emerged and gained attractions in both academia and industry. Traditional hardware security modules are based on cryptographic primitives such as secret key storage,

cipher/decipher blocks (e.g. AES, RSA) and random number generators (RNG). These modules are proven effective and suitable for mainframe computers, especially for those with high performance and require a high level of security. However, due to the computationally intensive algorithm, conventional hardware security primitive are generally power consuming and costly thus are undesired for most of the portable platform. In addition, the fact that mobile devices are distributed, unsupervised and resource-limited further aggravates the situation. As a result, hardware security design are expanded from protecting mainframe servers to distributed lightweight devices. Different lightweight oriented cryptographic protocols has been proposed and discussed [53]-[54] for applications in the source constrained ICs such as sensors, smart cards, and health care gears. Although refining the cryptographic algorithm or protocol will improve the level of security, of equal importance is to provide a more secure entropy source through underlying ICs. The primary focus of our work is to implement hardware security building blocks that are reliable, difficult to break and cost efficient. To begin with, we can consider an authentication scenario between two parties: a resource-abundant server and a resource-limited token.

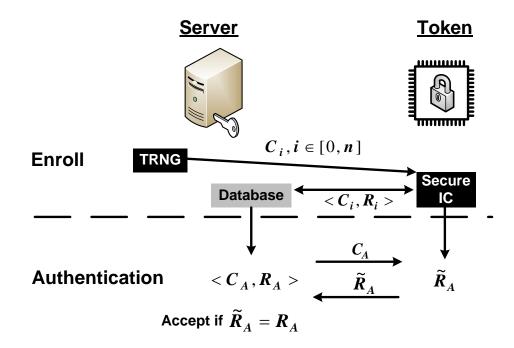

One of the simplest lightweight authentication schemes is shown in Figure 1.5 [56]. Before deploying the device, a one-time enrollment is required. The server randomly generates some challenges ( $C_i \in C_n$ ) with an RNG. The token device produces the corresponding responses thus forming the Challenge and Response Pairs (CRPs:  $\langle C_i, R_i \rangle$ ). The server collects and safely stores the CRPs in the database. Before distributing the devices to clients, the enrollment interface will be permanently destructed in order to prevent any possible micro-probing attacks. In the authentication phase, the server again randomly retrieves a challenge from its database. A genuine token then should return the response that matches the corresponding response stored in the database ( $\mathbf{R}_i = \widetilde{\mathbf{R}}_i$ ) [54].

Figure 1.5: A typical authentication protocol involves utilization of TRNG and PUF circuit.

In general, any authentication is breakable given enough time, motivation and resources. Improving the security is essentially to increase the cost for an adversary [53]. In addition to employing a more complex authentication protocol, utilizing novel authentication building blocks can be another solution to improve the security. From the server side, utilizing a True Random Number Generator (TRNG) helps enhance the security by making the random bit-streams (e.g., secret key, challenges for a PUF) more

difficult to guess. From the token side, Physical Unclonable Function (PUF) provides a low cost solution as compared to conventional Non-Volatile Memory (NVM) based authentications.

#### **1.2.1.** True Random Number Generator (TRNG)

The security of a network, in a large extent, relies on how unpredictable the secret data is appeared to unauthorized parties. Random numbers therefore are vital to many crypto protocols. Besides generating random challenges for authentications, another important application of random numbers is to provide the private and public key pairs for encrypting messages.

Depending on the approach to generate it, random data can be categorized into pseudo random numbers and true random numbers. Pseudo random numbers, as the name indicated, are essentially generated with algorithms that use mathematical formulae or simply pre-calculated tables. In most of the applications, a Pseudo Random Numbers Generator (PRNG) will be sufficient as the repeating period of the generated random sequence is so long that determinacy can be ignored. However for operation which requires high level security, e.g. the transaction between bank terminals, a truly random data is required. TRNGs are referred to those extracting randomness from physical phenomena, e.g. the circuit noise. The major advantage of TRNG over PRNG is its high unpredictability which increases the difficulty for attackers to guess the random sequence.

#### **1.2.2.** Physical Unclonable Function (PUF)

In a cryptographic system, the lightweight devices are generally used in the token side, namely the parties being authorized. Security tokens conventionally store the secret information, e.g. digital signature or biometric data, in NVMs such as EEPROM or fuses. During an authentication, cryptographic blocks import the secret information as a reference key to perform the designated protocols. NVMs are able to provide some basic protections however are becoming less effective on protecting mobile devices due to the following reasons. (1) As the attacking techniques improve significantly in the past years, NVMs are becoming more easily breakable under offline attacks such as cloning, reverse engineering and fault attacks. (2) NVMs are not logic-compatible therefore are oppose to the low-cost requirement for portable devices. (3) Conventional cryptographic hardware is still required to achieve the secure operations.

To address the problems faced by the NVM based authentication techniques, an alternative approach, Physical Unclonable Function (PUF) was proposed. Instead of burning in the secret information in a device, a PUF extracts the random features from the manufacturing induced random variation. PUFs are feasible for a lightweight authentication due to the following reasons: (1) Compatible with the standard logic process therefore less expensive than NVMs; (2) Some PUFs can be directly used for authentication without using additional cipher blocks; (3) Irreversible as the entropy source comes from the physical characteristic of the chip. (4) Immune to offline attacks. PUFs can be categorized in two classes, depending on the number of available CRPs they

can offer. Weak PUFs offers limited number of CRPs therefore is generally employed as a substitute to Non-Volatile Memories (NVMs) to store the secret key. Strong PUFs, in contrast, offers an enormous number of CRPs which are exponentially proportional to the block area. The strong PUF thus can be authenticated directly without using any cryptographic hardware.

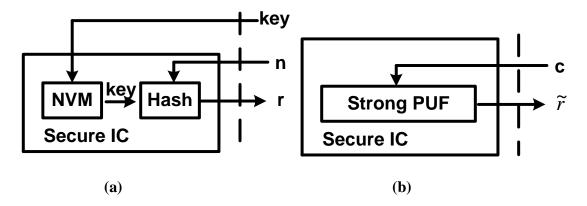

Figure 1.6: (a) Conventional authentication scheme stores keys in NVM. (b) Using strong PUF for direct authentication [54].

Figure 1.6 compares the conventional NVM based and strong PUF based authentication methods. In Figure 1.6(a), a secret key is programmed in NVM during enrollment. An additional cryptographic hardware (e.g. a Hash function) performs the encryption to provide a secure protection. The server sends a random nonce n and receives a response r from the token. The token will be authorized if r = Hash (k,n). Strong PUF based authentication, as shown in Figure 1.6(b), simplify the scheme by incorporating both the secret key and hash function in a single one way function.

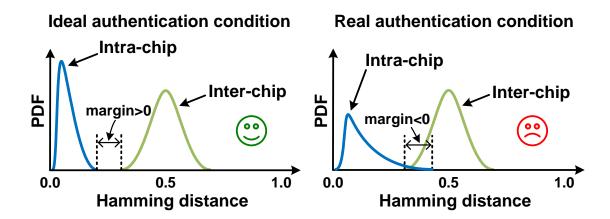

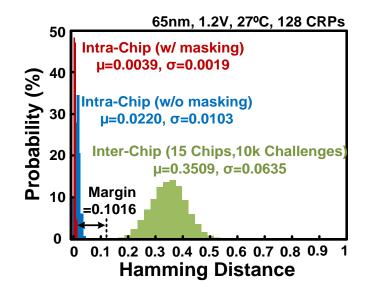

To evaluate the PUF performance, we introduce two concepts: intra- and inter- chip Hamming Distance (HD) [73]. The former represents the reproducibility of the responses while the latter represents the uniqueness of the responses. The intra-chip HD calculates the differences between the expected responses and the actual PUF outputs for the same challenges from a single chip. Inter-chip HD, on the other hand, evaluates how uniquely a PUF is distinguished from other PUFs. This is generally estimated over a group of chips by applying a large set of CRPs. In general, the HD is calculated as follow:

$$HD(x, y) = \sum_{i=1}^{n} (x \oplus y)$$

where x and y represent two n-bit responses. Based on this equation, an ideal token requires 0 inter-chip HD and 0.5 inter-chip HD. However, the PUF behavior is generally very sensitive to environmental variables such as thermal noise, supply voltage and temperature shifts. Therefore, to authentication a token, only an approximated match is required between the actual response and the CRP in the database. As shown in Figure 1.7, to guarantee a safe operation, the intra- and inter- chip HD distribution are required to be sufficiently separated with a certain margin. Otherwise, a post-processing procedure is required [55][74].

Figure 1.7: Intra-chip and inter-chip HD under (a) secure condition and (b) unsecure condition [55].

# Chapter 2. On chip RTN Monitors

# 2.1. Introduction

One direct impact of RTN on CMOS transistor is the V<sub>th</sub> fluctuation between capture and emission states which resembles a random telegraph signal. Recent studies on RTN aided by new characterization methods have helped establish a better understanding of the underlying physics. Figure 2.1 compares different RTN characterization techniques. Traditionally, characterization of RTN involved continuously monitoring the transistor drain current for a large population of devices using individual probing [3]-[6]. This method, however, is time-consuming, cumbersome, and provides little insight into the circuit level implications of RTN. Inferring circuit level parameters based on device I-V data is prone to error due to the fast signal switching and complex circuit topology Furthermore, due to the limited sensitivity of prior circuit based approaches, accelerated stress had to be applied in many experiments to amplify the RTN signal. This practice significantly undermines the confidence and applicability of the test results. Circuit based RTN characterization methods are therefore developed. The RTN impact on SRAM is generally monitored through observing the V<sub>min</sub> shift. However, RTN induced V<sub>min</sub> shift is so small that very few SRAM cells are within that failure margin making it difficult to be detected. As for logic circuits, very few attempts have been made to assess the true RTN impact. This, we believe, is primarily due to the difficulty of taking high precision

measurements in a short measurement time from realistic circuits such as Ring OSCillators (ROSCs).

|                       | Probing                                                                                                   | Circuit based methods                                                                           |                                                                                                                     |  |

|-----------------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

|                       | Individual transistor                                                                                     | SRAM                                                                                            | Logic circuit or<br>ring oscillator                                                                                 |  |

| Schematic             |                                                                                                           |                                                                                                 |                                                                                                                     |  |

| Parameter of interest | DC current                                                                                                | SRAM V <sub>min</sub>                                                                           | Frequency shift                                                                                                     |  |

| Pros                  | 1. Simple<br>2. High resolution                                                                           | 1. Realistic RTN<br>impact on SRAM V <sub>min</sub><br>2. Short test time<br>3. Small test area | <ol> <li>Realistic RTN impact<br/>on circuit frequency</li> <li>Short test time</li> <li>Small test area</li> </ol> |  |

| Cons                  | <ol> <li>Long test time</li> <li>Large test area</li> <li>Limited insight on<br/>circuit level</li> </ol> | <ol> <li>Limited resolution</li> <li>Rare occurrences</li> <li>Averaging effect</li> </ol>      | 1. Limited resolution<br>2. Long meas. time<br>3. Averaging effect                                                  |  |

#### Figure 2.1: Comparison of different RTN characterization techniques.

For efficient collection of large RTN statistics, several logic circuit based approaches have been demonstrated for RTN measurements. The metastable behavior of a counter circuit was used in [7]-[8] to extract RTN signatures. On the modeling side, there has been a large body of work analyzing the impact of RTN on circuit parameters such as logic gate delay and SRAM noise margins [11]. For instance, a statistical timing estimation algorithm was proposed in [12] to calculate RTN induced logic delay shift for a large circuit block. However, the lack of experimental data to verify the estimation results undermines the confidence of such work. Therefore an odometer circuit with capability of high resolution and high sample rate measurement for RTN detection is implemented for accurately characterizing the RTN induced frequency shift in logic circuit.

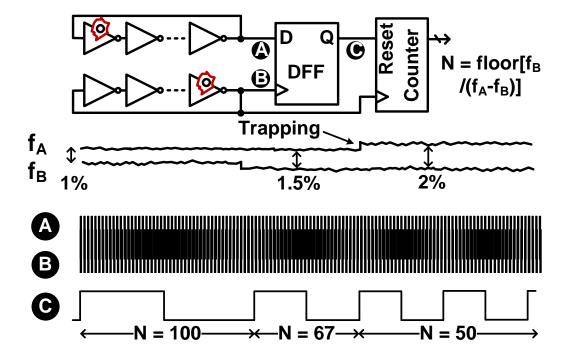

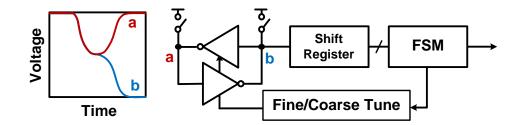

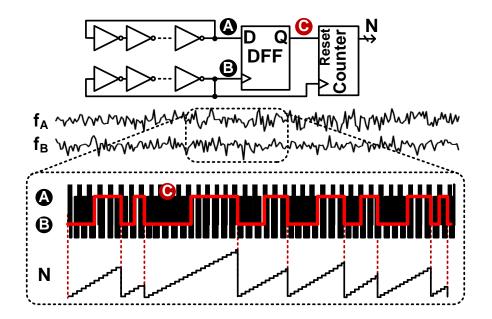

## 2.2. Beat Frequency Technique for RTN Monitoring

The basic concept of the beat frequency detection (BFD) technique for measuring the frequency difference between two ROSCs is illustrated in Figure 2.2 [13]. ROSCs are widely used evaluating process variation and reliability issues in logic circuits since they are able to provide circuit designers a straightforward estimation on circuit performance. The beat frequency detector samples the output of one oscillator using a D flip-flop at intervals set by the output of the other. The faster signal A catches up and then overtakes the slower signal B, and as this process repeats, the time between the overlapping points is the period of the beat frequency. This time is measured by counting the number of reference ROSC periods during a single beat period (i.e.  $N=floor(f_B/(f_A-f_B)))$ ). This information is then read out through a scan-based interface. The advantage of this technique is that the measurement resolution can be made very high by bringing the two frequencies  $f_A$  and  $f_B$  closer to each other. For example, when the initial frequency difference is calibrated to be 1%, the initial count output is 100. With a RTN trapping event on ROSC B which increase the frequency difference to 1.5%, the count output changes from 100 to 67. Therefore, the minimum frequency measurement resolution, corresponding to a count change from 100 to 99, is 0.01%. Further details on how to calculate the actual % frequency shift based on the scanned data can be found in the

previous publication [13]. The beat frequency approach enables us to measure changes in transistor switching times as small as one part in 10,000 in less than a microsecond, making it ideally suited for characterizing RTN effects in logic paths.

Figure 2.2: Beat frequency detection circuit adopted in this work for measuring RTN induced delay shifts at sub-0.5V supply voltages with high resolution. The output count N represents the number of  $f_B$  clock cycles that can fit within a single beat frequency (i.e.  $f_A$ - $f_B$ ) clock period.

## 2.3. Characterizing RTN with a Single Array Structure on a

## **65nm Process**

#### 2.3.1. RTN Monitor Design

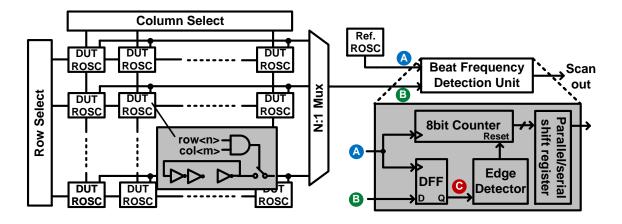

Figure 2.3: ROSC array test chip for RTN measurements comprising an on-chip beat frequency detection

The top level diagram of the 65nm test vehicle is shown in Figure 2.3. It consists of a 10x8 ROSC array, a reference ROSC, and a beat frequency detection unit. Each ROSC has only 11 inverter stages to ensure high RTN sensitivity by minimizing the averaging effect. Prior to the testing, the initial frequency difference between the DUT and reference ROSCs is set to be around 1% (i.e. output count = 100) using on-chip trimming capacitors. This initial setting was found to provide a sufficiently high measurement resolution (= 0.01%) with minimal noise effects. One DUT ROSC is selected at a time for the frequency measurements using column and row select signals. Output signal of

the selected DUT ROSC drives the bitline signal which is multiplexed out and fed to the D flip-flop inside the beat frequency detection unit.

|                           | Single ROSC                                 | DFF Sensor [8]                                                | This Work                                             |  |

|---------------------------|---------------------------------------------|---------------------------------------------------------------|-------------------------------------------------------|--|

| Circuit<br>Schematic      | Counter                                     | Counter                                                       |                                                       |  |

| Description               | Simple ROSC with<br>frequency divider       | D flip-flop driven by<br>a simple ROSC to<br>metastable state | Differential ROSC structure, beat frequency detection |  |

| Freq. Meas.<br>Resolution | Low resolution,<br>sensitive to V, T drifts | Pass/fail information only                                    | High resolution, immune to V, T drifts                |  |

| Sampling<br>Time*         | ~ 100µs                                     | N/A                                                           | > 1µs**                                               |  |

| Capable of<br>Measuring   | N/A<br>(no reported RTN data                | Single trap only                                              | Multiple traps                                        |  |

| Source(s)<br>of RTN       | using this method)                          | ROSC and DFF                                                  | ROSCs                                                 |  |

| Output                    | Actual ROSC freq.<br>shift                  | Input frequency divided by 2 or 3                             | Actual ROSC freq. shift                               |  |

\* For a 0.01% frequency shift resolution and a ROSC period of 10ns \*\* Emission and capture times down to several microseconds can be measured

# Figure 2.4: Comparison of three ROSC based RTN measurement techniques.

For a better understanding, Figure 2.4 compares three ROSC based RTN measurement structures including the proposed technique. A ROSC with a frequency divider can be considered, however, this single-ended configuration suffers from large measurement noise in the presence of voltage fluctuations and temperature drifts. To the best of our knowledge, there haven't been any reports showing RTN data based on this simple approach. Another method for measuring RTN is illustrated in Figure 2.4 where a frequency divider in a metastable state is used [8]. The divider's output frequency switches between f/2 and f/3 according to the RTN capture and emission times. Here, f is

the input frequency. The main drawback of this approach is that it is hard to infer physical parameters such as frequency or  $V_{th}$  based on the erratic divider output. The beat frequency scheme, on the other hand, can measure the exact frequency shift due to single or multiple RTN traps with high precision and short measurement time, making it an effective characterization method for RTN effects in logic circuits.

2.3.2. RTN Induced Frequency Shift Measurements on 65nm Test Chip

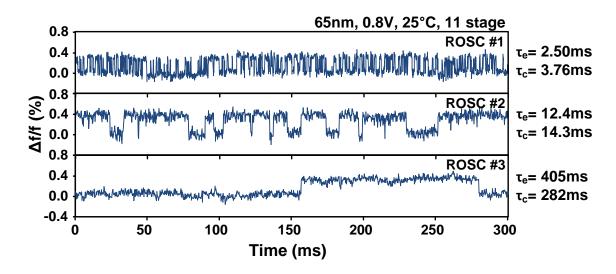

Figure 2.5: Single trap RTN waveforms measured from different ROSCs.

The frequency shift waveforms in Figure 2.5 are from three different ROSCs in the test array. RTN's signature trapping/de-trapping behavior can be clearly observed. Independent of the time constant values, the frequency shift caused by a single RTN trap was approximately 0.4% for the 11 stage ROSC operating at 0.8V and 25  $\$ . Our repeated experiments revealed no RTN in the reference ROSC, although this is purely a statistical occurrence. Due to the identical layout and physical proximity, there is no reason to believe that the chances of having an RTN trap in the reference and DUT

ROSCs will different. The emission and capture time constants (i.e.  $\tau_e$  and  $\tau_c$ ) range from 2.50ms to 405ms depending on the supply voltage and ROSC instance.

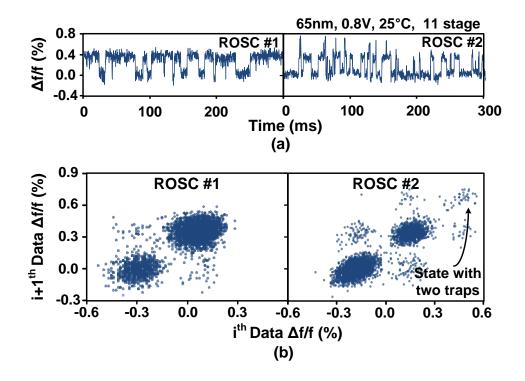

Figure 2.6: (a) Single and multi-trap RTN waveform from two different ROSCs. (b) Time Lag Plot (TLP) of the two traces.

Figure 2.6(a) shows frequency traces of two ROSCs having a single trap and two traps, respectively. The maximum frequency shift induced by two traps is 0.8%, which is almost twice as large as the single-trap one indicating a state in which both traps are in capturing event. But as indicated from the waveform, the time constant at 0.8% freq. shift is relatively smaller than the other two states which makes it difficult to be recognized. A Time Lag Plot (TLP) therefore is proposed [14] for a better visualization of the capturing and emission transitions as shown in Figure 2.6(b). This method plots each sampled points on a plane indicating its current state and the relationship to the next point's state.

As shown in these two TLPs, a single trap has only one capture and one emission state while two trap RTN has three clusters on the diagonal.

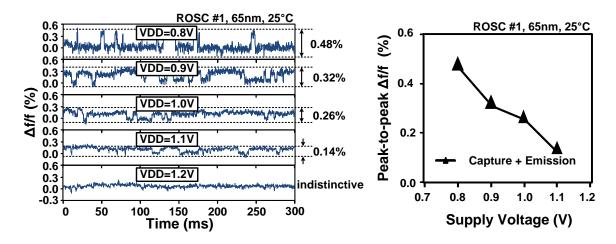

Figure 2.7: RTN traces from same ROSC at different supply voltages.

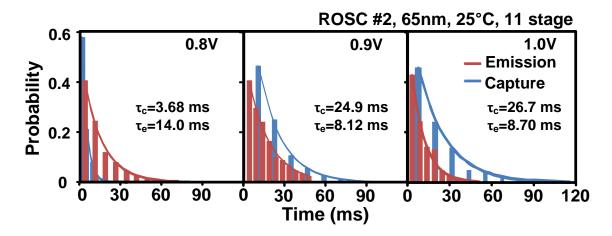

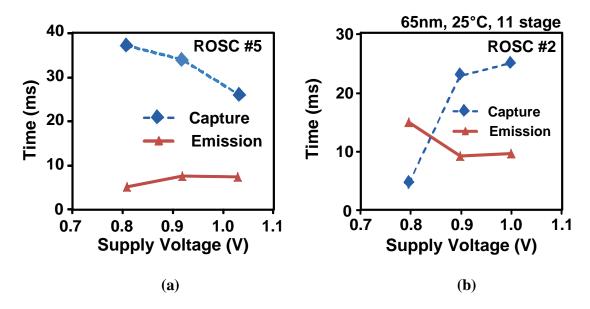

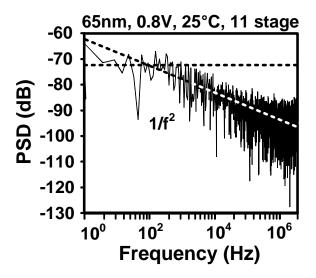

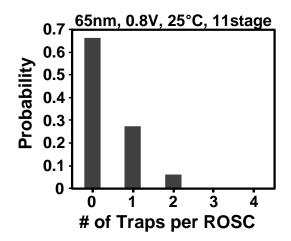

RTN parameters are shown to have a strong voltage dependence which was experimentally verified from the test chip (Figure 2.7). As the supply voltage is increased from 0.8V to 1.1V, the RTN induced frequency shift decreases from 0.48% to 0.14%. Eventually, RTN becomes indistinctive at 1.2V, the nominal operating voltage of this process. These results are in line with previous studies that have reported a stronger RTN signal at lower supply voltages [14]. RTN time constants are defined as the average time a trap site stays in the occupied state or in the unoccupied state. The capture ( $\tau_c$ ) and emission ( $\tau_e$ ) time constants can be extracted using an exponential model which agrees well with the measured data as shown in Figure 2.8. The distribution of the capture and emission times distribution spreads out as the supply voltage is increased from 0.8V to 1.0V indicating an increase of capture time constant. And the emission time distributions show opposite dependence. For a better understanding we extrapolated the capture and emission time constants in term of supply voltage as shown in Figure 2.9. The capture time constant shown in the Figure 2.9(a) decreases as the supply voltage is increased indicating an RTN trap on a NMOS. Whereas for RTN trap located on the PMOS, as shown in Figure 2.9(b), the capture time increase with the voltage. The Power Spectrum Density (PSD) of a DUT ROSC with a single trap is shown in Figure 2.10. The spectrum follows a Lorenzian with a corner frequency at ~10ms which is in accordance with the RTN capturing and emitting time constants. Histogram of the numbers of RTN traps per ROSC is shown in Figure 2.11. 66% of the ROSCs did not show any signs of RTN while no ROSC had more than 2 traps. The relatively low number of traps in each ROSC can be attributed to the mature process technology used for the test chip fabrication.

Figure 2.8: Capture and emission time distributions and exponential fit results for supply voltage from 0.8V to 1.0V.

Figure 2.9: Time constants versus supply voltages.

Figure 2.10: Power Spectrum Density (PSD) of the frequency shift data.

Figure 2.11: Histogram of the number of traps per ROSC.

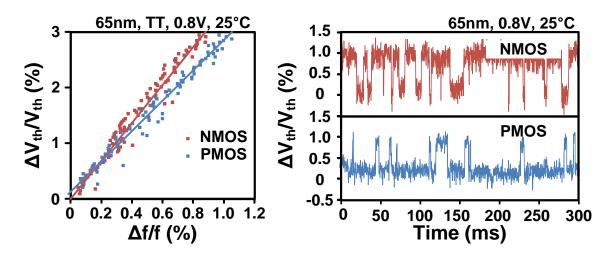

Figure 2.12: Frequency to V<sub>th</sub> mapping.

For a better understanding, we simulated an 11 stage ROSC with HSPICE and translated the measured frequency data back to the device  $V_{th}$  using the mapping curve as shown in Figure 2.12. RTN induced  $V_{th}$  shifts can be estimated from the measured frequency shift data with linear fitting. The transient waveforms in terms of  $V_{th}$  shift with respect to NMOS and PMOS are shown on the right. It indicates that single trap induced  $V_{th}$  shift in NMOS is 1.9% compare to 1.6% in PMOS. The dependence of frequency

shifts on  $V_{th}$  shifts with different supply voltage is simulated and shown in Figure 2.13(a). RTN induced  $V_{th}$  shifts with different supply voltages is translated from the measurement data. The transient waveform in Figure 2.13(b) indicates that the same trap induced  $V_{th}$ shifts reaches maximum at 0.9V. But for frequency shift, as shown earlier, the maximum value is achieved at 0.8V. This discrepancy implies that both the absolute  $V_{th}$  shift value and the parametric dependences should be considered when evaluating the RTN impact on logic circuit frequency shift.

Figure 2.13: RTN induced V<sub>th</sub> shift with different supply voltage.

# 2.4. Characterizing RTN with a Dual Array Structure on a 32nm HKMG Process

With scaling of VLSI technology, the transistor feature size is halved every generation however the supply voltage is scaled at a slower rate. The power density therefore is expected to grow in future technology nodes. On the other hand, the chip cooling capability remains the same which limits the number of simultaneously switching transistor per area [17]. One solution is to utilize the Near Threshold Voltage (NTV) technique which improves the energy efficiency by decreasing the supply voltage to a near threshold region [18]. A major challenge for NTV operation is the higher sensitivity to parametric variations as compared to a nominal operation condition. RTN induced frequency shift in logic circuit at lower supply voltage, as we proved in the previous section, is expected to be more severe than that at a higher voltage. For a better understanding of the RTN impact on circuit performance at a NTV operation, we proposed a dual array structure RTN monitor which is capable of characterizing RTN induced frequency shift in logic circuit in a sub-0.5V region.

The main contribution of this work is that we present detailed RTN induced frequency fluctuation data collected from a 32nm test chip operating at supply voltages as low as 0.45V. One of the main shortcomings of the previous design is that the resolution degrades sharply at low supply voltages due to increased variation between ROSC frequencies, which makes the BFD technique less accurate. Note that RTN effects become more severe at low supply voltages due to the Fermi level change and higher circuit sensitivity. To overcome this limitation, this work proposes a dual ROSC array based test structure which achieves a frequency measurement resolution less than 0.01% for every single ROSC in the array for supply voltages down to 0.45V.

#### 2.4.1. Dual Ring Oscillator Array Technique

Figure 2.14: Limitation of prior art. Due to the wide frequency spread, not all ROSCs under test can achieve high measurement resolution at sub-0.5V supply voltages.

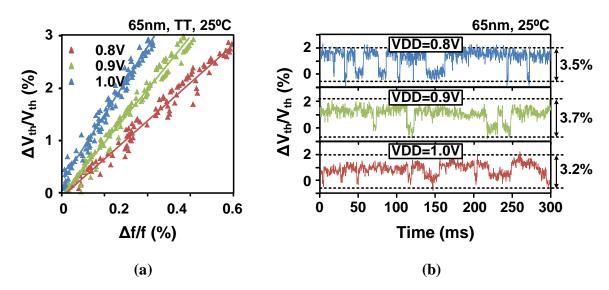

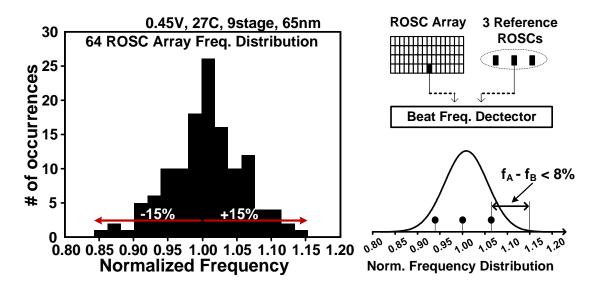

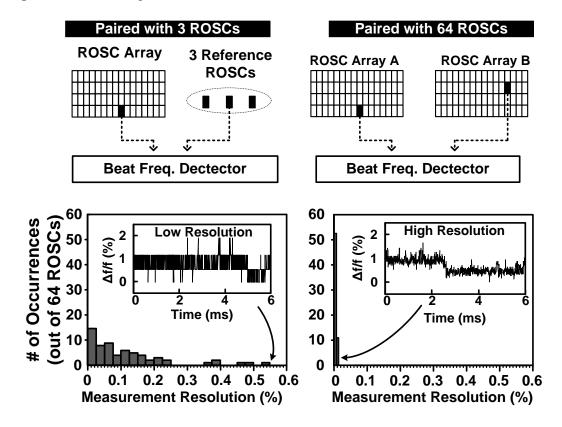

When a large number of ROSCs need to be measured at low supply voltages however, due to process variation between ROSCs, a small frequency difference (e.g. <1%) between the two ROSCs cannot always be guaranteed. This can be seen in Figure 2.14 where the frequency variation of 64 ROSCs can be as high as +/-15% at 0.45V. In the previous design the ROSC test array is paired with three reference ROSCs, the frequency difference can be as high as 8% which limits the frequency measurement resolution to >0.6% which is not sufficient for precise RTN measurements. Tuning the frequency of individual ring oscillators using dedicated hardware is not desirable since the tuning circuit itself may introduce RTN noise. Furthermore, adding tuning circuits will make the ROSC less representative and increase the sensitivity to common-mode effects such as temperature and voltage drifts.

Figure 2.15: Measurement resolution comparison when pairing a 64 ROSCs with 3 reference ROSCs (left figure) and 64 reference ROSCs (right figure). A more precise waveform can be reconstructed using 64 reference ROSCs which is critical for collecting high quality RTN statistics at low supply voltages such as 0.5V.

To overcome this limitation, in this work, we propose a dual-array test structure, which guarantees that a ROSC from the main array can be paired with a ROSC from another array with a frequency difference less than 1%. This ensures a frequency measurement resolution of less than 0.01% even in the worst case. As shown in Figure 2.15, as the number of reference ROSCs increases from 3 to 64, the worst-case

measurement resolution is improved from 0.5% to 0.01% for the proposed dual ring oscillator array configuration. Test chip results in Section 2.4.2 indicate that a frequency resolution of 0.05% is attainable which is significantly less than the frequency shift induced by a single RTN trap.

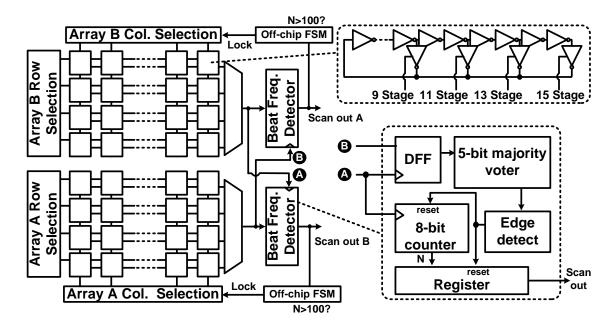

Figure 2.16: Block diagram of the proposed dual ROSC array based RTN characterization circuit. By pairing ROSCs from two arrays, the beat frequency detection circuit can achieve a frequency measurement resolution less than 0.01%. The number of inverter stages can be configured from 9 to 15 using scan bits.

Figure 2.16 shows further details of the 32nm test chip. It consists of two identical ROSC arrays, each comprising 64 ROSCs, along with two separate beat frequency detectors to determine which of the two input frequencies is higher. A 5 bit majority voter circuit is used to prevent functional errors caused by logic bubbles (e.g. lone 0 in a string of 1's and vice versa) which are likely to occur when the two ROSC edges are very close

to each other. A ROSC in one array is sequentially paired with a ROSC in the other array until the BFD count falls within the desired range (e.g. >100). A finite state machine sends out a 'lock' signal to freeze the column and row selection signals, and then the frequency difference is measured and scanned out. The pairing process takes no more than 100  $\mu$ s using our automated test setup. ROSCs are designed with programmable number of stages (i.e. 9, 11, 13, and 15) to study the impact of the number of inverter stages on the amount of RTN induced frequency shift. PMOS and NMOS transistors used in the ROSC circuit have a width of 624nm and a length of 56nm. The new test structure is well suited for Bias Temperature Instability (BTI) stress experiments since the ROSC can be configured as an open-loop inverter chain using tri-gate stages.

#### 2.4.2. RTN Induced Frequency Shift Measurements on 32nm Test Chip

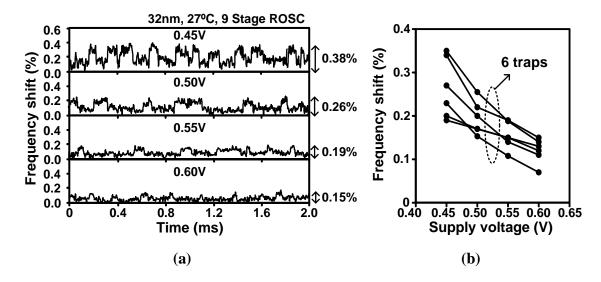

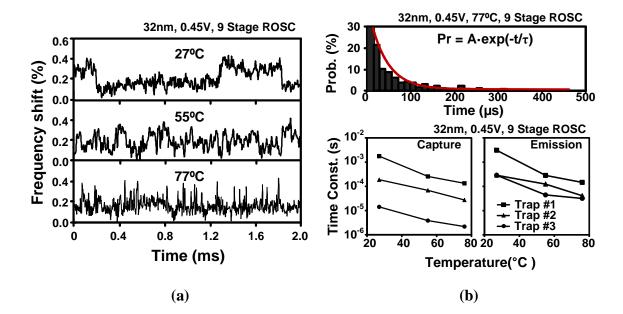

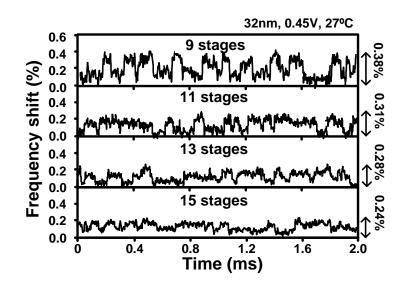

The proposed dual-array based RTN monitor was fabricated in a 32nm high-k metalgate process. The nominal supply voltage of this technology is 0.9V. Figure 2.17(a) shows frequency shift traces of a 9 stage ROSC from 0.45V to 0.6V. Measurements show the signature RTN behavior caused by trapping and de-trapping events. The measured RTN induced frequency shift decreases from 0.38% to 0.15% as the supply voltage is increased from 0.45V to 0.6V. The telegraph-shaped RTN waveform was not appreciable at supply voltages higher 0.6V. This suggests that RTN is not a major issue at the nominal supply voltage, but will become more significant when the supply is lowered to near-threshold voltages. The magnitude of frequency shift due to RTN measured from 6 different ROSCs is shown in Figure 2.17(b). Variation in RTN induced frequency shift can be attributed to the different trap locations in the gate oxide [15]. The frequency shift monotonically decreases at higher supply voltages. One possible reason for this is that ROSC frequency is more sensitive to the same Vth change at lower supply voltages due to the lower gate overdrive voltage. Figure 2.18(a) shows the frequency shift waveforms at 27 °C, 55 °C, and 85 °C. The magnitude of the frequency shift shows little dependence on temperature, however trapping and de-trapping occur more frequently at higher temperatures which is in line with previous studies. RTN time constants are defined as the average time a trap site stays in the occupied state or in the unoccupied state. The capture ( $\tau_c$ ) and emission ( $\tau_e$ ) time constants can be extracted using an exponential model fitted to the measured distribution, as shown Figure 2.18(b) (upper). Theoretically, the proposed BFD can measure time constants shorter than a microsecond. However, due to the slow data scan out, the minimum time constant measureable by our design is a few microseconds. The maximum time constant we can measure is limited only by the measurement time. To study the impact of logic depth on frequency shift, we first selected a ROSC with an RTN trap and then varied the number of stages using scan signals. Experimental data in Figure 2.19 shows that as the number of stages increases from 9 to 15, the frequency fluctuation reduces from 0.38% to 0.24% for the same RTN trap due to the lower sensitivity.

Figure 2.17: (a) RTN induced frequency shift traces measured at different voltages.(b) Magnitude of frequency shift of 6 RTN traps measured at different voltages.

Figure 2.18: (a) RTN induced frequency shift due to the same trap measured at different temperatures. (b) Capture and emission time constants both decrease at higher temperatures.

Figure 2.19: RTN induced frequency shift versus the number of ROSC stages. The frequency shift caused by the same RTN trap is reduced as the number of stages increases.

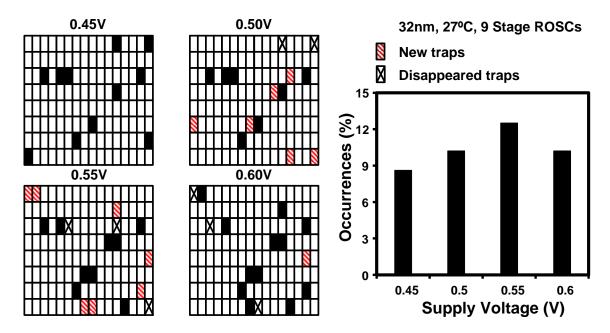

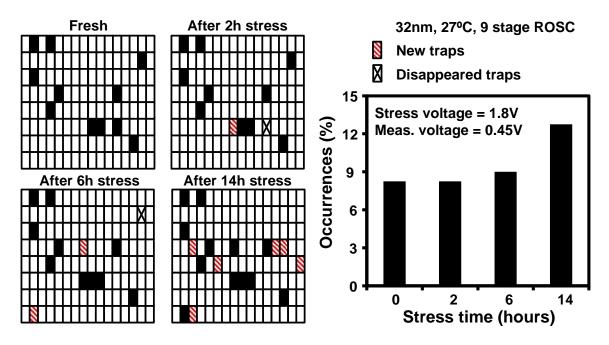

Figure 2.20 shows the occurrence and location of RTN traps across a single test chip from 0.45V to 0.6V. RTN traps may appear or disappear as the supply voltage is varied which we suspect is due to the Fermi level shift [15]. That is, the RTN trap is more likely to be detected if the trap energy level and the Fermi level are closely aligned. The number of ROSCs affected by RTN remained relatively constant under different supply voltages.

Both RTN and BTI have been reported to originate from the same defect sources [16]. To understand the interplay between RTN and BTI better, we measured the location and occurrence of RTN while applying a voltage stress to the ROSC array. The ROSC frequencies were sampled periodically at 0.45V while the test chip was subject to a 1.8V voltage stress (=2x the nominal  $V_{DD}$ ) for 14 hours. Stress results in Figure 2.21 reveal several newly generated RTN traps as well as few annealed traps. The former can be

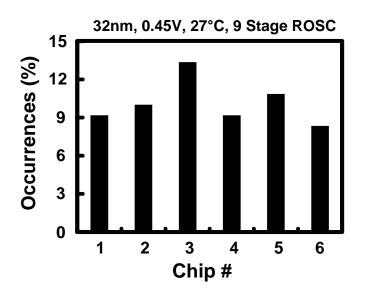

attributed to defects created during BTI stress while the latter may be related to the BTI recovery phenomenon [16]. The higher occurrence rate with longer stress time implies that RTN along with BTI further degrades the circuit long-term performance. The percentage of ROSCs affected by RTN measured from 6 different chips is shown in Figure 2.22.

Figure 2.20: RTN trap location map measured at different supply voltages. Each cell represents a single ROSC.

Figure 2.21: RTN trap location map measured after 0, 2, 6 and 14 hours of 1.8V stress.

Figure 2.22: RTN occurrences measured from 6 different chips.

#### 2.4.3. RTN Impact on Logic Timing

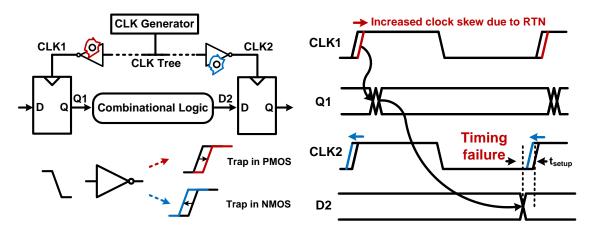

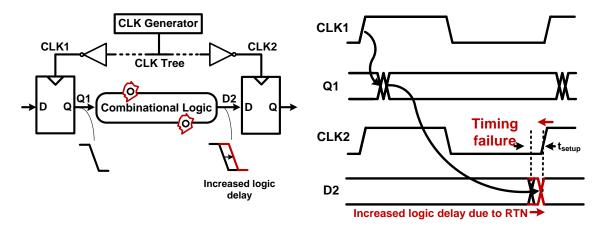

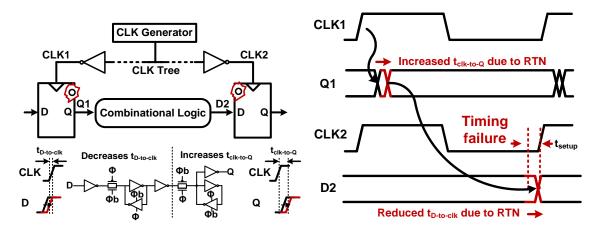

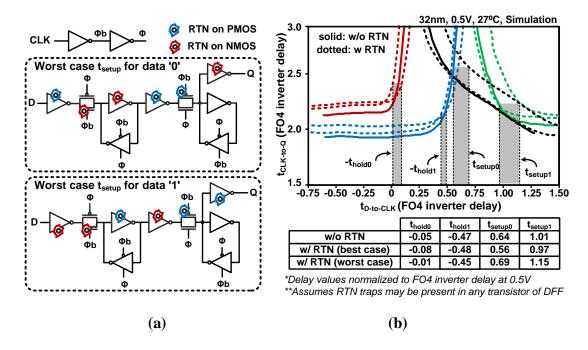

To estimate RTN induced delay shift in circuits other than simple inverters, we first translated the frequency shift measured from the 32nm test chip to V<sub>th</sub> shift using the frequency versus Vth relationship simulated in SPICE. Then we apply the Vth shift to various logic gates and D flip-flops (DFFs). We have evaluated three possible RTN induced timing violations in a typical pipeline circuit. Setup time violation is illustrated in Figure 2.23 in the presence of RTN traps in the clock tree. In the worst case, the launching clock CLK1 arrives late and the sampling clock CLK2 arrives early due to RTN. This introduces a skew between CLK1 and CLK2 which reduces the available time for logic computation. The second scenario is shown in Figure 2.24 where the combinational logic delay increases due to RTN. Finally, as shown in Figure 2.25, RTN in the DFF can affect setup and hold times. For better understanding, Figure 2.26(a) shows that the worst case DFF setup time occurs when traps appear in alternating PMOS and NMOS devices on the signal path from D to Q. Figure 2.26 (b) displays the D-to-CLK and CLK-to-Q delays with and without RTN. Since RTN becomes more appreciable at low supply voltages, our simulations are performed at 0.5V. It can be seen that in the presence of RTN, the setup time and hold time curves shift either to the right or left depending on the location of the RTN trap. The setup time varies by -0.08 to 0.18 FO4 inverter delays with RTN.

Figure 2.23: Logic timing errors for RTN traps located in clock tree.

Figure 2.24: Logic timing errors for RTN traps located in combinational logic.

Figure 2.25: Logic timing errors for RTN traps located in flip-flop.

Figure 2.26: (a) RTN trap location on DFF signal path for worst case setup time (hold time is opposite location). No traps assumed on clock path. (b) RTN impact on D-flip-flop setup and hold times.

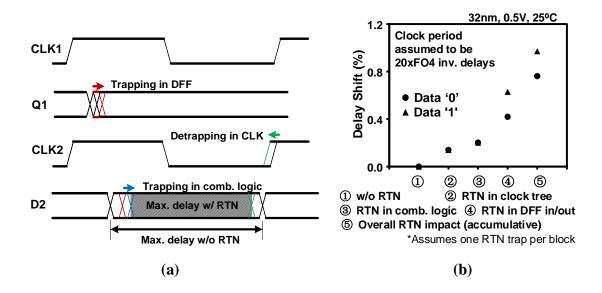

The following discussion will focus on setup time violation. A similar analysis can be performed for hold time violation. As shown in Figure 2.27(a), to operate without any logic errors, the clock period  $T_{clk}$  must be greater than  $t_{clk-to-q} + t_{logic} + t_{setup} + t_{clk_skew}$ . Figure 2.27(b) compares the max-delay time under different RTN scenarios. In the absolute worst case, traps may be present in the input and output DFFs as well as the clock tree and logic path. The max-delay time allowed for correct operation is reduced by 0.21 FO4 inverter delays under this worst-case condition.

Figure 2.27: RTN impact on logic path delay assuming a clock period of 20 FO4 inverter delays and one RTN trap in each block (i.e. logic path, clock tree, input DFF, and output DFF).

The following two factors have been incorporated for estimating RTN induced timing errors of a large circuit: (1) the frequency shift magnitude of an individual trap, and (2) the spatial distribution of traps. The probability of RTN induced timing errors for a given timing guard band x can be expressed as:

Pr(Timing error | guard band = x)

$$= \frac{1}{2} \left[ 1 - \sum_{i,j,k} \Pr(N_{clk} = i) \cdot \Pr(N_{data} = j) \cdot \Pr(N_{DFF} = k) \right]$$

$$\forall i, j, k : \Delta t_{skew} (N_{clk} = i) + \Delta t_{data} (N_{data} = j) + \Delta t_{DFF} (N_{DFF} = k) \le x$$

Here, Nclk, Ndata and NDFF represent the number of traps in the clock tree, combinational logic, and DFF, respectively. To prevent RTN induced timing errors, it is required that the guard band x should be greater than the total delay shift ( $\Delta t_{skew}$ +  $\Delta t_{data}$ +

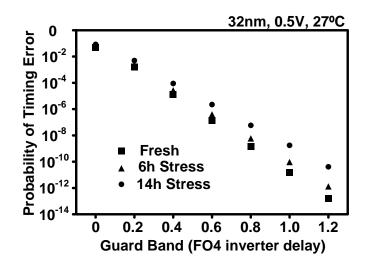

$\Delta t_{DFF}$ ) of the critical path. Here, we assume the probability of a trap being present in a transistor is independent and identically distributed, and follows the spatial probability measured from the 32nm test chip. The magnitude of RTN induced Vth shift can be modeled using a log-normal distribution [19]. However, for simplicity, Eq. (1) assumes that all RTN traps have the same Vth shift that is equal to the measured average value. We also assume that at any given moment, half the traps are in capture state and half are in emission state. A separate in-depth study will be needed to fully capture Vth shift variation and spatial distribution effects. Based on Eq. (1) and the above-mentioned simplifications, the estimated probability of timing errors for circuit before and after BTI stressed is shown in Figure 2.28. For a fresh circuit, the probability of timing errors due to RTN will be reduced to less than 10<sup>-12</sup> with a guard band of 1.2 FO4 delay. The number of traps increases with longer BTI stress and therefore the number of RTN induced timing errors increases accordingly.

Figure 2.28: Probability of setup time violation versus timing guard band.

#### 2.4.4. RTN Impact on SRAM Stability and Timing

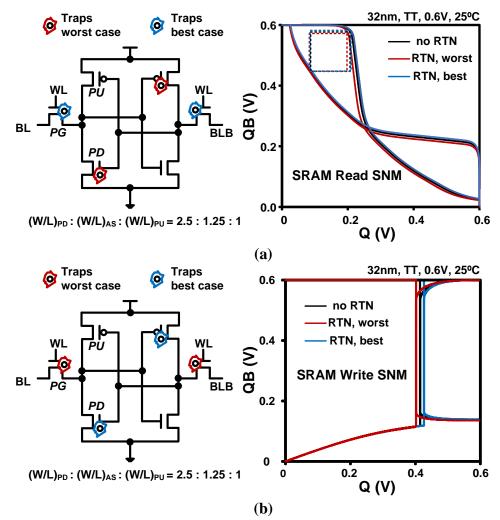

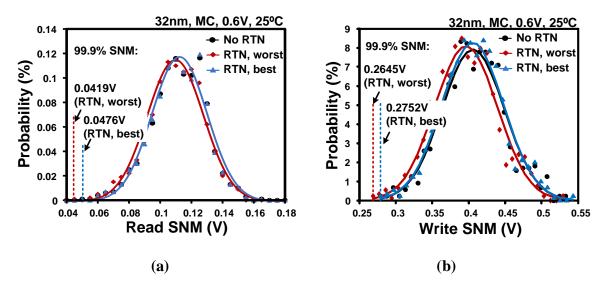

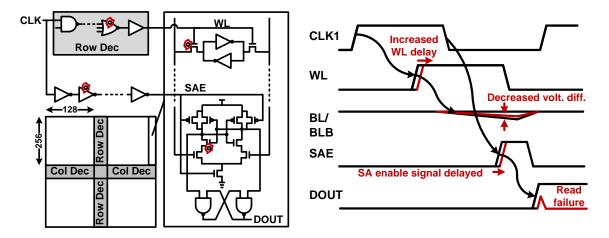

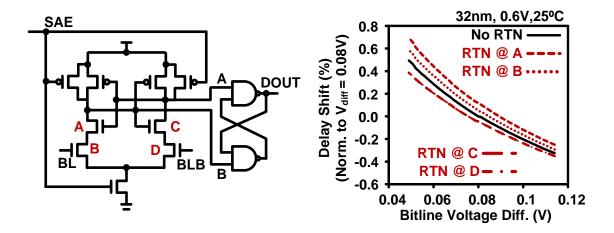

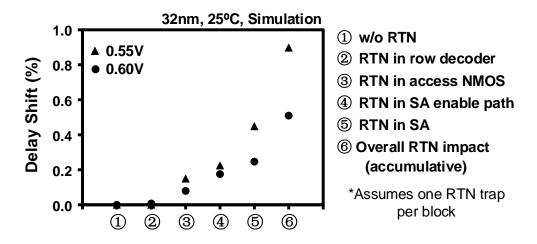

A 6T SRAM cell is shown in Figure 2.29. RTN either improves or worsens the read margin depending on the trap location inside the SRAM cell. The read margin is determined primarily by the relative strength between the pull down NMOS transistor (PD) and the pass gate (PG). In the worst case, the diagonal PD and PU transistor pair becomes weaker while PG becomes stronger due to multiple RTN traps. Figure 2.29(b) shows the RTN impact on SRAM write SNM. Read SNM and write SNM move in opposite directions for the same RTN trap. The worst case for write happens when RTN trapping occurs in PG. For better illustration, we ran Monte Carlo simulations on SRAM read and read SNM under a 0.6V supply voltage assuming random trap locations. As shown in Figure 2.30, with RTN, the 99.9 percentile read SNM and write SNM are reduced by 12% and 3.9%, respectively. Next, we analyze how the SRAM read path delay, namely the CLK to DOUT delay, is affected by RTN. Figure 2.31 shows the schematic and timing diagram of a 128Kbit SRAM subarray used in this discussion. Firstly, when RTN traps are present in the column decoder, the CLK to WL delay increases causing the read delay to increase. Similarly, read delay may increase due to RTN traps in the sense amplifier enable signal (SAE) generation path. The worst case read delay occurs when the trap is located in the PG transistors because SRAM read speed is determined by the read current. Finally, RTN in the sense amplifier may degrade the resolving time. Figure 2.32 shows a typical latch based sense amplifier. When BL is discharged, traps on transistors 2 and 3 increase the SAE to DOUT delay while traps on transistors 4 and 5 decrease the delay. RTN has a stronger impact on sense amplifier delay for smaller bitline voltage differences.

Figure 2.29: RTN impact on SRAM (a) read SNM and (b) write SNM.

Figure 2.30: Monte Carlo simulations of SRAM (a) read SNM and (b) write SNM, with and without RTN.

Figure 2.31: RTN impact on SRAM read timing.

To capture the above discussion, we simulated the CLK to DOUT delay of a realistic 128Kbit SRAM sub-array in 32nm technology assuming traps in different locations. As shown in Figure 2.33, traps located in the column decoder show negligible impact on the overall read delay while traps in the sense amplifier have a greater impact. Assuming one

trap each in the column decoder, SRAM access transistor, sense amplifier, and SR latch, the read delay increases by 0.96% at 0.6V and by 9.3% at 0.55V.

Figure 2.32: RTN impact on sense amplifier resolving time.

Figure 2.33: RTN impact on SRAM read path delay.

# 2.5. Conclusion

The impact of random telegraph noise on ring oscillator (ROSC) frequency was measured for the first time using an on-chip beat frequency detection system. The proposed differential sensing scheme achieves high measurement resolution and short measurement time was first demonstrated in a 65nm LP process. Experimental data from the test chip displays both single trap and multi-trap RTN behavior. The voltage dependencies of the frequency shift and capture/emission times were measured and analyzed. For a more accurate characterization of the impact of random telegraph noise (RTN) on logic timing margin under sub-0.5V supply voltages, a novel method utilized dual ring oscillator array test structure was fabricated in a 32nm HKMG technology. The new test structure improves the frequency measurement resolutions of the tested-andproven beat frequency detection (BFD) technique by pairing a ROSC from one array with a ROSC from a second array having a similar frequency. It enables fully-automated collection of RTN statistics with high measurement accuracy at supply voltages as low as 0.45V. The magnitude and occurrences of RTN induced ROSC frequency shift were measured across different supply voltages, temperatures, and voltage stress conditions. Based on the measured frequency shift data, we estimated the RTN impact on logic timing margins and SRAM performance.

# Chapter 3. Compact High-Sensitivity Radiation Sensor Array

## **3.1. Introduction**

Recent studies have shown that Soft Error Rate (SER) per memory bit is steadily decreasing with technology scaling due to the commensurate reduction in junction area [22]-[26]. Furthermore, SER in FinFET technologies is expected to be 5-10x less than that in planar technologies due to the smaller geometrical contact area between the diffusion and substrate regions [25]. As a result, collecting statistically significant amount of SER data in advanced technologies such as FinFET has become a challenging task, requiring massive number of test circuits exposed to a radiation source for long periods of time. Extracting model parameters from limited number of SEU and SET events results in model inaccuracies. Extrapolating SER based on data collected at low supply voltages can lead to unrealistic SER projections.

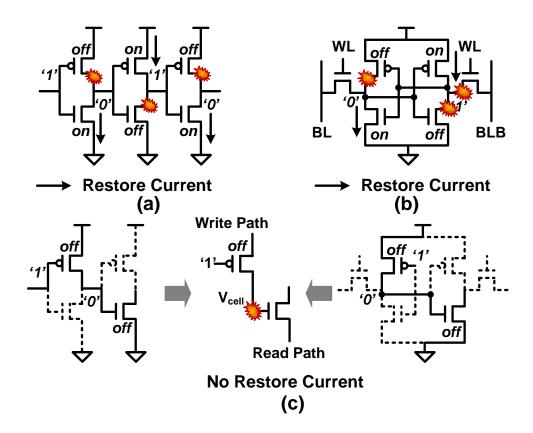

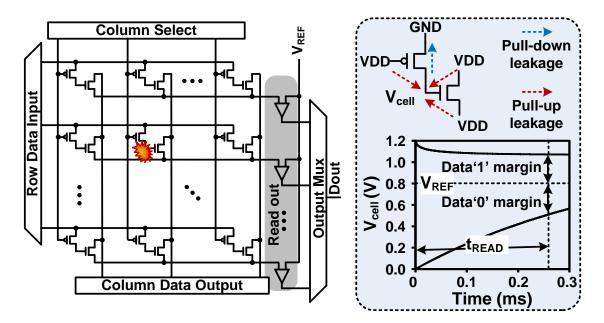

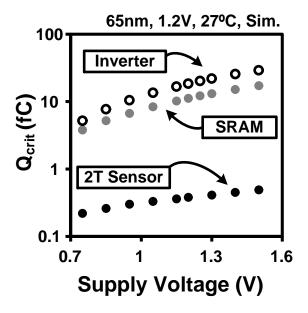

To overcome these limitations, we present a compact 2 Transistor (2T) radiation sensor array with a high sensitivity to radiation strikes. The proposed sensor circuit has a critical charge ( $Q_{crit}$ ) that is more than 10 times smaller compared to a 6T SRAM. This is achieved by eliminating the restore current and minimizing the node capacitance. Alpha particle experiments show that the proposed 2T sensor can detect many strikes that would have otherwise gone undetected in a standard 6T SRAM test structure. The higher sensitivity to particle strikes and dense area makes the proposed 2T sensor an effective tool for performing detailed radiation studies.

### 3.2. 2T Sensor Array

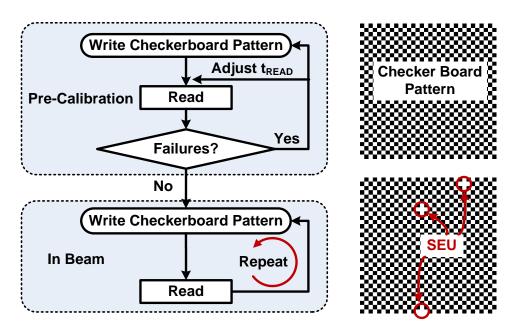

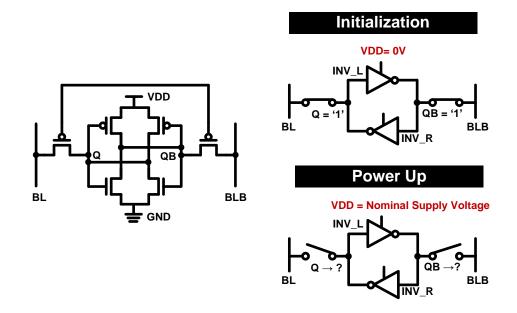

In terms of CMOS transistor, soft errors typically occur when the particle strikes the device diffusion area [26][27]. The most sensitive area is generally the drain of an 'off' state transistor. As shown in Figure 3.1(a) and (b), the susceptible nodes are the drains of the alternating PMOS and NMOS along an inverter chain, or the storage nodes in a 6T SRAM cell. SET occurs in combinational logic when the particle induced a sufficiently large current or voltage pulse, e.g. greater than an inverter trip point, to propagate through the logic chain. SET may gradually diminish while propagating along the logic chain, however if the pulse is captured by a latch or DFF then an error occurs. SEU, on the other hand, occurs in a single memory cell which directly lead to a data flip. Not all particle strikes will result in an SEU or SET, it largely depends on the particles energy, strike location and angles, circuit topology and so on. Two parameters are widely used to characterize the single event effects [1].

1) Collected charge ( $Q_{coll}$ ) is defined as the total charge created by a radiation event at the vicinity of the junction. The amount of  $Q_{coll}$  largely depends on the characteristic of the particles and its interaction with the materials. Typical value of  $Q_{coll}$  ranges from less than 1 fC to hundreds of fC. 2) Critical charge ( $Q_{crit}$ ) is defined as the amount of charges that is required to trigger a change of the data state which primarily relies on intrinsic circuit parameters such as node capacitance, supply voltage, and restore current.