### Advancing architecture optimizations with Bespoke Analysis and Machine Learning

### A THESIS SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

Subhash Sethumurugan

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

John M Sartori

February, 2023

© Subhash Sethumurugan 2023 ALL RIGHTS RESERVED

# Acknowledgements

I sincerely thank my academic advisor Prof. John Sartori for his guidance throughout my PhD. I am grateful for his enormous support all these years. He was always available for any help or advice both professionally and personally. He constantly encouraged me to pursue any research idea that interested me without any restrictions. I am truly thankful for the opportunity and freedom. I would also like to express my gratitude to the National Science Foundation for supporting my research through the NSF grants. I would like to thank my internship mentor and collaborator, Jieming Yin, for guiding me during an important phase of my PhD. I would also like to thank my other collaborators, Kangjie Lu and Henry Duwe, without whom, my research work would not be complete.

My PhD journey would not have begun if not for the guidance and counseling from my labmate and collaborator, Hari Cherupalli. He was instrumental in all my research endeavors and had spent hours working with me on my projects, even after he had graduated from the University. I would like to convey my special thanks to Shashank Hegde, who can be considered a partner in my PhD, for having worked with me for several years. In addition to learning a lot from him, I believe my problem-solving abilities have been enhanced by our discussions and debates. I would also like to thank all my other labmates - Himanshoo Sahoo, Shaman Narayanan, Nishanth Somashekara Murthy and Tariq Azmy, for all their support.

I would like to express my gratitude to all my university friends - Karthik Srinivasan, Ramya RamaSubramanian, Abhinav Vishwanathan Sambasivan, Vaishnavi Govindarajan, Venkat Ram Subramanian, Deepak Srivatsav Sridharan, Jayasimha Bezawada and many more for making my time in Minneapolis fun and memorable. I would also like to thank my childhood friends - Ashwin, Sharath, Surya, and Nayantara for cheering me up during all the stressful times. Any of my achievements would not have been possible without the support of my wife and parents. My wife, Sarada Peruboina, is my pillar of strength and confidence. I cannot thank her enough for sharing my life and my responsibilities throughout this period. I thank my parents for encouraging, motivating, and supporting me all throughout my life to realize my goals. I would also like to thank my brother - Akash Subramaniam Sethumurugan, for his constant support.

#### Abstract

With transistor scaling nearing atomic dimensions and leakage power dissipation imposing strict energy limitations, it has become increasingly difficult to improve energy efficiency in modern processors without sacrificing performance and functionality. One way to avoid this tradeoff and reduce energy without reducing performance or functionality is to take a cue from application behavior and eliminate energy in areas that will not impact application performance. This approach is especially relevant in embedded systems, which often have ultra-low power and energy requirements and typically run a single application over and over throughout their operational lifetime. In such processors, application behavior can be effectively characterized and leveraged to identify opportunities for "free" energy savings. We find that in addition to instruction-level sequencing, constraints imposed by program-level semantics can be used to automate processor customization and further improve energy efficiency. This dissertation describes automated techniques to identify, form, propagate, and enforce application-based constraints in gate-level simulation to reveal opportunities to optimize a processor at the design level. While this can significantly improve energy efficiency, if the goal is truly to maximize energy efficiency, it is important to consider not only design-level optimizations but also architectural optimizations. That being said, architectural optimization presents several challenges. First, the symbolic simulation tool used to characterize gate-level behavior of an application must be written anew for each new architecture. Given the expansiveness of the architectural parameter space, this is not feasible. To overcome this barrier, we developed a generic symbolic simulation tool that can handle any design, technology, or architecture, making it possible to explore applicationspecific architectural optimizations. However, exploring each parameter variation still requires synthesizing a new design and performing application-specific optimizations, which again becomes infeasible due to the large architecture parameter space. Given the wide usage of Machine Learning (ML) for effective design space exploration, we sought the aid of ML to efficiently explore the architectural parameter space. We built a tool that takes into account the impacts of architectural optimizations on an application and predicts the architectural parameters that result in near-optimal energy efficiency for an application. This dissertation explores the objective, training, and inference of the ML model in detail. Inspired by the ability of ML-based tools to automate architecture optimization, we also apply ML-guided architecture design and optimization for other challenging problems. Specifically, we target cache replacement, which has historically been a difficult area to improve performance. Furthermore, improvements have historically been ad hoc and highly based on designer skill and creativity. We show that ML can be used to automate the design of a policy that meets or exceeds the performance of the current state-of-art.

# Contents

| Α            | ckno  | wledge        | ments                                                  | i    |

|--------------|-------|---------------|--------------------------------------------------------|------|

| A            | bstra | $\mathbf{ct}$ |                                                        | iii  |

| $\mathbf{C}$ | onter | nts           |                                                        | v    |

| Li           | st of | Tables        | 5                                                      | viii |

| Li           | st of | Figure        | es                                                     | x    |

| 1            | Intr  | oducti        | on                                                     | 1    |

| <b>2</b>     | Bac   | kgrou         | nd                                                     | 6    |

|              | 2.1   | Symbo         | blic Simulation Based Hardware Software Co-analysis    | 6    |

|              | 2.2   | Conse         | rvative State                                          | 7    |

| 3            | Cor   | nstrain       | ed Conservative Symbolic Hardware-Software Co-analysis | 9    |

|              | 3.1   | Conse         | rvative State Limitation                               | 9    |

|              | 3.2   | Propo         | sed Work                                               | 14   |

|              |       | 3.2.1         | Encoding Constraints From Binary                       | 15   |

|              |       | 3.2.2         | Propagating Constraints                                | 17   |

|              |       | 3.2.3         | Enforcing Constraints                                  | 18   |

|              | 3.3   | Proof         | of CCS Correctness                                     | 19   |

|              | 3.4   | Evalua        | ation                                                  | 20   |

|              |       | 3.4.1         | Analysis Time                                          | 22   |

|              |       | 3.4.2         | Exercisable Gates                                      | 23   |

|          |     | 3.4.3 Final Remarks                                                    | 25 |

|----------|-----|------------------------------------------------------------------------|----|

|          | 3.5 | Related Work                                                           | 26 |

|          |     | 3.5.1 Static Analysis                                                  | 26 |

|          |     | 3.5.2 Hardware-Software Co-analysis                                    | 26 |

|          | 3.6 | Summary                                                                | 27 |

| 4        | Des | ign-Agnostic Symbolic Co-analysis Tool                                 | 28 |

|          | 4.1 | Gate-Level Simulator                                                   | 28 |

|          | 4.2 | Extending Iverilog For Symbolic Hardware-Software Co-Analysis $\ldots$ | 29 |

|          |     | 4.2.1 Iverilog Software Flow Enhancement                               | 30 |

|          | 4.3 | Symbolic Hardware-software Co-analysis Using Iverilog                  | 31 |

|          |     | 4.3.1 Designing A Testbench For Symbolic Hardware-Software Co-Analysis |    |

|          |     | For Iverilog                                                           | 32 |

|          |     | 4.3.2 Conservative State Management                                    | 34 |

|          |     | 4.3.3 Propagation Of Symbols                                           | 36 |

|          | 4.4 | Evaluation                                                             | 37 |

|          |     | 4.4.1 Validation                                                       | 38 |

|          |     | 4.4.2 Exercisable Gates                                                | 39 |

|          |     | 4.4.3 Simulation paths                                                 | 39 |

|          | 4.5 | Related Work                                                           | 42 |

|          | 4.6 | Summary                                                                | 43 |

| <b>5</b> | App | plication-Specific Architecture Selection                              | 45 |

|          | 5.1 | Effect Of Bespoke Process On Architectural Variants                    | 46 |

|          | 5.2 | Effect Of Architectural Variants On Efficiency Metric                  | 48 |

|          |     | 5.2.1 Processor Architectures                                          | 48 |

|          |     | 5.2.2 Hardware Accelerators                                            | 50 |

|          | 5.3 | Motivation                                                             | 50 |

|          | 5.4 | Application-Specific Architecture Selection                            | 52 |

|          |     | 5.4.1 Feature Extraction                                               | 54 |

|          |     | 5.4.2 Model Selection                                                  | 55 |

|          |     | 5.4.3 Training The Model                                               | 56 |

|          |     | 5.4.4 Prediction, Ranking, And Architecture Selection                  | 56 |

|          |     |                                                                        |    |

|   |                | 5.4.5  | Application-Specific Architecture Selection For DSP Circuits                                                                                | 57   |

|---|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------|------|

|   | 5.5            | Evalua | $tion \ldots \ldots$ | 57   |

|   |                | 5.5.1  | Design Space Exploration For Bespoke General Purpose Processors                                                                             | 5 59 |

|   |                | 5.5.2  | Design Space Exploration For Bespoke DSP Accelerators $\ . \ . \ .$                                                                         | 65   |

|   |                | 5.5.3  | Final Remarks                                                                                                                               | 66   |

|   | 5.6            | Genera | ality And Limitations                                                                                                                       | 69   |

|   | 5.7            | Relate | d Work                                                                                                                                      | 70   |

|   |                | 5.7.1  | Design Space Exploration                                                                                                                    | 70   |

|   |                | 5.7.2  | Application-Specific Processor Cores And High-Level Synthesis .                                                                             | 71   |

|   | 5.8            | Summ   | ary                                                                                                                                         | 71   |

| 6 | $\mathbf{Des}$ | igning | Cost-Effective Cache Replacement Policy Using Machine                                                                                       | 9    |

|   | Lea            | rning  |                                                                                                                                             | 73   |

|   | 6.1            | Motiva | ntion                                                                                                                                       | 73   |

|   | 6.2            | Machin | ne Learning-Aided Architecture Exploration                                                                                                  | 76   |

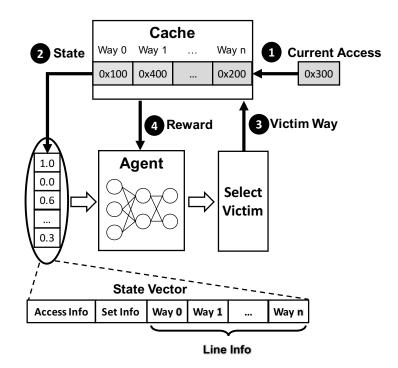

|   |                | 6.2.1  | RL-based Simulation Framework                                                                                                               | 77   |

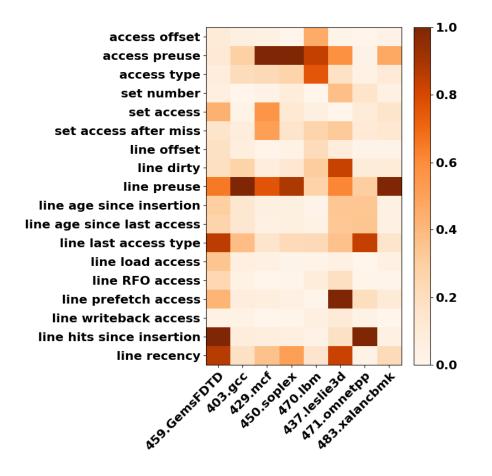

|   |                | 6.2.2  | Insights From Neural Network                                                                                                                | 81   |

|   |                | 6.2.3  | Benefits Of Deriving Insights Using ML                                                                                                      | 88   |

|   | 6.3            | Reinfo | rcement Learned Replacement (RLR)                                                                                                           | 90   |

|   |                | 6.3.1  | Replacement Algorithm                                                                                                                       | 90   |

|   |                | 6.3.2  | Hardware Implementation                                                                                                                     | 93   |

|   |                | 6.3.3  | Optimizations                                                                                                                               | 94   |

|   |                | 6.3.4  | Multicore Extension                                                                                                                         | 95   |

|   | 6.4            | Evalua | tion                                                                                                                                        | 96   |

|   | 6.5            | Relate | d Work                                                                                                                                      | 102  |

|   | 6.6            | Summ   | ary                                                                                                                                         | 105  |

| 7 | Con            | clusio | n And Discussion                                                                                                                            | 106  |

| B | efere          | nces   |                                                                                                                                             | 109  |

|   | C10101         |        |                                                                                                                                             | -00  |

# List of Tables

| 3.1 | Benchmarks                                                                                | 20 |

|-----|-------------------------------------------------------------------------------------------|----|

| 3.2 | $Constrained \ conservative \ state \ symbolic \ co-analysis \ reduces \ analysis \ time$ |    |

|     | compared to naive and conservative state-based co-analysis and enables                    |    |

|     | analysis of applications with complex control structures. $\ldots$                        | 21 |

| 3.3 | Use of constraints reduces the number of explored symbolic execution                      |    |

|     | paths                                                                                     | 21 |

| 3.4 | Use of constraints reduces the number of gates identified as exercisable.                 | 21 |

| 3.5 | Symbolic simulation approach comparison                                                   | 25 |

| 4.1 | Benchmark applications                                                                    | 38 |

| 4.2 | Target platform characterization                                                          | 38 |

| 4.3 | Gate count analysis                                                                       | 39 |

| 4.4 | Simulation path and runtime analysis                                                      | 41 |

| 5.1 | General purpose processors evaluated                                                      | 58 |

| 5.2 | DSP accelerators evaluated                                                                | 59 |

| 5.3 | Architectural variants explored                                                           | 60 |

| 5.4 | Benchmark applications for general purpose processors                                     | 61 |

| 5.5 | Summary of optimal architecture in terms of area; the model predicts                      |    |

|     | with $100\%$ accuracy in top 10 predictions $\ldots \ldots \ldots \ldots \ldots \ldots$   | 63 |

| 5.6 | Summary of optimal architecture in terms of <b>energy per bit</b> ; the model             |    |

|     | predicts with 100% accuracy in top 10% of predictions                                     | 65 |

| 5.7 | This table presents the optimal architectural variant for each bespoke                    |    |

|     | accelerator and its rank as predicted by our model for <b>area</b> . In most              |    |

|     | cases, our model ranks the optimal architecture within the top $10\%$ of                  |    |

|     | candidate architectures.                                                                  | 67 |

|     |                                                                                           |    |

| 5.8 | This table presents the optimal architectural variant for each bespoke                                             |     |

|-----|--------------------------------------------------------------------------------------------------------------------|-----|

|     | accelerator and its rank as predicted by our model for <b>energy</b> . In most                                     |     |

|     | cases, our model ranks the optimal architecture within the top $10\%$ of                                           |     |

|     | candidate architectures. $\ldots$ | 68  |

| 6.1 | Hardware overhead for different replacement policies in a 16-way 2 $\operatorname{MB}$                             |     |

|     | cache                                                                                                              | 74  |

| 6.2 | List of features considered by the RL agent $\hdots \ldots \ldots \ldots \ldots \ldots$                            | 78  |

| 6.3 | Parameters and configuration for RL training                                                                       | 81  |

| 6.4 | Parameters for the evaluated system                                                                                | 96  |

| 6.5 | Overall speedup for different replacement policies                                                                 | 100 |

# List of Figures

| 2.1 | Example of conservative state representing register values at different     |    |

|-----|-----------------------------------------------------------------------------|----|

|     | execution states for the same PC                                            | 8  |

| 3.1 | Example C program                                                           | 10 |

| 3.2 | Compiled MSP430 program                                                     | 10 |

| 3.3 | Conservative state-based scalable symbolic co-analysis can analyze appli-   |    |

|     | cations with infinite loops and input-dependent branches by simulating      |    |

|     | conservative states that capture the activity of multiple possible states.  | 12 |

| 3.4 | Constraining memory elements based on bounds from the software level        |    |

|     | reduces pessimism in estimating the number of gates marked as exercis-      |    |

|     | able and also reduces the number of paths that need to be explored. $\ .$ . | 13 |

| 3.5 | Methodology for CCS                                                         | 14 |

| 3.6 | Example of constraint encoding during static analysis of the application    |    |

|     | binary                                                                      | 16 |

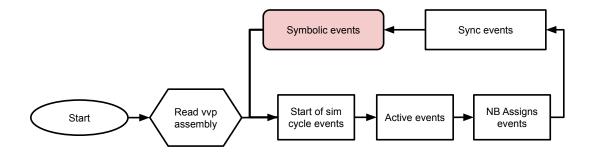

| 4.1 | We add a new type of event to capture 'symbolic events' in iverilog's       |    |

|     | event queue. This enables us to monitor control signals for X and halt the  |    |

|     | simulation when necessary. The VVP engine is a part of iverilog source      |    |

|     | that executes an iverilog compiled assembly code that is generated from     |    |

|     | the verilog testbench                                                       | 30 |

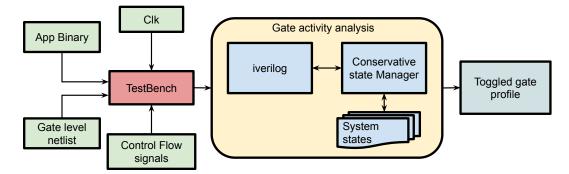

| 4.2 | Our design-agnostic symbolic co-analysis tool is built on top of iverilog   |    |

|     | to allow hardware-software co-analysis of any digital design                | 31 |

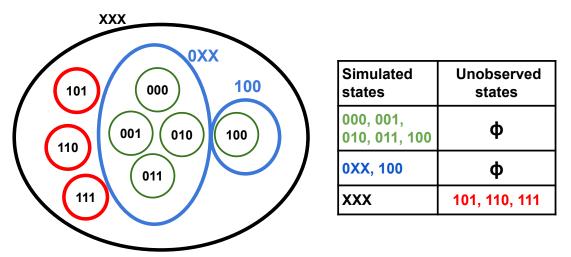

| 4.3 | Various approaches for conservative state generation exhibit trade-offs be-                 |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | tween simulation effort and conservative over-approximation. To capture                     |    |

|     | all states in the first row (green) we could either create two conservative                 |    |

|     | states as shown in the second row (blue) or one uber-conservative state                     |    |

|     | as shown in the third row (red)                                                             | 35 |

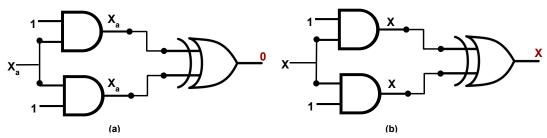

| 4.4 | Our symbolic tool allows rules for symbol propagation to be customized.                     |    |

|     | The left sub-figure shows a case where circuit inputs are propagated as                     |    |

|     | separate symbolic values, while the right sub-figure shows a case where                     |    |

|     | the symbolic values carry no identifying information and thus cannot be                     |    |

|     | distinguished.                                                                              | 36 |

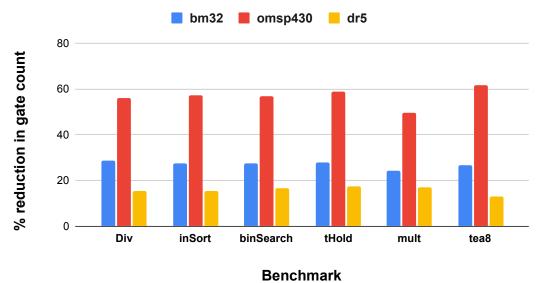

| 4.5 | Benchmarks run on MSP430 processor have a higher reduction in exer-                         |    |

|     | cisable gate count compared to MIPS and RISCV processors because of                         |    |

|     | the presence of unused peripherals in MSP430                                                | 40 |

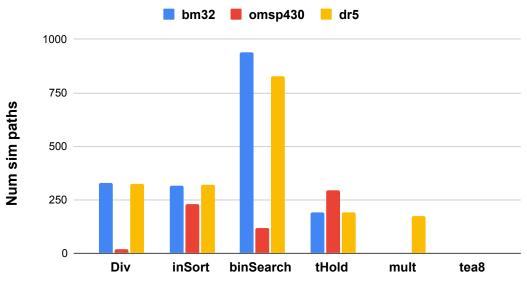

| 4.6 | Benchmarks run on MIPS and RISCV processors have a higher number                            |    |

|     | of simulated paths because a 16-bit register is used to indicate branch                     |    |

|     | conditions, whereas in MSP430, a 1-bit register is used, resulting in fewer $% \mathcal{A}$ |    |

|     | conservative states                                                                         | 42 |

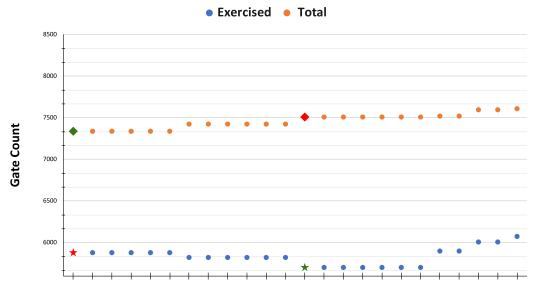

| 5.1 | This plot shows the total gate count for various architectural variants of                  |    |

|     | the darkriscv processor both before and after bespoke customization for                     |    |

|     | the tea8 application. The optimal processor variant before customization                    |    |

|     | (green diamond) is different than the optimal bespoke processor variant                     |    |

|     | after customization (green star).                                                           | 47 |

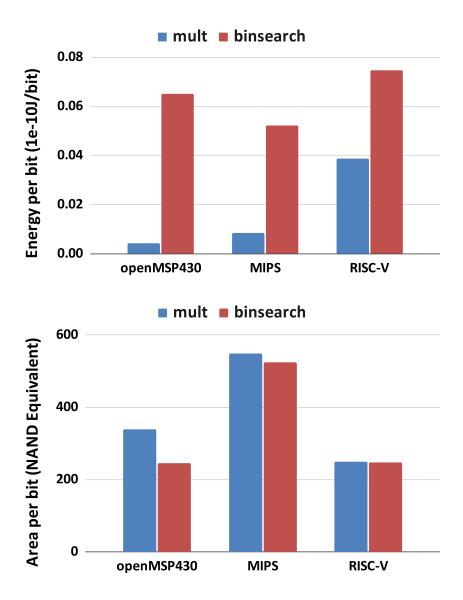

| 5.2 | The plots compare per-bit energy consumption (top) and area (bottom)                        |    |

|     | for bespoke processors tailored for mult and binsearch applications, start-                 |    |

|     | ing from three distinct processor architectures – $MSP430$ , $MIPS$ , and                   |    |

|     | RISC-V. The MSP430-based bespoke processor has the lowest per-bit                           |    |

|     | energy consumption for the mult application, but the MIPS-based design                      |    |

|     | has the lowest energy for the binsearch application. On the other hand,                     |    |

|     | the RISC-V-based design has the lowest per-bit area for each application.                   |    |

|     | The results demonstrate that the best processor architecture from which                     |    |

|     | to generate a bespoke processor differs based on the target application                     |    |

|     | and efficiency metric                                                                       | 49 |

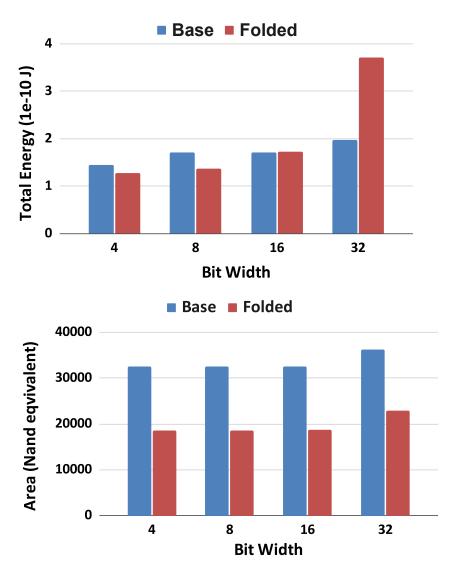

| 5.3 | The plots compare energy consumption (top) and area (bottom) for be-                                 |    |

|-----|------------------------------------------------------------------------------------------------------|----|

|     | spoke accelerators tailored for applications with different input bit preci-                         |    |

|     | sion, starting from folded and un-folded architectural variants of a 32-bit                          |    |

|     | DCT filter DSP accelerator. The x-axis represents input signal bit width,                            |    |

|     | corresponding to different applications that require different levels of pre-                        |    |

|     | cision. Bespoke accelerators generated from the folded architecture have                             |    |

|     | lower area for all input bit widths, but for a bit width of 32, the un-                              |    |

|     | folded accelerator has lower energy due to its lower computation time.                               |    |

|     | The best accelerator architecture from which to generate a bespoke ac-                               |    |

|     | celerator differs based on the target application (bit width) and efficiency                         |    |

|     | metric.                                                                                              | 51 |

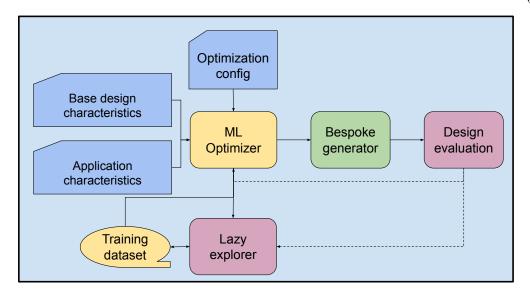

| 5.4 | Our machine learning model for selecting an architectural configuration                              |    |

|     | from which to generate a bespoke processor uses architecture features of                             |    |

|     | the baseline design and application characteristics to predict metric values                         |    |

|     | for each architectural configuration in the architectural parameter space.                           |    |

|     | A short-list of candidate architectures is evaluated more thoroughly to                              |    |

|     | identify the most efficient architectural variant                                                    | 53 |

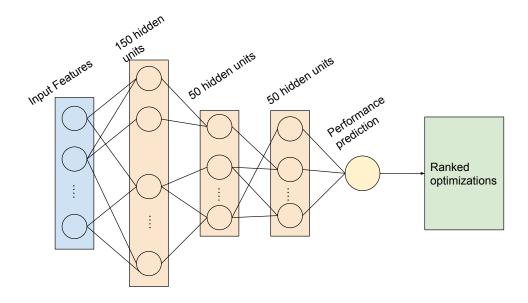

| 5.5 | We use a neural network that predicts different desired metrics. There                               |    |

|     | is a slight variation in the models that predict area and energy metrics.                            |    |

|     | The model that predicts energy uses the tanh activation function, while                              |    |

|     | the model that predicts area uses ReLU activation                                                    | 56 |

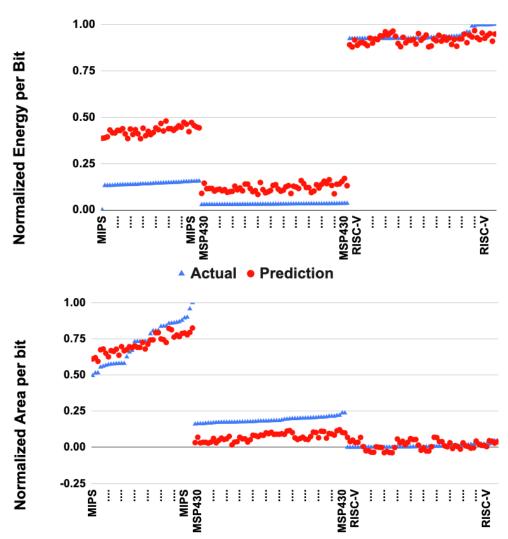

| 5.6 | This plot shows the normalized energy per bit (top) and normalized area                              |    |

|     | per bit (bottom) predictions of bespoke processors for mult. The x-axis                              |    |

|     | denotes different architectural configurations. The predicted and actual                             |    |

|     | metric values follow a similar trend. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 62 |

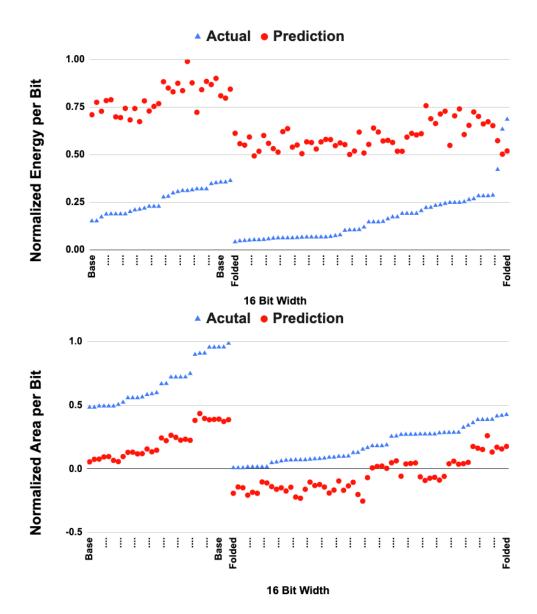

| 5.7 | This plot shows predicted and actual values for normalized energy per bit                            |    |

|     | (top) and normalized area per bit (bottom) for bespoke DCT accelerators.                             |    |

|     | The x-axis denotes different architectural configurations. The predicted                             |    |

|     | and actual metric values follow a similar trend, indicating that our model                           |    |

|     | can be used to predict the optimal architecture. $\ldots$                                            | 64 |

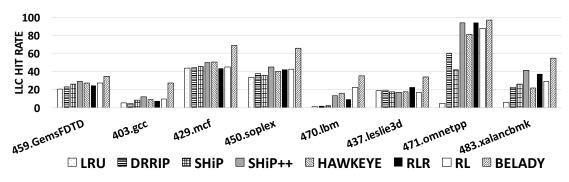

| 6.1 | LLC hit rate comparison (Belady is the theoretical optimal). $\ldots$ .                              | 75 |

| 6.2 | Simulation framework overview                                                                        | 79 |

| 6.3  | Heat map of neural network weights. The y-axis shows features repre-                   |     |

|------|----------------------------------------------------------------------------------------|-----|

|      | senting LLC state, and the x-axis shows the benchmarks used in the agent               |     |

|      | simulation. The features with high magnitude of weights are (consider-                 |     |

|      | ing at least three benchmarks) access preuse, line preuse, line last access            |     |

|      | type, line hits since insertion, and line recency. $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 83  |

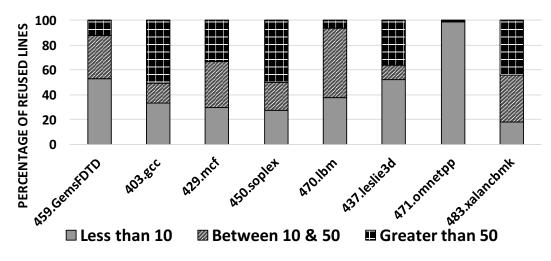

| 6.4  | Difference between preuse and reuse distance for reused cache lines                    | 85  |

| 6.5  | Average victim age for each access type                                                | 86  |

| 6.6  | Number of hits when a cache line is evicted                                            | 87  |

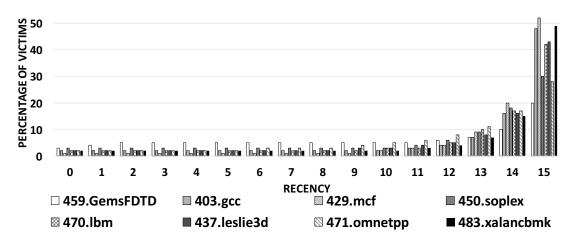

| 6.7  | Recency for victims in agent simulation                                                | 88  |

| 6.8  | Flowchart for priority computation in RLR                                              | 90  |

| 6.9  | Hardware implementation for computing RD. On a demand hit, the cache                   |     |

|      | line's age value is sent to the RD computation circuit.                                | 94  |

| 6.10 | Performance comparison for different LLC replacement policies (SPEC2006).              | 97  |

| 6.11 | Performance comparison for different policies (Cloudsuite).                            | 97  |

| 6.12 | Demand MPKI comparison for different policies                                          | .00 |

| 6.13 | Performance comparison of different policies in the 4-core setup 1                     | .01 |

## Chapter 1

# Introduction

One of the main challenges that processor architects face in recent times is improving the energy efficiency of a design. Dennard Scaling has ended and transistor size scaling has slowed down. Irrespective of scale, from servers to embedded systems, improving energy efficiency is becoming increasingly challenging. Energy efficiecy is especially vital for embedded systems that run applications such as implantables [1,2], wearables [3,4], and IoT applications [5-10], since these systems are often powered by batteries or energy harvesting. One defining characteristic of such systems is that they tend to run the same software over and over, as defined by their application. Based on the application-specific nature of such systems, a recent line of work has proposed application-specific power and energy reduction techniques that identify hardware resources (e.g., gates) in a processor that cannot be exercised by the application running on the processor and eliminate the power used to support those resources [11-13]. However, such application-specific optimizations can only be safely applied if an analysis technique can guarantee that the application running on the processor will never use the resources for any possible execution of the application, for any inputs. Eliminating gates or power for resources that could be used by the application could lead to incorrect execution of the application. For example, power gating a gate that was incorrectly identified as "unused" but is actually exercised by an application can result in the application producing incorrect outputs or crashing. Given the need for guarantees and the inability to achieve such guarantees through input-based application profiling, recently-proposed application-specific power management techniques rely on a symbolic simulation [14] of the application on the processor hardware to identify hardware resources that are guaranteed to not be used across all possible executions of an application. By propagating symbols that represent unknown logic values for all inputs to an application, it is possible to determine all possible hardware resources that could be used by the application in an input-independent fashion [11,12]. Recent work has demonstrated that the input-independent activity profiles generated by such a symbolic simulation of an application running on a processor can be leveraged to identify worst-case timing, power, and energy characteristics for a low-power system and to eliminate power used by resources that the system's captive application is guaranteed to never use [11–13].

This approach is sound and characterizes the application based on the instructions in the application binary. However, some of the program semantics are lost because of optimization techniques used in prior works. To handle the large number of possible execution paths for applications with complex control structures, prior work [15] maintains *conservative* states at PC-changing instructions. A conservative state encompasses a superset of all observed states every time the simulation re-visits the PC. If a state is a sub-state of the conservative state maintained at the PC, that state has already been simulated, and execution from the state can be terminated.

The conservative state based approach allows analysis to complete sooner, but suffers from the pessimism of marking too many gates as exercisable, potentially leaving significant benefits on the table. This is due to the nature of conservative state construction, where states are merged by replacing locations that are different with Xs, representing unknown logic values; thus, the number of states represented by the resulting super-state can be exponentially more than the number of states used to generate the conservative state. This can lead to covering states that are not possible in the original application. In this work, we characterize the behavior of an application by analyzing the binary to determine constraints, e.g., bounds of a particular memory element. Such bounds can be used to *constrain* the value of the memory element from being overly pessimistic (i.e., containing too many Xs), leading to fewer gates marked as exercisable and reduced simulation times.

Constraints from application software help us to optimize an existing processor design for better energy efficiency. However, design optimization for energy efficiency should consider not only design-level optimization but also architecture-level optimization. Some architectures may suit one application better than another. For example, an architecture that contains a hardware multiplier may perform multiplication operation in one cycle but consume more energy than an architecture that uses repeated addition to perform multiplication. Depending on the energy requirements, we may chose to add or remove the hardware multiplier for the architectures. In another example, a pipelined design has shorter critical paths than a non-pipelined version of the same design allowing the gates to have a lower drive strength. In contrast, increasing pipeline stages could cause energy overhead from both inserted registers and clock distribution [16]. Depending on factors that are dominating, either the pipelined or the non-pipelined version of a design could be more energy-efficient. Clearly, if energy efficiency is the goal, the processor architecture must also be optimized. Given the wide variety of architectures for embedded processors, there are a lot of choices to consider. This brings in new challenges. We need a tool that analyzes application behavior on any architecture. Despite the significant potential of application-specific design and optimization techniques, applicability has been limited, since the symbolic co-analysis tools developed in previous works [13] were developed for a single processor (openMSP430), and extending them to analyze and optimize other processor designs or architectures requires the challenging and time-consuming task of developing a new custom simulation tool for each new design. This simulation approach is not scalable, especially for industry, as each application may use a different design, and it is infeasible to write a custom simulation tool for each design. So, we built a design-agnostic simulation tool that can handle any design, technology or architecture. For this, we use iverilog - an open source synthesis and simulation tool. In this work, we discuss how we restructured iverilog to allow us to perform application specific processor optimization on any given processor-application pair.

Another challenge that the architecture choices bring is the enormous design-space to evaluate. A processor's architecture can be different depending on microarchitectural features such as register-file, memory, adders, multipliers, and many more. In addition to number of microarchitectural features, the choice of the feature implementation also adds to exploration. For example, a multiplier can have a and-gate, nand-gate, or muxbased implementation. In another example, an adder can be implemented as a ripplecarry adder, carry-save adder, or several other options. All these options exponentially increase the architectural parameter space. Enumerating and exploring this search space includes applying design automation techniques such as synthesis, placement, and routing of the design in addition to symbolically evaluating the application on the hardware. Though we have a generic tool to evaluate any architecture, the run time to evaluate all the possibilities is prohibitively expensive. Moreover, the impact of application-specific hardware optimizations on the energy profile of an architecture is non-trivial. There is no deterministic way to identify an architecture that is most energy-efficient without performing the hardware optimizations and then evaluating the application on the optimized design. Considering the enormous design space, significant simulation time and non-trivial impact of the hardware optimizations, we rely on Machine Learning (ML) to help us minimize the number of architectural options that we must evaluate. We present a tool that takes into account the impacts of application-specific optimizations on different architectural features and predicts near-optimal architecture that best suits the application in terms of energy efficiency. We evaluate top few predicted architectures using our generic tool and pick the design with most energy-efficiency.

With the help of Machine Learning, we were able to solve the design space exploration problem efficiently. This motivated us to use ML in other complex problems. ML expedites tedious processes and augments human intelligence to solve problems where heuristic-based solutions have limitations. Because of these benefits of ML, there is a surging interest in applying machine learning (ML) to challenging computer architecture design problems. Building an effective cache replacement policy has been one of the important challenges in computer architecture. There has been considerable work on designing efficient cache replacement algorithms [17–22]. The design of novel policies has historically been based on the designer's skill and creativity to derive insights from common cache access patterns and use them to develop a cost-effective cache replacement policy. Firstly, it takes enormous skill and effort to analyze an access pattern and come up with valuable insights. Secondly, new applications emerge every day and existing applications keep evolving, exposing caches to new access patterns. The cache architecture needs to adapt to the ever-changing demands. Therefore, we need an automated way of generating insights and developing cache replacement policies. In this work, we develop a tool that analyzes a set of applications and learns a near-optimal replacement policy using ML. The designer can then derive a cost-effective replacement policy using the insights from the learned policy. In this work, we show one way of developing a cost-effective cache replacement policy that meets or beats the performance of current state of art policies.

This dissertation is organized as follows. Chapter 2 provides the background for coanalysis techniques used to devise application-specific hardware optimizations. Chapter 3 introduces application-based software constraints and discusses the means and impact of using them for application-specific hardware optimizations. Chapter 4 presents a generic tool that performs application-specific analysis on any design. Chapter 5 emphasizes the importance of modifying architecture for energy-efficiency and shows how Machine Learning can help contain the design-space exploration when several architectural parameters are considered. Chapter 6 extends the use of Machine Learning in architecture optimization by showing how a cost-effective cache replacement policy can be built using machine learning that beats the current state of art. Chapter 7 concludes the thesis and discusses a few future research directions.

# Chapter 2

# Background

This chapter provides background information on co-analysis techniques used to devise application-specific hardware optimizations.

### 2.1 Symbolic Simulation Based Hardware Software Coanalysis

Application-specific nature of emerging ultra-low-power systems [1–10] provides the opportunity to make application-specific optimizations on the processor used in such systems. A recent line of work [11–13] has proposed application-specific power and energy reduction techniques that identify hardware resources (e.g., gates) in a processor that cannot be exercised by the application running on the processor and eliminate the power used to support those resources. However, such application-specific optimizations can only be safely applied if an analysis technique can guarantee that the application running on the processor will never use the resources for any possible execution of the application, for any inputs. Eliminating gates or power for resources that could be used by the application could lead to incorrect execution of the application. For example, power gating a gate that was incorrectly identified as "unused" but is actually exercised by an application can result in the application producing incorrect outputs or crashing. Given the need for guarantees and the inability to achieve such guarantees through input-based application profiling, recently-proposed application-specific power management techniques rely on a symbolic simulation [14] of the application on the processor hardware to identify hardware resources that are guaranteed to not be used across all possible executions of an application. By propagating symbols that represent unknown logic values for all inputs to an application, the work in [11–13] characterizes the gate-level activity of a processor executing an application for all possible inputs. During the gate-level simulation, the simulator sets all inputs to Xs, which are treated as both 1s and 0s. In each simulation cycle, gates where an X propagated are considered as toggled, since some input assignment could cause the gates to toggle. The set of gates that have toggled during the simulation determines the possible hardware resources that could be used by the application for any application input.

Symbolic simulation is an effective methodology to analyze a design for all application inputs using a single simulation. However, replacing application inputs with symbols makes it challenging to handle input dependent control flow paths. For example, if an X propagates to the PC, it is unclear how execution must proceed. The work in [11–13] branches the execution tree and simulates execution for all possible branch paths, following a depth-first ordering of the control flow graph. Since this naive simulation approach does not scale well for complex or infinite control structures which result in a large number of branches to explore, the work in [15] employed a conservative approximation method that allows the analysis to scale for arbitrarily-complex control structures while conservatively maintaining correctness in identifying exercisable gates. For the approximation to work, [15] generates and maintains conservative states.

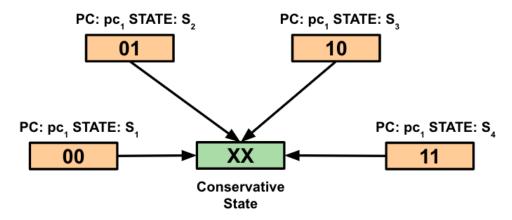

#### 2.2 Conservative State

A conservative state is defined as the gate-level state of a processor that conservatively represents multiple observed states for each control-flow changing instruction of the application. For example, a conservative state with a register value of XX can represent four different states with the same register possessing one of the 00,01,10,11 values as shown in Figure 2.1. The approximation works by tracking the most conservative gatelevel state that has been observed for each PC-changing instruction (e.g., conditional branch). When a branch is re-encountered while simulating on a control flow path, simulation down that path can be terminated if the symbolic state being simulated is a substate of the most conservative state previously observed at the branch (i.e., the

Figure 2.1: Example of conservative state representing register values at different execution states for the same PC.

states match or the more conservative state has Xs in all differing variables), since the state (or a more conservative version) has already been explored. If the simulated state is not a substate of the most conservative observed state, the two states are merged to create a new conservative symbolic state by replacing differing state variables with Xs, and simulation continues from the conservative state. This conservative approximation technique allows gate activity analysis to complete in a small number of passes through the application code, even for applications with an exponentially-large or infinite number of execution paths.

This conservative approximation method is effective. However, it still treats the application as a black box, and hence, suffers from the pessimism of marking too many gates as exercisable, potentially leaving significant benefits on the table. This is due to the nature of conservative state construction, where states are merged by replacing locations that are different with Xs; thus, the number of states represented by the resulting super-state can be exponentially more than the number of states used to generate the conservative state. This can lead to covering states that are not possible in the original application. In the next chapter, we discuss how application information can help reduce the conservativeness of this approximation method.

# Chapter 3

# Constrained Conservative Symbolic Hardware-Software Co-analysis

Conservative state based symbolic hardware-software co-analysis allows the gate activity analysis to complete in a small number of passes through the application. However, the conservative approximation results in exploring execution paths that are not actually possible for the application. In this chapter, we demonstrate the concept of conservative state using an example and illustrate its limitations. We also show how application information can be exploited to reduce some of the over approximation.

#### 3.1 Conservative State Limitation

Conservative states are generated from previous simulated states by replacing locations that are different with Xs. The idea is to represent all simulated states with one conservative state. Conservative states allow terminating a simulation when the simulation encounters a previously simulated branch and the simulation state is a substate of the most recent conservative state for the corresponding PC. We illustrate the behavior and limitation of Conservative states using an example.

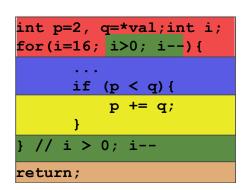

The example code in Figure 3.2 (compiled from C-code in Figure 3.1) represents a

Figure 3.1: Example C program.

mov #16, r5 1. 2. mov #2, r13 3. mov &200, r14 loop: 4. 5. cmp r13, r14 6. jnc then add r14, r13 7. then: 8.dec r5 9.jnz loop 10. ret

Figure 3.2: Compiled MSP430 program.

simple subroutine that updates an internal variable (represented by r13 (p)), based on an external value (represented by r14 (q)), over 16 iterations (tracked by r5 (i)). The first section of the code (red) initializes the registers r5, r13, and r14. The next two sections (blue and yellow) are the loop body, where r13 is compared against r14. If r14  $\geq$  r13, line 7 is executed to increase r13 by r14. Otherwise, simulation iterates again, after decreasing the loop counter (r5) in the next section (green). After exiting the loop, we return from this subroutine.

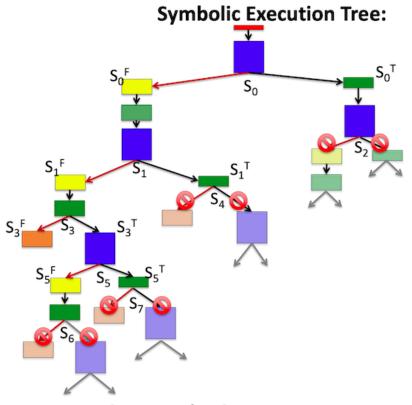

To get the gate activity of the example code, the symbolic simulation replaces the external value (represented by r14 (q)) with Xs. Figure 3.3 shows the execution tree of conservative state based symbolic simulation and the values of two registers r13 and r5 at various states that the processor reaches during execution. The simulation starts in the red block and reaches the end of the blue block. Since r14 contains Xs, the subsequent jump jnc's path is inconclusive, and an X propagates to the PC. We split the simulation to execute both branch paths – the yellow block and the green block. The state of the processor at the end of the blue block is represented as  $S_0$ , and the states of the processor at the start of false and true paths are represented as  $S_0^F$  and  $S_0^T$ ,

respectively. The same convention is used for the rest of the states in the tree. Each state in the table contains two rows for the values of the registers r13 and r5. The upper row represents the value of the register observed when the simulation reaches the corresponding point in the execution tree. The lower row represents the conservative value computed by merging this value with the previous conservative state observed at this point.

Simulation proceeds using this conservative value instead of the observed value. One example of conservative approximation is that of register r5 for state  $S_1$ . Since  $S_1$  and  $S_0$  correspond to the same PC, we build a conservative state to represent both the states  $S_1$  and  $S_0$  when we simulate down  $S_1$ ; this is achieved by replacing the values that differ between the two states with Xs. In the case of r5, the two states differ in the least significant 5 bits, which are replaced by Xs to represent both the states. This *X*-ification of the states leads to skipping execution of several states downstream and thus a faster completion of application analysis.

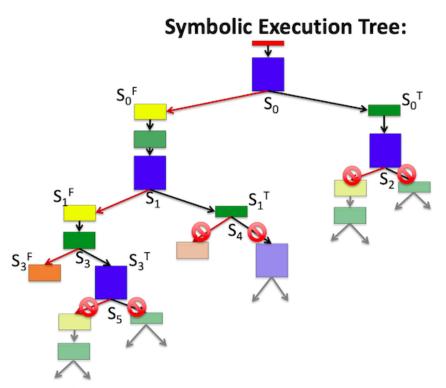

In our work, constrained conservative state symbolic hardware-software co-analysis, we translate constraints on variables at the software level to constraints on memory elements in the processor-memory system. In this example, since  $0 \leq r5 < 17$ , we constrain the value of r5 to 16'b0000000000XXXXX, preventing the unnecessary propagation of Xs. Figure 3.4 shows the execution of the example code in Figure 3.2 using

#### **Conservative States:**

| State                 | РС | r13                                     | r13 r5                                  |  |

|-----------------------|----|-----------------------------------------|-----------------------------------------|--|

| State                 | PC | R13(c_state)                            | R5(c_state)                             |  |

| c                     | 6  | 0b0000000000000000000000000000000000000 | 060000000000000000000000000000000000000 |  |

| S <sub>0</sub>        | D  | 0b0000000000000000000000000000000000000 | 060000000000000000000000000000000000000 |  |

| c                     | 6  | 0bxxxxxxxxxxxxxxxx                      | 0Ь0000000000001111                      |  |

| S <sub>1</sub>        | в  | 0bxxxxxxxxxxxxxxxx                      | 0ь00000000000ххххх                      |  |

| -                     | 6  | 060000000000000000000000000000000000000 | 0Ь0000000000001111                      |  |

| S <sub>2</sub>        | Б  | 0bxxxxxxxxxxxxxxx                       | 0ь00000000000ххххх                      |  |

| <u> </u>              | 0  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| S <sub>3</sub>        | 9  | Obxxxxxxxxxxxxxxx                       | 0bxxxxxxxxxxxxxxxx                      |  |

| <u> </u>              |    | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| $S_4$                 | 9  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| 6                     | 6  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| <b>S</b> <sub>5</sub> | 6  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| c                     | 0  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| S <sub>6</sub>        | 9  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

| -                     | 0  | Obxxxxxxxxxxxxxx                        | 0bxxxxxxxxxxxxxxxx                      |  |

| S <sub>7</sub>        | 9  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |  |

Figure 3.3: Conservative state-based scalable symbolic co-analysis can analyze applications with infinite loops and input-dependent branches by simulating conservative states that capture the activity of multiple possible states.

### **Constrained Conservative States(CCS):**

| State          | PC | r13                                     | r5                                      |              |

|----------------|----|-----------------------------------------|-----------------------------------------|--------------|

|                |    | R13(cc_state)                           | R5(cc_state)                            |              |

| c              |    | 060000000000000000000000000000000000000 | 060000000000000000000000000000000000000 |              |

| S <sub>0</sub> | 6  | 0Ь000000000000000000000000000000000000  | 0Ь0000000000010000                      |              |

| c              | 6  | 0bxxxxxxxxxxxxxxxx                      | 0Ь0000000000001111                      |              |

| S <sub>1</sub> | 6  | 0bxxxxxxxxxxxxxxxx                      | 0ь00000000000ххххх                      |              |

| 6              | 6  | 0Ь000000000000000000000000000000000000  | 0Ь0000000000001111                      |              |

| S <sub>2</sub> | 6  | 0bxxxxxxxxxxxxxxxx                      | 0ь00000000000ххххх                      | 1 <= r5 < 17 |

| c              | _  | 0bxxxxxxxxxxxxxxx                       | 0bxxxxxxxxxxxxxxxx                      |              |

| S <sub>3</sub> | 9  | 0bxxxxxxxxxxxxxxxx                      | 0ь00000000000xxxxx                      |              |

| c              | _  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |              |

| S <sub>4</sub> | 9  | 0bxxxxxxxxxxxxxxxx                      | 0b00000000000xxxxx                      |              |

| c              | 6  | 0bxxxxxxxxxxxxxxxx                      | 0bxxxxxxxxxxxxxxxx                      |              |

| S <sub>5</sub> | 6  | 0bxxxxxxxxxxxxxxxx                      | 0b000000000000xxxxx                     |              |

Figure 3.4: Constraining memory elements based on bounds from the software level reduces pessimism in estimating the number of gates marked as exercisable and also reduces the number of paths that need to be explored.

Figure 3.5: Methodology for CCS

constrained conservative state symbolic execution. This not only reduces the number of gates toggled; it also reduces the number of execution paths simulated, leading to faster convergence.

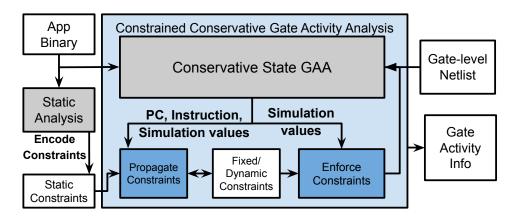

#### 3.2 Proposed Work

In this section, we explain Constrained Conservative State Symbolic Hardware-Software Co-Analysis. Our co-analysis tool (see Figure 3.5) is based on the observation that certain constraints on variables at the software level are lost when the application is simulated at the gate-level, leading to overly pessimistic estimates of the hardware resources (i.e., gates) needed to execute the application. We translate software-level constraints to the gate level in three steps. First, we encode high-level program constraints as constraints on the operand values of static instructions. Our tool generates these constraints from a pattern-based static analysis of the application binary. Second, these encoded constraints are loaded into the conservative symbolic simulator and propagated from source operands to destination operands during simulation. Third, when operands containing Xs are updated by an instruction, encoded and propagated constraints are applied so that the operands' symbolic values observe the constraints. Pseudocode of our implementation is shown in Algorithm 1 and Algorithm 2. Changes to the conservative symbolic co-analysis in Algorithm 1 are presented in **red**. In the following subsections, we explain each step in greater detail.

Algorithm 1 Constrained Conservative State Symbolic Co-analysis

```

1. Procedure GateActivityAnalysis(app_binary, design_netlist)

2. Initialize all memory cells and all gates in design_netlist to X

3. Load app_binary into program memory

4. Propagate reset toggle signal

5. s \leftarrow State at start of app_binary

6. Symbolic Execution Tree T.set_root(s)

7. Unprocessed execution points queue, U.push(s)

8. C.init() // Initialize conservative system state map

9. C_T.load_constraints() // Load Static constraints map

10. while U \mathrel{!=} \emptyset do

11.

e \leftarrow U.pop()

if e.isConditinalBranch() and e.PC \in C then

12.

13.

a \leftarrow C.getState(e.PC)

if e.isConservativeSubstateOf(a) then

14.

15.

continue

16.

else

e \leftarrow \text{buildConservativeState}(a, e)

17.

18.

C \leftarrow C.update(e.PC, e)

19.

end if

20.

else if e.isConditionalBranch() then

21.

C \leftarrow C.add(e.PC, e)

22.

end if

23.

while e.nextPC \mathrel{!=} X and !e.END do

24.

e.setInputsX() // set all peripheral port inputs to Xs

25.

e' \leftarrow \text{propagateGateValues}(e) // \text{perform simulation for this cycle}

if e'.aboutToCommit() then

26.

27.

// instruction will be committed in the next cycle

28.

c_t \leftarrow \text{getConstraints}(C_T, e'.PC)

29.

e' \leftarrow \text{propagateConstraints}(e', c_t) // \text{transfer constraints}, \text{source to destination}

30.

e' \leftarrow \text{enforceConstraints}(e', c_t)

31.

end if

32.

e.annotateGateActivity(e, e') // annotate tree point with activity

33.

e.addNextState(e') // add to execution tree

34.

e \leftarrow e' \ // \ {\rm process \ next \ cycle}

35.

end while

if e.nextPC == X then

36.

for all a \in \text{possibleNextPCVals}(e) do

37.

e' \leftarrow e.updateNextPC(a)

38.

39.

U.\mathrm{push}(e')

40.

T.insert(e')

41.

end for

42.

end if

43. end while

```

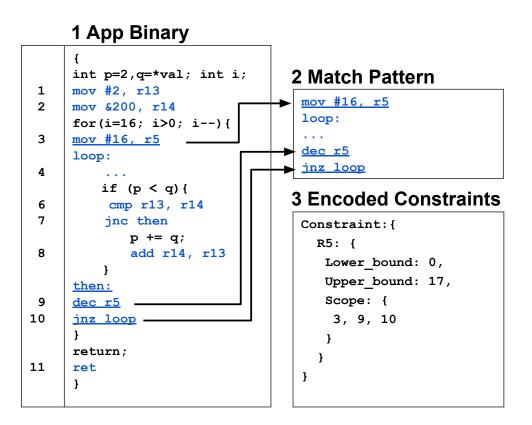

#### 3.2.1 Encoding Constraints From Binary

In order to constrain simulation values, our tool must know what memory element's values should be constrained, what its valid set of values are, and at what execution points those constraints are valid. As shown in Figure 3.6, our tool takes value bound constraints (e.g., 0 to 17) on instruction operands (e.g., r5) for specific instructions (e.g., the mov, dec, and jnz instructions at PCs 3, 9, and 10, respectively).

Figure 3.6: Example of constraint encoding during static analysis of the application binary.

An example instruction pattern is shown in Figure 3.6. Many possible static analyses at different abstraction levels, from C compiler to binary analysis, could be used to generate constraints, with varying trade-offs of coverage and precision [23–25]. For our work, we chose to use a pattern-based binary analysis approach where we map known binary patterns resulting from high-level program structures (e.g., loops and if statements) into constraints (e.g., register holding a loop iterator is bounded between its initialization and termination values at loop boundaries). We have identified nine such patterns involving different types of loops and nested loops. Note that for pattern-based analysis, the relevant patterns can depend on compiler options. Our library of patterns covers the most common patterns observed in our benchmark set (see Section 4.4).

#### 3.2.2 Propagating Constraints

Once we encode all the constraints, we load them into the co-analysis tool as Fixed (i.e., immutable) constraints on operands (i.e., register and memory values) at specific static instructions, and we start symbolic co-analysis. During co-analysis, we intercept every instruction when it is about to be committed in the processor pipeline, read the constraints on the instruction's source operands, and update the constraint on the destination operand if that operand does not have a Fixed constraint at the current PC. This updating creates a Dynamic constraint for the memory element.

Consider the instruction mov #2, r13, with r13 having no constraint before the instruction is executed. At the end of the execution of the instruction, we will have a constraint on r13 as  $2 \leq r13 < 3$ , representing its constant value. Consider another instruction, add r5, r13, with constraints on r5 as  $1 \leq r5 < 17$  and on r13 as  $2 \leq r13 < 3$ . Since the value of r5 does not contain Xs (it is 16), the constraint of r13 is updated by adding r5's value (16) to the lower and upper bounds of r13's constraints to produce the constraint:  $18 \leq r13 < 19$ . However, if the value of r5 is 16'bXXXXX, the constraint on r13 is updated to  $3 \leq r13 < 20$ , by adding the lower bounds and the upper bounds of the two constraints, respectively. This ensures that constraints are as tight as possible while encompassing all possible values.

#### 3.2.3 Enforcing Constraints

Encoding and propagating constraints ensures that values of registers or memory locations that are constrained cannot go out of bounds of these constraints. To ensure this, we monitor all register and memory location values for changes during simulation. Whenever a register or a memory location is modified, we check its value against any constraint it has. If the value of the register or memory location could be out of bounds of the constraint, we enforce the constraint on the register or memory location by modifying its value appropriately. Our technique ensures that enforcing constraints does not eliminate exploration of any reachable states for a given application. A formal proof is presented in Section 3.3.

In addition to constraining memory and register values, it is important to ensure that memory *addresses* do not go out of bounds. In an indirect addressing mode, if the register holding the memory address contains Xs, there are several possible addresses that could be accessed. In such a case, the constraint on the register restricts the number of possible memory locations. While performing memory reads, all possible memory addresses (defined by the constrained conservative value) are read, and a conservative value is generated out of data read from memory. This value is sent to the data bus and used by the instruction. Similarly, while handling a memory write, both the address and the value could have Xs. In this case, we first resolve the constraint on the address by identifying the permissible locations for the element, based on the constraint and the value of the address. We then generate conservative values and update the constraints at all the resolved addresses. For instance, consider the instruction mov r5, -5(r6). Assume that both r5 and r6 contain Xs. To handle proper execution of this instruction, we first obtain the constraint for r6 and adjust the address constraint for -5(r6) according to the offset (i.e., Lower\_bound -5(r6) $\leftarrow$  Lower\_bound (r6) - 5) and Upper\_bound -5(r6)  $\leftarrow$  Upper\_bound (r6) - 5). Then, for each address represented by -5(r6)'s value in the simulator (the value with the Xs), we check if the address is in the range of the constraint (i.e., Lower\_bound -5(r6)< address < Upper\_bound -5(r6)). For the addresses that are in the bound of the constraint, we write the conservative value of r5 combined with the existing memory value to the locations pointed by the resolved addresses. This algorithm is presented in Algorithm 2.

Algorithm 2 Constraint Enforcement

```

1. //e: Execution state of the processor

2. // c_t : Constraint

3. Procedure enforceConstraints(e, c_t)

4. if e.isOutputOutOfBounds(c_t) then

if {\it e.isMemoryOp()} then \\

5.

e \leftarrow \text{handleMemoryEnforcement}(e, c_t)

6.

7.

else

e.dstRegVal \leftarrow genConstrainedVal(e.dstRegVal, c_t)

8.

9.

end if

10. end if

11. return e

12. //e: Execution state of the processor

13. // c_t : Constraint

14. Procedure handleMemoryEnforcement(e, c_t)

15. if containsX(e.memAddress) then

for all addr \in \text{possibleAddresses}(e.\text{memAddress}) do

16.

if isAddressInBounds(addr, c_t.addressConstraint) then

17.

18.

if e.memOperation == read then

19.

val \leftarrow generateConstrainedConservativeVal(val,

e.dMemory[addr], c_t.valConstraint)

20.

else if e.memOperation == write then

e.dMemory[addr] \leftarrow generateConservativeVal(e.val, e.dMemory[addr])

21.

22.

end if

23.

end if

24.

end for

if e.memOperation == read then

25.

26.

e.dataBus.put(val)

27.

end if

28. else

29.

addr \leftarrow e.memAddress

30.

if e.memOperation == read then

31.

val \leftarrow e.dMemory[addr]

32

e.dataBus.put(val)

else if e.memOperation == write then

33.

e.dMemory[addr] \leftarrow e.val

34.

35.

end if

36. end if

37. return e

```

#### **3.3 Proof of CCS Correctness**

**Theorem 1** (Application Execution State Coverage). Given a constraint c and an element (register/memory address) e, enforcing c on e at a PC p does not eliminate exploration of any reachable states for application A.

*Proof.* Let  $S_1, S_2, \ldots, S_n$  be consecutive conservative states generated at PC p by the Conservative State (CS) approach. By definition of conservative state,  $S_1 \subset S_2 \subset \ldots \subset S_n$ . Let  $S_i$  be the first state where e violates c. Thus,  $S_i$  covers all executions leading to p that have been explored until the  $i^{th}$  encounter of p. I.e., for all states before

Table 3.1: Benchmarks

| Embedded Sensor Benchmarks [29]                                 |

|-----------------------------------------------------------------|

| mult, binSearch, div, inSort, tea8, rle, tHold, intAVG, intFilt |

| EEMBC Embedded Benchmarks [30]                                  |

| AutoCorr, convEn, FFT, Viterbi                                  |

| Complex Benchmarks                                              |

| MergeSort , graph500 [31], highCC                               |

$S_i$   $(S_1, S_2, \ldots, S_{i-1})$ , the Constrained Conservative State (CCS) approach and CS are identical. Since  $S_i$  violates c, it necessarily covers some states that are not reachable by A. Constraining e using c generates  $S'_i$  such that  $S'_i$  covers all possible values that e can assume in A; only unreachable states are eliminated through the application of c. Thus, continuing the simulation from  $S'_i$  will explore all valid states that are reachable by A.

#### 3.4 Evaluation

We perform evaluations on a silicon-proven openMSP430 [26] processor, synthesized, placed and routed in TSMC 65GP (65nm) technology using Synopsys Design Compiler [27] and Cadence EDI System [28]. The processor was implemented for an operating point of 1V and 100MHz. We implemented our constrained conservative state-based scalable symbolic co-analysis in a custom gate-level simulator that was built in-house in C++. We also developed a custom static binary analysis tool in Python for encoding constraints. The static constraints were stored in a JSON file and fed to the custom gatelevel simulator, which the simulator uses for Propagation and Enforcement. We show results for all benchmarks from [29], all EEMBC benchmarks [30] that fit in the program memory of our processor, as well as complex and recursive benchmarks<sup>1</sup> designed to stress-test the scalability of our symbolic hardware-software co-analysis technique with complex control structures not found in the rest of our benchmarks (Table 3.1). Experiments are performed on a server housing two Intel Xeon E-2640 processors (8cores each, 2GHz operating frequency, 64GB RAM).

To illustrate the benefits of our proposed technique for symbolic co-analysis, we

<sup>&</sup>lt;sup>1</sup>MergeSort is a recursive sorting algorithm. graph500 runs BFS on a graph. highCC (high Cyclomatic Complexity) is a synthetic benchmark that uses cyclic array accesses to alter the control flow of the application and has  $16^{32}$  possible control flow paths.

Table 3.2: Constrained conservative state symbolic co-analysis reduces analysis time compared to naive and conservative state-based co-analysis and enables analysis of applications with complex control structures.

| Benchmark    | Analysis Time (Number of Simulation Cycles) |        |       |                           |                            |  |

|--------------|---------------------------------------------|--------|-------|---------------------------|----------------------------|--|

|              | Naive                                       | Consv. | CCS   | %Reduction (w.r.t. Naive) | %Reduction (w.r.t. Consv.) |  |

| div          | $\infty$                                    | 186    | 178   | -                         | 4.30                       |  |

| intAVG       | $\infty$                                    | 337    | 329   | -                         | 2.37                       |  |

| rle          | $\infty$                                    | 7431   | 5951  | -                         | 19.92                      |  |

| rle_small    | 25496                                       | 6495   | 2153  | 91.56                     | 66.85                      |  |

| binSearch    | 100468                                      | 9994   | 1551  | 98.46                     | 84.48                      |  |

| tHold        | 20520                                       | 2615   | 1986  | 90.32                     | 24.05                      |  |

| inSort       | $\infty$                                    | 22205  | 12120 | -                         | 45.42                      |  |

| inSort_small | 24427                                       | 9106   | 5089  | 79.17                     | 44.11                      |  |

| Viterbi      | $\infty$                                    | 69265  | 26389 | -                         | 61.90                      |  |

| MergeSort    | $\infty$                                    | 104574 | 16093 | -                         | 84.61                      |  |

| graph500     | $\infty$                                    | 185341 | 79663 | -                         | 57.02                      |  |

| highCC       | $\infty$                                    | 116290 | 80276 | -                         | 30.90                      |  |

| Benchmark    | Symbolic Execution Paths |        |      |                           |                           |  |  |

|--------------|--------------------------|--------|------|---------------------------|---------------------------|--|--|

|              | Naive                    | Consv. | CCS  | %Reduction (w.r.t. Naive) | %Reduction (w.r.t. Consv. |  |  |

| div          | $\infty$                 | 9      | 7    | -                         | 22.22                     |  |  |

| intAVG       | $\infty$                 | 15     | 13   | -                         | 13.33                     |  |  |

| rle          | $\infty$                 | 129    | 101  | -                         | 21.71                     |  |  |

| rle_small    | 504                      | 113    | 33   | 93.45                     | 70.80                     |  |  |

| binSearch    | 2048                     | 91     | 41   | 98.00                     | 54.95                     |  |  |

| tHold        | 460                      | 247    | 39   | 91.52                     | 84.21                     |  |  |

| inSort       | $\infty$                 | 121    | 67   | -                         | 44.63                     |  |  |

| inSort_small | 476                      | 115    | 65   | 86.34                     | 43.48                     |  |  |

| Viterbi      | $\infty$                 | 771    | 291  | -                         | 62.26                     |  |  |

| MergeSort    | $\infty$                 | 1453   | 235  | -                         | 83.83                     |  |  |

| graph500     | $\infty$                 | 1350   | 1124 | -                         | 16.74                     |  |  |

| highCC       | $\infty$                 | 1604   | 756  | -                         | 52.80                     |  |  |

Table 3.3: Use of constraints reduces the number of explored symbolic execution paths.

Table 3.4: Use of constraints reduces the number of gates identified as exercisable.

| Benchmark    | Exercisable Gates Identified |        |      |                          |                            |  |  |

|--------------|------------------------------|--------|------|--------------------------|----------------------------|--|--|

|              | Naive                        | Consv. | CCS  | %Increase (w.r.t. Naive) | %Reduction (w.r.t. Consv.) |  |  |

| div          | N/A †                        | 3627   | 3566 | -                        | 1.68                       |  |  |

| intAVG       | N/A †                        | 3675   | 3648 | -                        | 0.73                       |  |  |

| rle          | N/A †                        | 4488   | 3759 | -                        | 16.24                      |  |  |

| rle_small    | 3185                         | 4487   | 3740 | 17.43                    | 16.65                      |  |  |

| binSearch    | 3065                         | 3454   | 3424 | 11.71                    | 0.87                       |  |  |

| tHold        | 2893                         | 3530   | 3368 | 16.42                    | 4.59                       |  |  |

| inSort       | N/A †                        | 5406   | 3518 | -                        | 34.92                      |  |  |

| inSort_small | 3134                         | 5418   | 3523 | 12.41                    | 34.98                      |  |  |

| Viterbi      | N/A †                        | 5449   | 5449 | -                        | 0.00                       |  |  |

| MergeSort    | N/A †                        | 5134   | 4294 | -                        | 16.36                      |  |  |

| graph500     | N/A †                        | 5988   | 5987 | -                        | 0.02                       |  |  |

| highCC       | N/A †                        | 4007   | 3558 | -                        | 11.20                      |  |  |

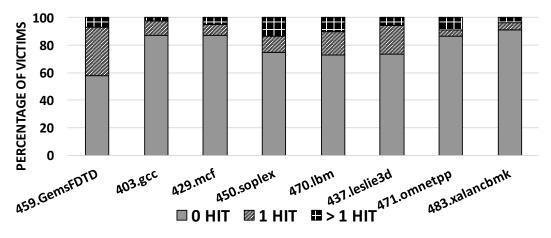

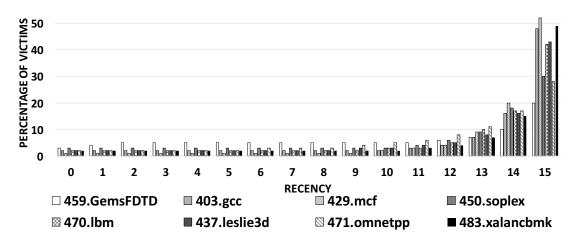

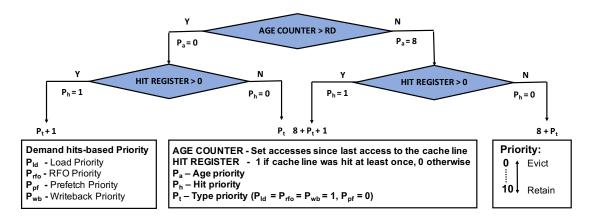

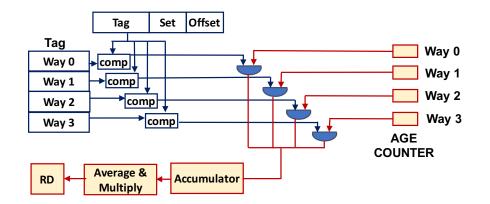

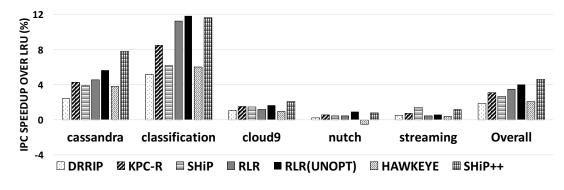

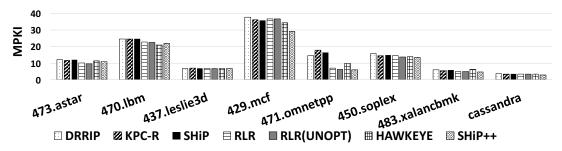

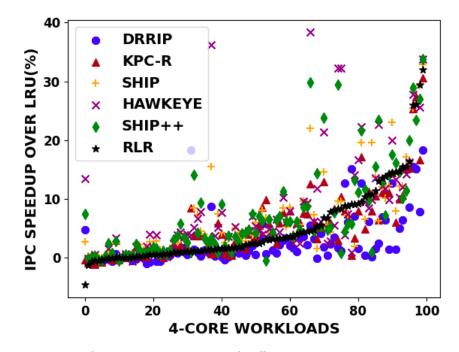

† Since these simulations did not finish, naive simulation would be forced to report that all 7218 gates of the design might be exercisable.