### Energy Efficient Computing with Time-Based Digital Circuits

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL UNIVERSITY OF MINNESOTA

BY

Luke R. Everson

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Prof. Chris H. Kim, Advisor

May 2019

### Acknowledgements

The PhD has been a special journey, and although it is a tremendous personal achievement, it has been the furthest thing from a singular effort. I cannot thank my wife, Megan, enough for her ceaseless support, love, and patience through these past four years. I have joked that she has heard me rehearse presentations enough, so that if I were to fall down the stairs on the day of a talk, she could give them in my place! Even through the seemingly perpetual challenges during this PhD, we grew stronger as a couple and always put our commitment to each other first.

I am fortunate that my family has always been there to encourage me. My in-laws deserve credit for their enduring patience in many regards as at times this investment might not have always looked like it would come to fruition. My parents have been the biggest influence in my life, and I am lucky for that because they have lived a life that I am proud to follow.

I treasure this opportunity afforded to me by Professor Kim. His support and vision gave me intellectual freedom to create some very creative, unconventional circuits. The relentless pursuit of simple, elegant, and intuitive designs drove me each and every day to give my best. At times it wasn't always easy, but I will forever cherish the time I got to work in his lab.

My committee members; Professor Sapatnekar, Professor Parhi, and Professor Yang have provided a sounding board for some of my work and their encouragement was instrumental during my career. I am also grateful for the time they spent reading this thesis and providing insightful comments.

My group members; Ibrahim Ahmed, Muqing Liu, Po Wei Chiu, Gyusung Park, Nakul Pande, Minsu Kim, Jeehwan Song, Chen Zhou, Saurabh Kumar, Qianying Tang (VLSI I & II TA, owe her a great deal of thanks for teaching me the tools), Somnath Kundu, Jongyeon Kim, Won Ho Choi, and Hoonki Kim were an ideal audience for vetting new ideas at team meetings, helping at any time with measurements or to discuss a circuit. I was fortunate to have them as colleagues, and now as friends. I also want to thank Kim Lab alumni John Keane for the mentorship during summer 2018.

This journey actually began during my junior year of undergraduate study in Professor David Lilja's lab under the direction of Dr. Manas Minglani. This opportunity was initiated by the Department, of which I am grateful for the financial support, academic advising, and providing a relevant and engaging curriculum. Additional research experiences along the way enriched my skillset and broadened my mindset. I want to thank Robert Lattin of Thermo King for building my confidence in hands-on engineering. Dr. Dwaipayan Biswas, Dr. Nick Van Helleputte and Dr. Chris Van Hoof of imec for providing an environment unparalleled for innovation, and Wes Santa and Dr. Erik Peterson of Medtronic for mentorship during the final year of my study.

### **Dedication**

For Megan

#### **Abstract**

Advancements in semiconductor technology have given the world economical, abundant, and reliable computing resources which have enabled countless breakthroughs in science, medicine, and agriculture which have improved the lives of many. Due to physics, the rate of these advancements is slowing, while the demand for the increasing computing horsepower ever grows. Novel computer architectures that leverage the foundation of conventional systems must become mainstream to continue providing the improved hardware required by engineers, scientists, and governments to innovate. This thesis provides a path forward by introducing multiple time-based computing architectures for a diverse range of applications. Simply put, time-based computing encodes the output of the computation in the time it takes to generate the result. Conventional systems encode this information in voltages across multiple signals; the performance of these systems is tightly coupled to improvements in semiconductor technology. Time-based computing elegantly uses the simplest of components from conventional systems to efficiently compute complex results. Two time-based neuromorphic computing platforms, based on a ring oscillator and a digital delay line, are described. An analog-to-digital converter is designed in the time domain using a beat frequency circuit which is used to record brain activity. A novel path planning architecture, with designs for 2D and 3D routes, is implemented in the time domain. Finally, a machine learning application using time domain inputs enables improved performance of heart rate prediction, biometric identification, and introduces a new method for using machine learning to predict temporal signal sequences. As these innovative architectures are presented, it will become clear the way forward will be increasingly enabled with time-based designs.

### **Table of Contents**

| List of T        | Tablesx                                                                        |

|------------------|--------------------------------------------------------------------------------|

| List of F        | Figuresxi                                                                      |

| Chapter 1.       | Introduction1                                                                  |

| 1.1 Tim          | ne-based Neuromorphic Circuits                                                 |

| 1.1.1            | A Scalable Time-Based Integrate-&-Fire Digitally Controlled Oscillator 2       |

| 1.1.2            | A One-Shot Neuromorphic Core with Dynamic Threshold Error Correction           |

|                  | 2                                                                              |

| 1.2 Tim          | ne-based Graph Computing                                                       |

| 1.2.1            | A 40×40 2D Gradient-enabled A* Path Planning ASIC                              |

| 1.2.2            | A 20 <sup>3</sup> cube for 3D Graph Traversal                                  |

| 1.3 Tim          | ne-based Biosignal Recording System                                            |

| 1.4 Tim          | ne-based Photoplethysmography Machine Learning Algorithms 4                    |

| 1.4.1<br>Worn P. | BiometricNET: Deep Learning based Biometric Identification using Wrist-<br>PG4 |

| 1.4.2            | CorNET: Deep Learning Framework for PPG based Heart Rate Estimation 5          |

| 1.4.3            | BioTranslator: Deep Learning Framework for Converting Time Series              |

| Biosign          | als                                                                            |

| Chapter 2.       | Time-based Neuromorphic Circuits7                                              |

| 2.1 Intr         | oduction                                                                       |

| 2.1.1            | Time-based Neuromorphic Foundations                                            |

| 2.1.2            | Alternative Neuromorphic Architectures                                         |

| 2.1.2.           | 1 Digital Systems-on-Chip                                                      |

| 2.1.2.           | 2 Analog SRAM Solutions 9                                                      |

| 2.1.2.           | .3 Analog Neuromorphic Systems                                                 |

| 2.1.2      | .4 Digital SRAM Crossbar                                             | 10     |

|------------|----------------------------------------------------------------------|--------|

| 2.1.2      | .5 Non-volatile Crossbar Designs                                     | 11     |

| 2.2 A S    | Scalable Time-Based Integrate-&-Fire Digitally Controlled Oscillator | 13     |

| 2.2.1      | Integrate-&-Fire Architecture and Concept                            | 13     |

| 2.2.2      | Leak and Local Lateral Inhibition Technique                          | 18     |

| 2.2.3      | Application and Measurement Results                                  | 19     |

| 2.2.4      | Conclusions                                                          | 24     |

| 2.3 An     | Energy Efficient Time-Based One-Shot Neuromorphic Chip               | 25     |

| 2.3.1      | One-Shot Neuromorphic Architecture                                   | 25     |

| 2.3.2      | TDC Performance Analysis                                             | 28     |

| 2.3.3      | Dynamic Threshold Error Correction (DTEC)                            | 33     |

| 2.3.4      | Application and Measurement Results                                  | 36     |

| 2.3.5      | Conclusions                                                          | 40     |

| 2.4 Su     | nmary                                                                | 41     |

| Chapter 3. | Time-based Graph Computing                                           | 42     |

| 3.1 A      | 0×40 Four-Neighbor Time-Based In-Memory Computing Graph ASI          | C Chip |

| Featuring  | Wavefront Expansion and 2D Gradient Control                          | 42     |

| 3.1.1      | Introduction                                                         | 42     |

| 3.1.2      | Principle of Operation                                               | 45     |

| 3.1.2      | .1 Vertex Circuit Functionality                                      | 46     |

| 3.1.2      | .2 Edge Unit                                                         | 49     |

| 3.1.2      | .3 Gradient A* Mapping                                               | 50     |

| 3.1.3      | Measurement Results                                                  | 52     |

| 3.1.4      | Applications                                                         | 55     |

| 3.1.4      | .1 Collision Avoidance through Voronoi Diagrams                      | 55     |

| 3      | 3.1.4. | 2 Shortest Path Planning                                    | 58  |

|--------|--------|-------------------------------------------------------------|-----|

| 3      | 3.1.4. | 3 Multi-core Scalability                                    | 60  |

| 3      | 3.1.4. | 4 Optics Experiment                                         | 61  |

| 3.1    | .5     | Conclusion                                                  | 62  |

| 3.2    | 3D     | Graph Traversal ASIC                                        | 63  |

| 3.2    | .1     | Introduction                                                | 63  |

| 3.2    | .2     | Architecture Details                                        | 63  |

| 3      | 3.2.2. | 1 Array Structure                                           | 63  |

| 3      | 3.2.2. | 2 Vertex Operation                                          | 67  |

| 3.2    | .3     | Measurement Details                                         | 70  |

| 3.2    | .4     | Applications                                                | 72  |

| 3      | 3.2.4. | 1 3D Navigation                                             | 72  |

| 3      | 3.2.4. | 2 Voronoi Diagrams                                          | 74  |

| 3      | 3.2.4. | 3 k-Nearest Neighbor Classification                         | 75  |

| 3.2    | .5     | Conclusion                                                  | 78  |

| Chapte | r 4.   | Time-based Biosignal Recording System                       | .79 |

| 4.1    | Intr   | oduction                                                    | 79  |

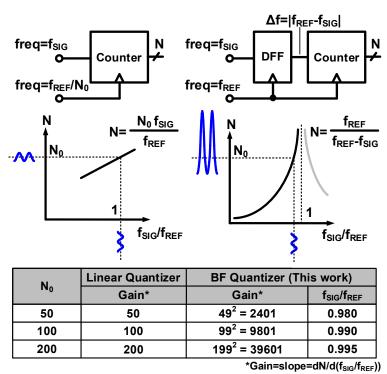

| 4.2    | Bea    | t Frequency ADC                                             | 81  |

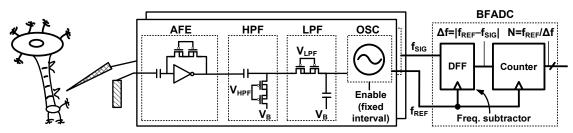

| 4.3    | Test   | t Chip Organization                                         | 84  |

| 4.3    | .1     | Analog Front End Circuit                                    | 85  |

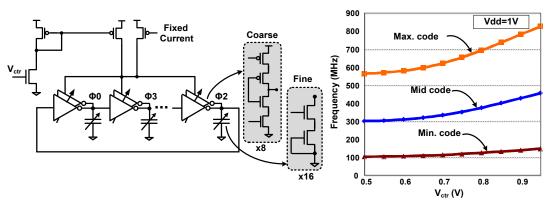

| 4.3    | .2     | Current Controlled Oscillator                               | 86  |

| 4.4    | Mea    | asurement Results                                           | 87  |

| 4.5    | Res    | ults of <i>In-vivo</i> Experiment                           | 90  |

| 4.6    | Con    | nclusion                                                    | 91  |

| Chapte | r 5.   | Time-based Photoplethysmography Machine Learning Algorithms | .92 |

| 5.1<br>PPG |        | metricNet: Deep Learning based Biometric Identification using Wrist-Wo | orn |

|------------|--------|------------------------------------------------------------------------|-----|

| 5.1        | .1     | Introduction                                                           | 92  |

| 5.1        | .2     | IEEE 2015 Signal Processing Cup Dataset                                | 94  |

| 5.1        | .3     | Problem Formulation                                                    | 96  |

| 5.1        | .4     | BiometricNet Framework                                                 | 97  |

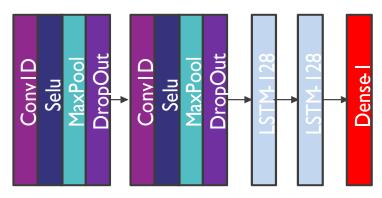

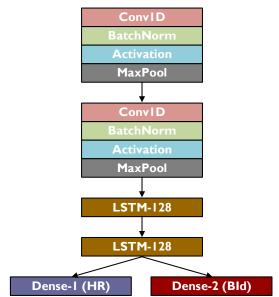

| 4          | 5.1.4. | .1 Deep Neural Network: CNN + LSTM                                     | 98  |

| 4          | 5.1.4. | 2 BiometricNet Architecture                                            | 99  |

| 4          | 5.1.4. | 3 Implementation Details                                               | 100 |

| 5.1        | .5     | Results                                                                | 101 |

| 5.1        | .6     | Conclusion                                                             | 104 |

| 5.2        | Cor    | NET: Deep Learning framework for PPG based Heart Rate Estimation a     | and |

| Biom       | etric  | Identification in Ambulant Environment                                 | 105 |

| 5.2        | 2.1    | Introduction                                                           | 105 |

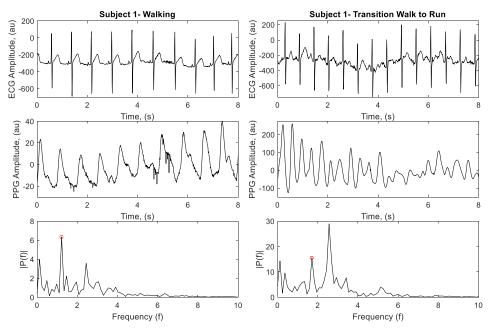

| 5.2        | 2.2    | Prior Art                                                              | 107 |

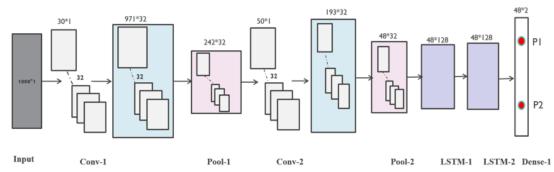

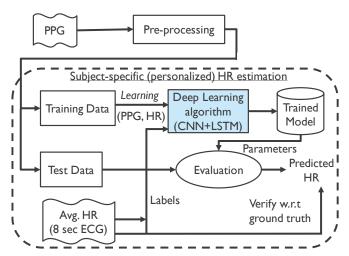

| 5.2        | 2.3    | Problem Formulation                                                    | 109 |

| 5.2        | 2.4    | CorNET Framework                                                       | 110 |

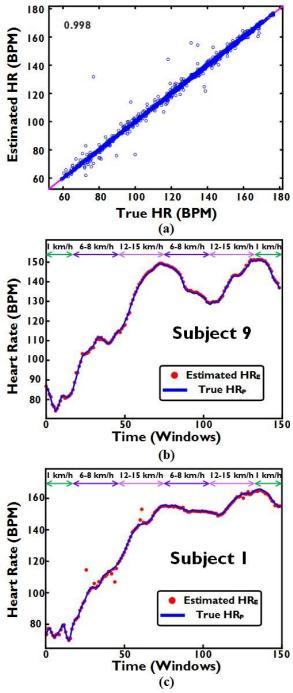

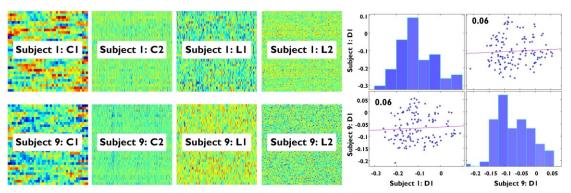

| 5.2        | 2.5    | Results and Analysis                                                   | 111 |

| 5.2        | 2.6    | Conclusion                                                             | 116 |

| 5.3        | Bio    | Translator: Inferring R-Peaks from Ambulatory Wrist-Worn PPG Signal 1  | 17  |

| 5.3        | .1     | Introduction                                                           | 117 |

| 5.3        | .2     | Prior Work in HRV Prediction                                           | 118 |

| 5.3        | .3     | Problem Formulation                                                    | 120 |

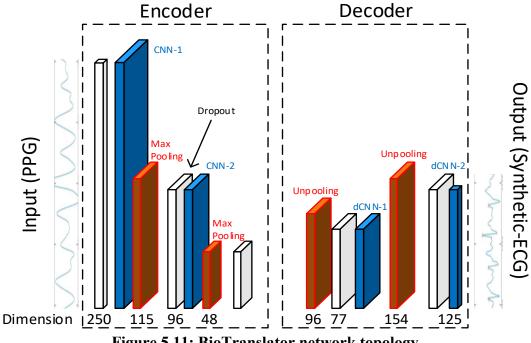

| 5.3        | .4     | BioTranslation Framework                                               | 122 |

|            | 5.3.4. | Deep Neural Network Essentials                                         | 122 |

| 4          | 5.3.4. | 2 Experimental Setup Details                                           | 123 |

| Bibliography133 |                      |     |

|-----------------|----------------------|-----|

| Chapter 6.      | Conclusion           | 130 |

| 5.3.6           | Conclusion           | 129 |

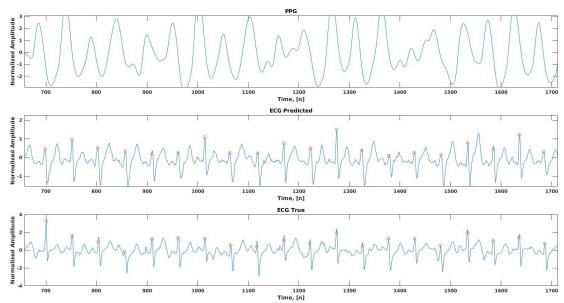

| 5.3.5           | Results and Analysis | 125 |

### **List of Tables**

| Table 2.1: Performance Comparison                            | 22  |

|--------------------------------------------------------------|-----|

| Table 2.2: DDL Delay for increasing chain lengths            | 31  |

| Table 2.3: Performance Comparison Table                      | 39  |

| Table 3.1: Comparison Table                                  | 54  |

| Table 4.1: Performance Comparison                            | 88  |

| Table 5.1: Parameter Grid Search Results                     | 102 |

| Table 5.2: Performance of <i>BiometricNet</i> on SPC Dataset | 104 |

| Table 5.3: Performance Comparison for <i>HR</i> estimation   | 115 |

| Table 5.4: Activity Dependent Performance for Subject 1      | 115 |

| Table 5.5: R Peak Prediction Results on SPC Dataset          | 127 |

| Table 5.6: Time Domain Metrics                               | 127 |

| Table 5.7: BioTranslator Complexity Analysis                 | 128 |

### **List of Figures**

| Figure 2.1: Time-based neurons utilize the delay through basic circuit elements such as  |

|------------------------------------------------------------------------------------------|

| inverters to implement the dot-product                                                   |

| Figure 2.2: Conceptual circuit diagram of the proposed time-based integrate & fire (I&F) |

| DCO neuromorphic core                                                                    |

| Figure 2.3: Detailed implementation of programmable delay stage and unit cell layout. 14 |

| Figure 2.4: Time-based DCO neuromorphic architecture                                     |

| Figure 2.5: Measured DCO Frequency before and after tuning                               |

| Figure 2.6: Illustration of time-based leaky neuron and local lateral inhibition (LLI)   |

| operation                                                                                |

| Figure 2.7: Effect of leak and LLI features                                              |

| Figure 2.8: Multi-layer digit recognition test architecture and summary for time-based   |

| neuromorphic chip demonstration. 20                                                      |

| Figure 2.9: Measured application results.                                                |

| Figure 2.10: Example of measured output from one digit                                   |

| Figure 2.11: Measured power consumption and DCO frequency for the I&F core 23            |

| Figure 2.12: Die photo and performance summary                                           |

| Figure 2.13: Top Schematic of the one-shot time-based neuromorphic core                  |

| Figure 2.14: (Top) Schematic of pixel stage. (Bottom) Layout of pixel element            |

| Figure 2.15: (Left) Complex tristate wiring. (Right) Trained weight to DU stages 26      |

| Figure 2.16: Timing details of the 2 bit TDC.                                            |

| Figure 2.17: Measured data from chip calibration across 10 DDLs                          |

| Figure 2.18: Post-layout simulation of DU linearity                                      |

| Figure 2.19: DTEC operating concept illustrated where reference DDL bias is swept to     |

|------------------------------------------------------------------------------------------|

| boost TDC resolution. 33                                                                 |

| Figure 2.20: Measured effectiveness of DTEC, first rows show ambiguous prediction and    |

| as bias is swept winner is isolated                                                      |

| Figure 2.21: Distribution of activation outputs in a 2 layer neural network              |

| Figure 2.22: Measurement results on MNIST application                                    |

| Figure 2.23: Dataflow for multilayer neural network with binary inputs                   |

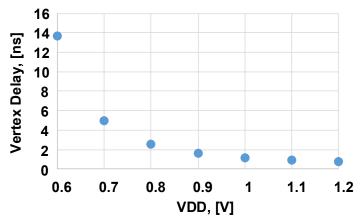

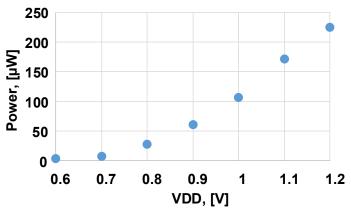

| Figure 2.24: Power dissipation of a single DDL and delay/stage across VDD                |

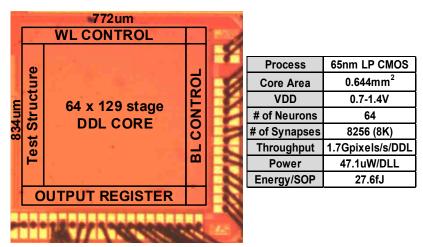

| Figure 2.25: Chip micrograph and chip summary (metrics reported at nominal supply). 39   |

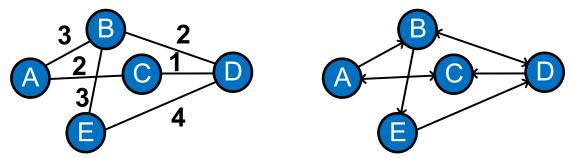

| Figure 3.1: Examples of an integer weighted undirected graph (left) and unweighted       |

| directed graph (right)                                                                   |

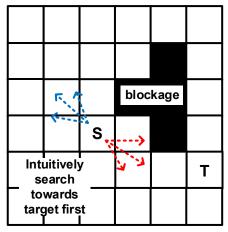

| Figure 3.2: Illustration of the intuition of the A* heuristic                            |

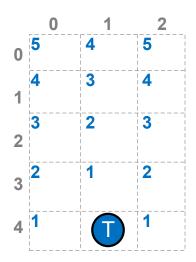

| Figure 3.3: Manhattan Distance as the heuristic in A* SSP                                |

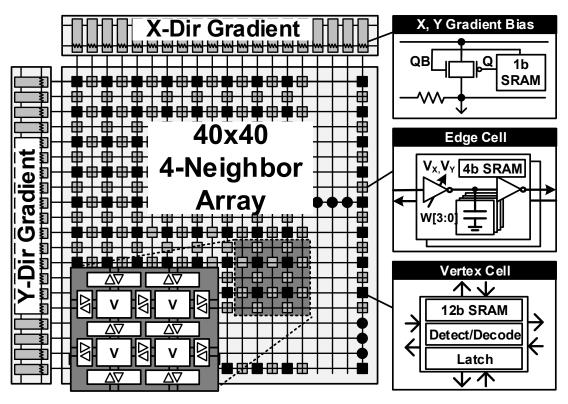

| Figure 3.4: 40x40 graph ASIC chip for solving single-source shortest path problems based |

| on 2-dimensional wavefront expansion. 45                                                 |

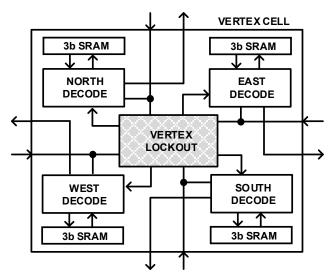

| Figure 3.5: Block diagram of the vertex.                                                 |

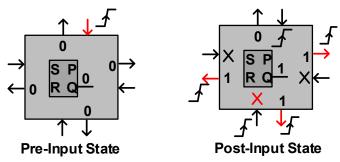

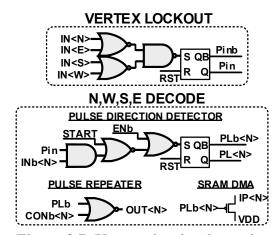

| Figure 3.6: Operation of the lockout mechanism                                           |

| Figure 3.7: Vertex circuit schematic                                                     |

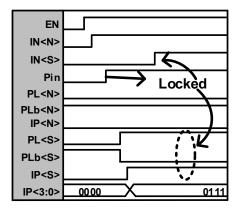

| Figure 3.8: Vertex timing diagram of lockout functionality                               |

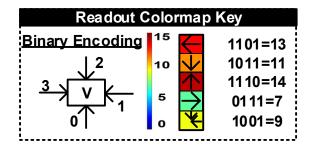

| Figure 3.9: Local SRAM storage encoding enabling traceback                               |

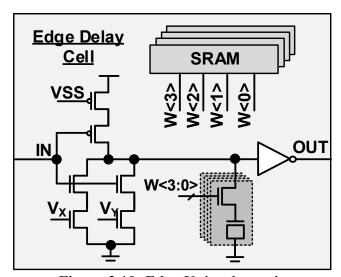

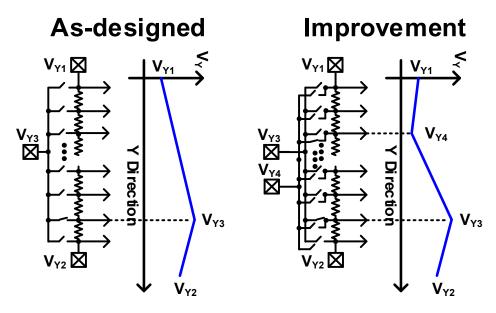

| Figure 3.10: Edge Unit schematic                                                         |

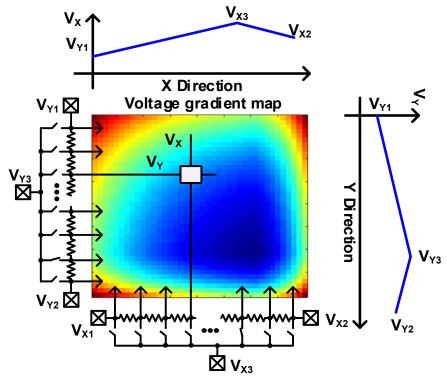

| Figure 3.11: Functional example of the gradient ladder                                   |

| Figure 3.12: Possible Wavefront shaping with increased gradient complexity               |

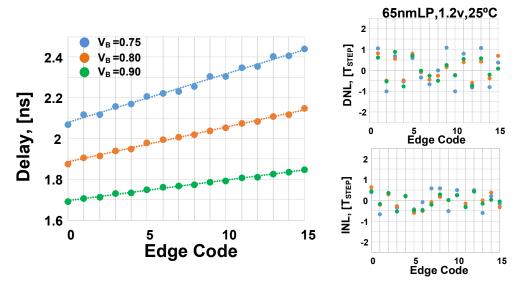

| Figure 3.13: Measured delay of the edge cell                                      | 53           |

|-----------------------------------------------------------------------------------|--------------|

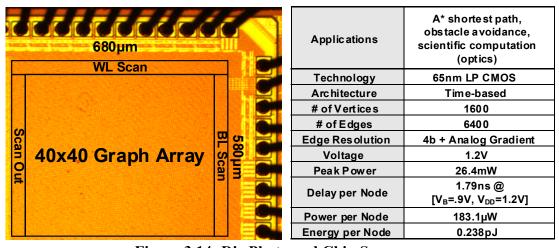

| Figure 3.14: Die Photo and Chip Summary                                           | 55           |

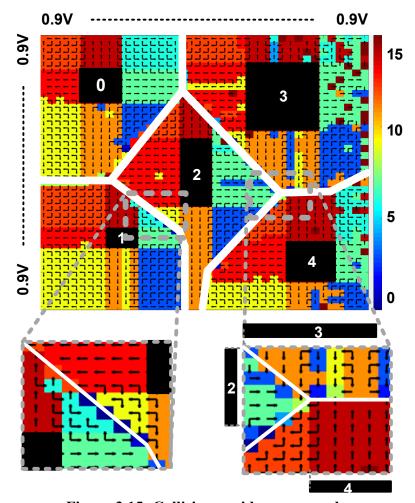

| Figure 3.15: Collision avoidance example                                          | 57           |

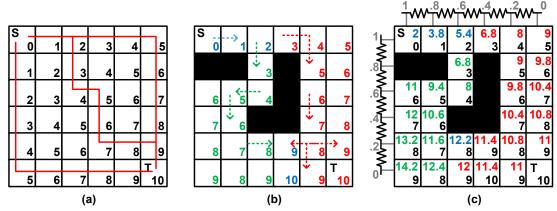

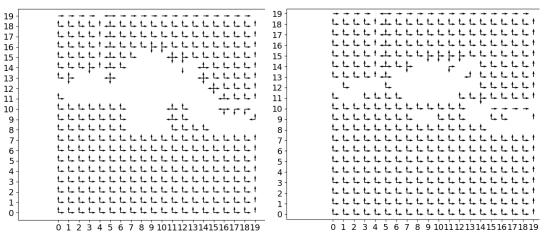

| Figure 3.16: Path Planning on grids (a) costs from Dijkstra's (b) Dijkstra's with | ı blockages  |

| (c) A* via gradient                                                               | 58           |

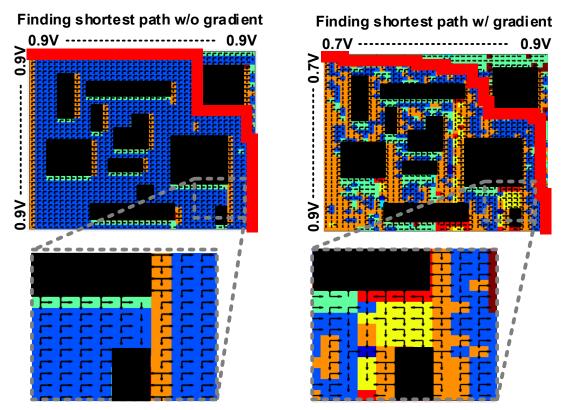

| Figure 3.17: Measured results from path planning application without (left) and   | with (right) |

| the gradient.                                                                     | 59           |

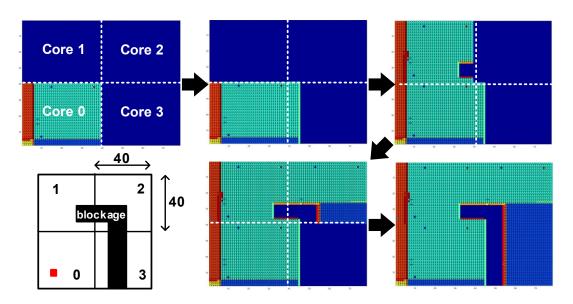

| Figure 3.18: Four-core example with time-multiplexed outputs interleaved to       | shown full   |

| map                                                                               | 60           |

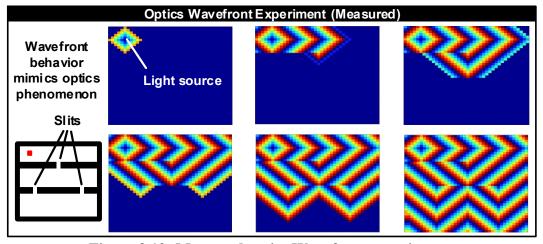

| Figure 3.19: Measured optics Wavefront experiment.                                | 61           |

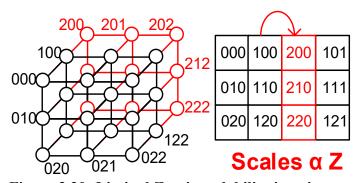

| Figure 3.20: Limited Z-axis scalability in prior art                              | 64           |

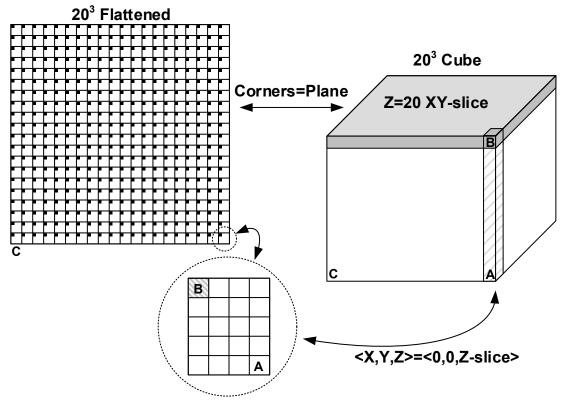

| Figure 3.21: Mapping between 3D cube and 2D planar layout.                        | 65           |

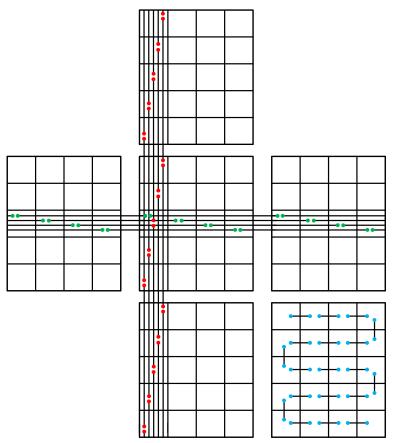

| Figure 3.22: Global routing across the three dimensions.                          | 66           |

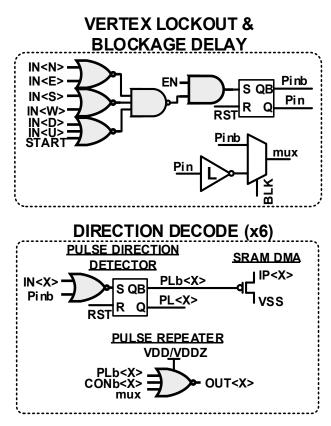

| Figure 3.23: Circuit schematic of vertex cell                                     | 67           |

| Figure 3.24: Measured average delay of each vertex                                | 70           |

| Figure 3.25: Post-Layout Simulation of Power                                      | 71           |

| Figure 3.26: Die Photo and Chip Summary                                           | 72           |

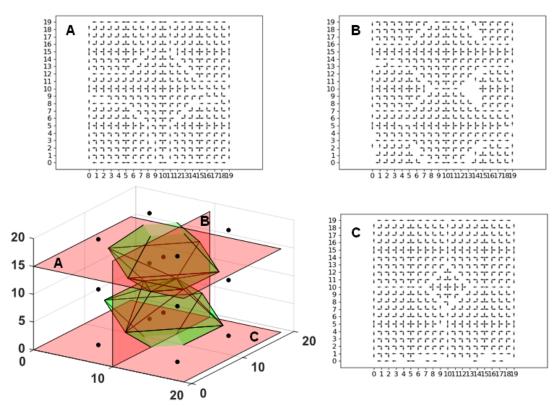

| Figure 3.27: Example of the 3D Navigation application.                            | 73           |

| Figure 3.28: Readout of the chip of the Z=0 (left) and Z=2 (right) plane          | 74           |

| Figure 3.29: 3D Voronoi diagram via 2D reconstruction                             | 75           |

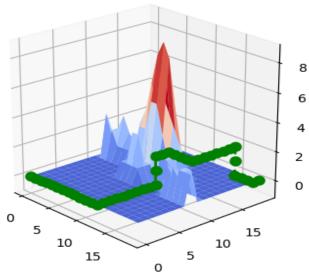

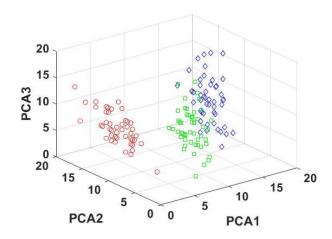

| Figure 3.30: Fisher's Iris dataset prepared for the chip                          | 76           |

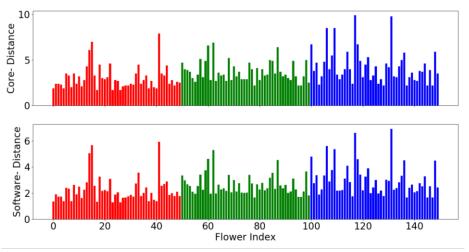

| Figure 3.31: Measured kNN distance for k=10                                       | 77           |

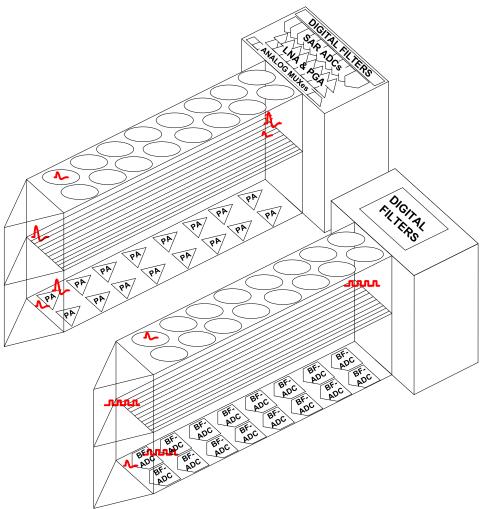

| Figure 4.1: (Above) Conventional shank-based neural recording system [3]. (Below)                  |

|----------------------------------------------------------------------------------------------------|

| Envisioned BFADC system. 80                                                                        |

| Figure 4.2: Comparison between linear VCO-based quantizer and BF-quantizer 82                      |

| Figure 4.3: Schematic representation of the implemented neural recording BFADC test                |

| chip                                                                                               |

| Figure 4.4: (Left) Schematic of current controlled oscillator and (Right) parasitic-extracted      |

| simulated range [48]                                                                               |

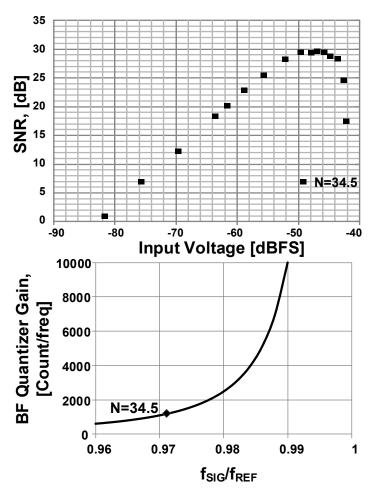

| Figure 4.5: (Above) Measured SNDR vs. input amplitude. (Below) BF quantizer gain plot.             |

|                                                                                                    |

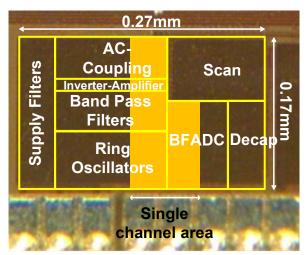

| Figure 4.6: Die photo of the test chip in 65nm LP CMOS. Box highlighted in orange                  |

| represents the area of a single channel                                                            |

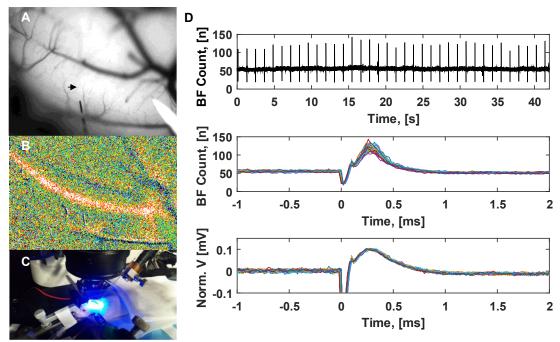

| Figure 4.7: Results from the in-vivo recording experiment                                          |

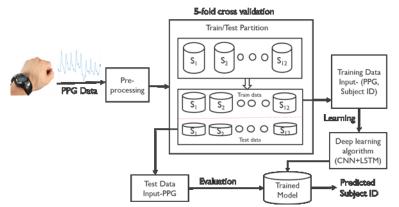

| Figure 5.1: Overview of the proposed methodology for biometric identification 97                   |

| Figure 5.2: BiometricNet topology                                                                  |

| Figure 5.3: Details of the filter sizes used in <i>BiometricNet</i> found from the grid search 101 |

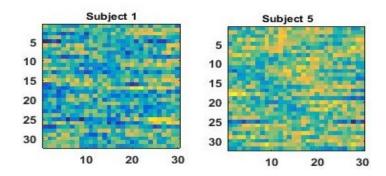

| Figure 5.4: Difference in dense layer weights between subject 1 and 5                              |

| Figure 5.5: Raw ECG, PPG signal and spectrum while walking (left) and during transition            |

| from walking to running (right) respectively. The highest PPG spectral peak does not               |

| coincide with true HR (encircled) during intense motion                                            |

| Figure 5.6: HR Estimation methodology and dataflow                                                 |

| Figure 5.7: CorNET (HR) and BiometricNET (BId) share the same feature extraction                   |

| engine                                                                                             |

| Figure 5.8: Results from the <i>HR</i> estimation problem                                          |

| Figure 5.9: Weights of <i>CorNET</i> for subject 1 and 9                | 114              |

|-------------------------------------------------------------------------|------------------|

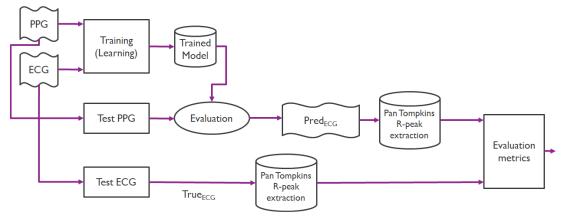

| Figure 5.10: Overview of the novel signal transformation methodology f  | or estimating R- |

| peaks.                                                                  | 121              |

| Figure 5.11: BioTranslator network topology                             | 124              |

| Figure 5.12: An illustration of PPG, predicted and true ECG, with the R | -peaks (obtained |

| through Pan Tompkins) marked over them.                                 | 128              |

### **Chapter 1.** Introduction

The uniting theme for all the work in this thesis is time. In Chapters 2, 3, and 4, time is used as the state variable in the computation. Traditional computing uses voltage as the state variable; digital recognizes binary states of "on" and "off" or VDD and VSS to encode computation. Analog computers use a real-valued representation of the voltage to encode a value with infinite resolution. Time based circuits encode the computation value in the evaluation time. This idea has recently been gained popularity [1] due to the flattening of Moore's law [2]. However, the idea of encoding data in time delays is nothing new. In a seminal review [3] of digital computer memories, delay-line memories are described to be used by injecting a pattern into a medium, such as mercury, which delays the propagation of the pattern until it reaches the end of the medium and it is read out. The purpose of these memories was to store, or delay, the information from the time it was generated until the time the next computation could use it. This paradigm is no different than that of some of the work presented in this thesis; time-based computing can be used to when digital systems fall short. In Chapter 5, temporal signals are used directly for computing, compared to conventional methods which derive features from the signals and compute on those. To meet the requirements of modern applications in the face of slowing technical innovation, time-based computing architectures will be presented on a diverse set of applications; neuromorphic and machine learning, analog to digital conversion, graph computing, and biosignal processing.

### 1.1 Time-based Neuromorphic Circuits

### 1.1.1 A Scalable Time-Based Integrate-&-Fire Digitally Controlled Oscillator

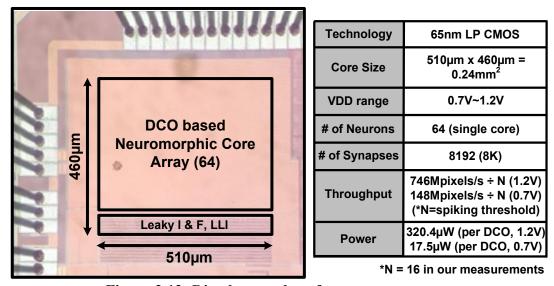

A fully scalable light-weight integrate-and-fire neuromorphic core with brain-inspired leak and local lateral inhibition features is implemented in 65nm. The core computes the neural net algorithm entirely in the time domain using standard digital circuits. A parallel two-layer architecture realized using the proposed core achieves a 91% handwritten digit recognition accuracy. The 0.24mm² neuromorphic core including 64 digitally controlled oscillator (DCO) circuits consumes 320.4μW per DCO at a maximum throughput of 746M pixels/s.

### 1.1.2 A One-Shot Neuromorphic Core with Dynamic Threshold Error Correction

As neural networks continue to infiltrate diverse application domains, computing will begin to move out of the cloud and onto edge devices necessitating fast, reliable, and low power solutions. To meet these requirements, a time-domain core using one-shot delay measurements and a lightweight post processing technique, Dynamic Threshold Error Correction (DTEC) will be presented. This design differs from traditional digital implementations in that it uses the delay accumulated through a simple inverter chain distributed through an SRAM array to intrinsically compute resource intensive multiply-accumulate (MAC) operations. Implemented in 65nm LP CMOS, the design achieves an energy efficiency of 104.8TOp/s/W at 0.7V with 3b resolution for 19.1fJ/MAC.

### 1.2 Time-based Graph Computing

### 1.2.1 A 40×40 2D Gradient-enabled A\* Path Planning ASIC

A mixed-signal time-based 65nm application specific integrated circuit is developed for solving shortest-path problems. The core follows similar principles from wave routing and additionally incorporates a gradient on the periphery of the core to implement the A\* algorithm. A leading pulse is propagated from start nodes and is asynchronously latched in neighboring vertex cells and pushed to its four neighbors. Applications include collision avoidance for self-driving cars, shortest path planning, scientific computing, and is shown to be scalable across many cores. The chip achieves 559 million traversed edges per second at 10<sup>5</sup>× improved energy efficiency compared to existing platforms such as FPGA and CPU. The processor operates nominally at 1.79ns per node with peak power consumption of 26.4mW.

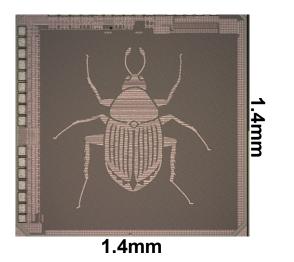

### 1.2.2 A 20<sup>3</sup> cube for 3D Graph Traversal

Building on the work presented in the prior section, the primary limitation of adopting the 2D path finding framework in drones and UAVs is the lack of the vertical spatial dimension. This has been addressed in the 20<sup>3</sup> cube purpose designed for drone navigation. A novel 3D-to-2D transformation is developed to create a practical, scalable architecture in standard 2D CMOS. A diverse range of applications including path planning, routing, 3D Voronoi diagram generation, and k nearest neighbor classification is demonstrated on the core. The chip achieves throughput of 1.38 billion traversed edges per second at 0.162pJ/node at 1.2V in a 2mm<sup>2</sup> die area making it ideal path planner for resource constrained platforms such as quadcopters.

### 1.3 Time-based Biosignal Recording System

A digital-intensive, low-area, time-based ADC optimized for in-situ neural recording is fabricated in a 65nm test chip and validated with *in-vivo* data. The intrinsic inversely proportional gain of a beat frequency based quantizer allows recording of sub-millivolt neural signals without any sophisticated amplifiers or filters. A low-area analog-front-end (AFE) is implemented with a standard digital logic inverter transimpedance amplifier and tunable low pass and high pass filters. The test chip achieves 20.9dB SNDR for a 1mVpp input at 416Hz with a bandwidth of 4.2 kHz and consumes 52μW at 0.8V. *In-vivo* evoked potentials and spontaneous activity were measured directly from a mouse cerebellum without any external components, validating the efficacy of the aggressive tradeoffs. These results are achieved in an area of 0.0094mm²/channel, including on-chip AC coupling and filter passives, which makes this an attractive architecture for complete integration in ultrahigh channel count neural recording systems.

## 1.4 Time-based Photoplethysmography Machine Learning Algorithms

### 1.4.1 BiometricNET: Deep Learning based Biometric Identification using Wrist-Worn PPG

Rapid advances in semiconductor fabrication technology have enabled the proliferation of miniaturized body-worn sensors capable of long term pervasive biomedical signal monitoring. In this section, a novel deep learning-based framework (BiometricNET) on biometric identification using data collected from wrist-worn Photoplethysmography

(PPG) signals in ambulatory environments will be presented. A completely personalized data-driven approach is formulated, using a four-layer deep neural network - employing two convolution neural network (CNN) layers in conjunction with two long short-term memory (LSTM) layers, followed by a dense output layer for modelling the temporal sequence inherent within the pulsatile signal representative of cardiac activity. The proposed network configuration was evaluated on the TROIKA dataset collected from 12 subjects involved in physical activity, achieved an average five-fold cross-validation accuracy of 96%.

### 1.4.2 CorNET: Deep Learning Framework for PPG based Heart Rate Estimation

The proliferation of miniaturized body-worn sensors capable of long-term pervasive biomedical signal monitoring has ignited a data revolution in healthcare. Remote cardiovascular monitoring has been one of the beneficiaries of this development, resulting in non-invasive, photoplethysmography (PPG) sensors being used in ambulatory settings. Wrist-worn PPG, although a popular alternative to electrocardiogram (ECG), inferring cardiac information (e.g. heart rate) is challenging owing to artifacts induced by motion inherent in daily life. Hence, in this chapter, a novel deep learning framework (CorNET) to efficiently estimate heart rate (HR) information and perform biometric identification (BId) using only wrist-worn, single-channel PPG signal collected in ambulant environment is described. A completely personalized data-driven approach is formulated, using a four-layer deep neural network - employing two convolution neural network layers in conjunction with two long short-term memory layers, followed by a dense output layer for modelling the temporal sequence inherent within the pulsatile signal representative of

cardiac activity. The final dense layer is customized with respect to the application, functioning as: a) regression layer - having a single neuron to predict HR; b) classification layer - two neurons which identifies a subject among a group. The proposed network was evaluated on the TROIKA dataset having 23 PPG records collected during various physical activities, achieved mean absolute error of 0.48±0.19 BPM for HR estimation and an average accuracy of 96% for BId on 20 subjects.

### 1.4.3 BioTranslator: Deep Learning Framework for Converting Time Series Biosignals

Advancements in wireless sensor networks (WSN) technology and miniaturization of wearable sensors have enabled long-term continuous pervasive biomedical signal monitoring. Wrist-worn photoplethysmography (PPG) sensors have gained popularity given their form factor. However the signal quality suffers due to motion artifacts when used in ambulatory settings, making vital parameter estimation a challenging task. In this section, a novel deep learning framework, BioTranslator, is presented for computing the instantaneous heart rate (IHR), using wrist-worn PPG signals collected during physical activity. Using one-dimensional Convolution-Deconvolution Network, it translates a single channel PPG signal to an electrocardiogram (ECG)-like time series signal, from which relevant R-peak information can be inferred enabling IHR measures. The proposed network configuration was evaluated on 12 subjects of the TROIKA dataset, involved in physical activity. The proposed network identifies 92.8% of R-peaks, besides achieving a mean absolute error of 51ms with respect to reference ECG-derived IHR.

### **Chapter 2.** Time-based Neuromorphic Circuits

### 2.1 Introduction

Machine Learning (ML) has become one of the hottest topics in mainstream research as well as IC design. The incredible performance on diverse applications has made it a silver bullet for problems typically ill-suited for traditional computers [4]. This has led to a proliferation of custom silicon solutions targeted at meeting the demand [5]. The remainder of this section will introduce time-based neuromorphic computing and compare and contrast to alternative neuromorphic architectures proposed in the literature. In Section 2.2 A Scalable Time-Based Integrate-&-Fire Digitally Controlled Oscillator is described [6]. Next, Section 2.3 details An Energy Efficient Time-Based One-Shot Neuromorphic Chip [5]. Finally, conclusions will be drawn in Section 2.4.

### 2.1.1 Time-based Neuromorphic Foundations

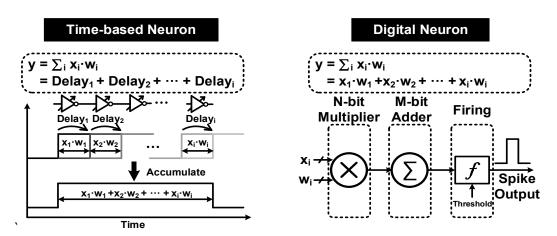

Figure 2.1: Time-based neurons utilize the delay through basic circuit elements such as inverters to implement the dot-product.

Equation 2.1 shows the characteristic kernel in ML is the dot-product:

$$y = \sum_{i} x_{i} \cdot w_{i}$$

2.1

Here  $x_i$  is the input data and  $w_i$  is the synaptic weight learned during the training phase of the application. Time-based neurons utilize the delay through basic circuit elements such as inverters to implement the multiplication. The primary benefit of time-domain circuits is that the accumulate portion of the multiply-accumulate (MAC) is intrinsic to the architecture; realized by accumulating the delays. The delay can be measured by counting oscillation cycles in a ring oscillator (ROSC) [6] or comparing delays with a time-to-digital converter (TDC) [5]. Digital neurons use conventional Boolean logic for arithmetic operations such as arrays of multipliers and wide accumulation adders [7]. Both architectures can be mapped to deep learning applications. It should be noted that additional operations such as non-linear transfer functions, pooling (down-sampling), and drop-out during training can be implemented readily in digital circuits. Additionally, data movement of inputs, weights, and outputs between main memory, on-chip cache, and processor needs to be facilitated. These concerns are considered open research [8] and not addressed in this thesis. The following section will discuss prior art from different neuromorphic architectures.

### 2.1.2 Alternative Neuromorphic Architectures

### 2.1.2.1 Digital Systems-on-Chip

Digital Systems-on-Chips (SoCs) have found success through many algorithmic techniques. Weight resolution modulation is employed in [7] by leveraging a reconfigurable multiplier block capable of 16-bit, 8-bit, or 4-bit operations to enable a 40x energy-precision scalability. However, there is a significant overhead as the MAC unit has

unused cells at full precision. Another feature is inputs and weights that have a value of zero assert a "guard" flag that bypasses that particular computation. Careful design of the memory-hierarchy in [9] minimizes data movement between off-chip DRAM memory by exploiting data reuse. They also incorporate knowledge of the data statistics to reduce energy by gating computations, as in [7], and using data compression to limit the size of data transferred off-chip. A 14x12 array of Processing Engines is used to compute the MACs in parallel. These cells each have over 4kb of registers and memories which reduces area efficiency and greatly increases the footprint of the SoC. Each Processing Engine is power gated to further increase energy efficiency.

### 2.1.2.2 Analog SRAM Solutions

SRAM memory-based designs that leverage charge sharing have also been proposed. In [10], SRAMs are used to store weights. Interspersed in the array are local analog moving average blocks, the control unit that implements the charge sharing across bitlines. This design makes use of low power analog techniques to drive down power, but relies on charge sharing and utilizes a time-dependent pre-charge scheme to implement the input. These two techniques limit the scalability of the design and as such they are limited to convolutional operations which have reduced input lengths due to the filter size. As a result of using charge-sharing, the SRAMs cannot be directly connected together which is why 10T bitcells are utilized instead of the conventional, denser 6T bitcells. Reference [11] also leverages charge-sharing between SRAMs in order to implement signed multiplication. They demonstrate that using in-memory computing can reduce power consumption by as much as 4.5x. However, when used as an analog device, process variation from SRAMs

necessitates on-chip learning. Models learned on one chip and applied to another can cause a 43% drop in accuracy. This requires a massive increase in overhead, reducing the efficiency of the core.

### 2.1.2.3 Analog Neuromorphic Systems

Early approaches relied on analog circuits to mimic synapse and neuron functions [12]. Analog circuits use the sub-threshold region of MOSFET devices to implement the computation. Analog neurons have low area and power consumption thanks to their subthreshold operation. However, they are slower and more sensitive to process, voltage, and temperature and compensation techniques require a large amount of overhead. Neurogrid [13] is an example of an analog neuron system. The system was intended to simulation large-scale neural interactions such as in a rat brain. The main drawback of using analog circuits to implement brain-inspired computing models is that they are sensitive to noise and process variation, so homogeneity and precision cannot be guaranteed for large scale designs. Scaling of CMOS technology also poses a challenge for analog designs as matching becomes challenging as process spreads increase.

### 2.1.2.4 Digital SRAM Crossbar

Digital SRAM implementation of neural nets has been a more popular approach lately. Compared to analog neural nets, they are less vulnerable to noise and process variation, and can benefit from technology scaling, enabling massively parallel neuromorphic ASIC systems such as IBM's TrueNorth [14]. Weights are stored in the SRAM array and wordlines represent input bits to implement the partial products of the

multiplication which is called a crossbar array. Accumulation is implemented with local registers on the bitline. The registers can be cleared randomly to implement plasticity.

### 2.1.2.5 Non-volatile Crossbar Designs

One of the key limitations of using SRAMs is the volatile storage. This requires the power supply to be connected constantly drawing static leakage power. If it is disconnected, an overhead will be incurred to reprogram the array to prepare the array for computation. Nonvolatile storage devices such as ReRAM [15] and eFlash [16] present opportunities to have persistent weight storage. The arrays work much in the same manner as SRAM crossbar arrays where the accessed bitline currents are summated to implement the MAC. ReRAM is considered an ideal candidate due to not only the low access latency and energy, but the small footprint could enable very dense arrays. ReRAM can be thought of as a programmable, analog, nonvolatile resistor. However, due to the non-uniform analog resistance states, [15] asserts that it can cause errors in the convolution. They work around this by using ReRAM as a digital device which has benefits including: better programming accuracy, binary voltages applied to WL is scalable due to lower IR-drop in large arrays, and it does not require a large on/off resistance ratio previously required in analog ReRAM [15]. The key limitation is the lack of a capable commercially available process and even [15] does not have measurement results to support their claims. eFlash arrays utilize multi-level storage element and are logic compatible to reduce cost and available in all processes [16]. The main drawback is the large cell size due to the I/O devices required to limit gate leakage on the storage node, on the order of 4x larger than an SRAM even accounting for the eFlash multilevel cell storage.

All of these different architectures have benefits and drawbacks. Time-based computing will be studied closer in the following sections. A strong case will be made for the adoption of these architectures due to their field leading energy efficiency, area density, and application performance. Two designs will be described in detail in the following sections.

## 2.2 A Scalable Time-Based Integrate-&-Fire Digitally Controlled Oscillator

### 2.2.1 Integrate-&-Fire Architecture and Concept

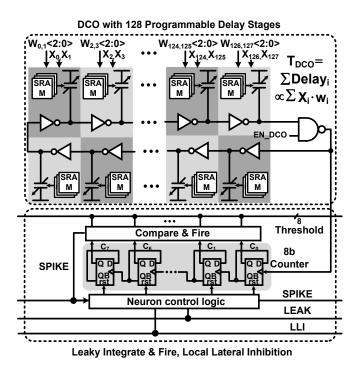

Figure 2.2 shows the time-based integrate-&-fire digital controlled oscillator (DCO) neuromorphic core. Each DCO has 128 stages with 3b programmable weight and binary input.

Figure 2.2: Conceptual circuit diagram of the proposed time-based integrate & fire (I&F) DCO neuromorphic core.

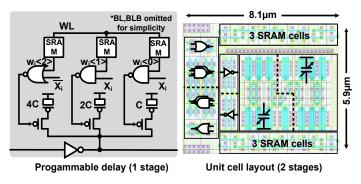

The detailed implementation of programmable unit cell delay and the leafcell layout of two delay stages are shown in Figure 2.2. Each input stage of the DCO is composed of an inverter and binary-weighted MOSFET capacitors mixing an input pixel with a 3-bit weight. The weights for each stages are stored locally in SRAM cells.

Figure 2.3: Detailed implementation of programmable delay stage and unit cell

Input pixels determine whether a stage is enabled, and weights determine how many capacitors are enabled to load the driver in that stage. Weight 1002 is defined as weight zero. Positive, or exhibitory, weights are defined as less than 1002 (i.e. 001~0112), turning on fewer load capacitors. Thus, reducing the delay of that stage. On the contrary, weights greater than 1002 (i.e. 101~1112) represent inhibitory synapses, negative weights. Delay of all stages accumulates naturally in the DCO loop and the output is fed to an 8-bit counter. The counter increments every rising-edge of the DCO cycle. When the counter value reaches a target count, a spike is generated and the counter is cleared. The spike count of the other blocks will be recorded and used as the output of each DCO unit. The counting and threshold blocks can implement the integrate-and-fire using simple hardware. The measurement precision of the time based DCO circuit can be easily programmed by changing the spiking threshold. With a higher spiking threshold for instance, a smaller frequency difference can be detected at the cost of higher energy dissipation and decreased throughput.

The DCO circuit is also very robust against jitter, since the jitter will be averaged out over many DCO cycles. This is due to the first-order noise shaping principle of using

a DCO for a time-to-digital converter [17]. When the rising edge is traveling around the DCO at each stage some random noise will be present and manifest as noise in the channel of the MOSFET which affects the current, and subsequently the delay of the stage. This error is accumulated in each stage until the input to the counter is reached. The counter will sample and the pulse will continue. However, any deviation between measurements is not lost, but carried over to the next stage. This averaging in the discrete time domain is equivalent to first-order noise shaping in the frequency domain [17].

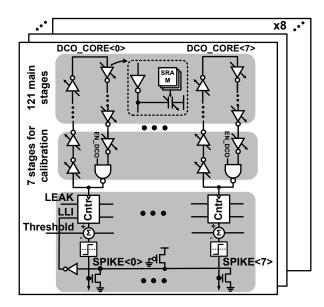

Figure 2.4 shows the overall architecture of the time-based neuromorphic core with 64 parallel DCO circuits. The array is divided into 8 groups, each consisting of 8 DCO circuits, to realize the local lateral inhibition feature discussed in section 0. Each DCO can be enabled or disabled independently allowing activation of any number of DCOs simultaneously. The neuromorphic core compares the raw spike count of each DCO to determine which neuron output is dominant.

Figure 2.4: Time-based DCO neuromorphic architecture.

Due to process variation however, different DCOs have slightly different oscillation frequencies for identical inputs. This is due to variations in the channel doping of the transistors at manufacturing which manifests as different threshold voltages. If each DCO is composed of gates that have different threshold voltages the oscillation frequencies will not be matches. It is crucial that the DCO frequencies are uniform to start with to have a meaningful measurement for the ML application. Unlike process variation, voltage and temperature variation affect all DCOs uniformly, so although the inter-trial count may vary, the dominant neuron will stay the same under voltage and temperature deviations. Seven of the 128 DCO stages are reserved for frequency trimming while the remaining 121 stages are used for the MAC function. For frequency calibration, all DCOs are configured using nominal inputs and weights, and then the frequency counts are measured for a fixed time period. By tuning the weights of the 7 frequency trimming stages, it is ensured that the DC DCO frequencies are matched.

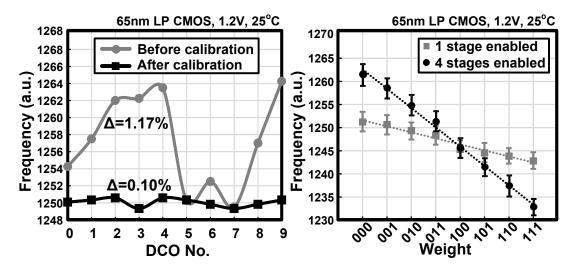

Figure 2.5: Measured DCO Frequency before and after tuning.

Measurement results in Figure 2.5 (left) confirms that after calibration the frequency variation of 10 DCOs reduces from 1.17% to 0.10%. Figure 2.5 (right) shows the mean and  $3\sigma$  error bars of the frequency count when different number of stages are activated as the weight of each stage is swept. Measured results show adequate linearity.

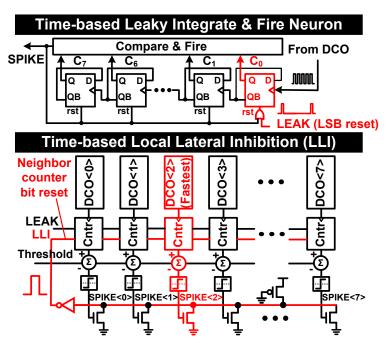

### 2.2.2 Leak and Local Lateral Inhibition Technique

Figure 2.6: Illustration of time-based leaky neuron and local lateral inhibition

Neuro-inspired leak and local lateral inhibition (LLI) features are also implemented in our design, and they can enhance the contrast between neuron outputs. Figure 2.6 explains the concept of leak and LLI. When the leak feature is enabled, the LSB of the counter is reset periodically by a low-frequency LEAK signal. This has the effect of periodically reducing the accumulated count, imitating a leaky neuron [18]. Note that the period of the LEAK signal should be several times longer than that of the DCO in order to allow the count to increment. The main benefit of the leak operation is that it can increase the relative difference between DCO counts as shown in Figure 2.7(left). The frequency difference between the dominant DCO and the others becomes larger and this can be thought of as increasing the contrast.

\*None: No leak and no LLI, basic DCO operation.

Figure 2.7: Effect of leak and LLI features.

Lateral inhibition is a phenomenon in which the dominant neuron strives to suppress the activation of its neighbors. In this design, eight DCO cores are grouped together to realize LLI. The inhibition amount (count decrease) is determined by which bits of the neighbor counter are reset. Once a DCO in the group spikes, an LLI pulse generated, which resets predetermined bits of the neighboring counters. The fastest DCO in the group resets the other DCOs more often than it is reset by the other DCOs, enhancing the contrast between different DCO outputs, which is illustrated in Figure 2.7 (right).

### 2.2.3 Application and Measurement Results

A test chip was fabricated in a standard 1.2V, 65nm LP CMOS process to demonstrate the time-based neuromorphic core. Due to die area constraints, a single core was implemented. However, a multi-core architecture can be realized to handle deep neural network algorithms by tiling additional DCO cores and operating them in parallel.

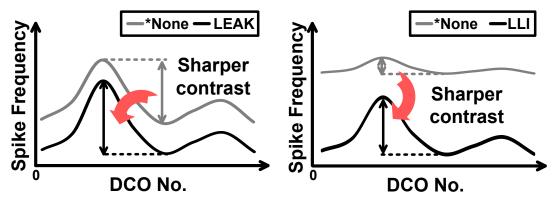

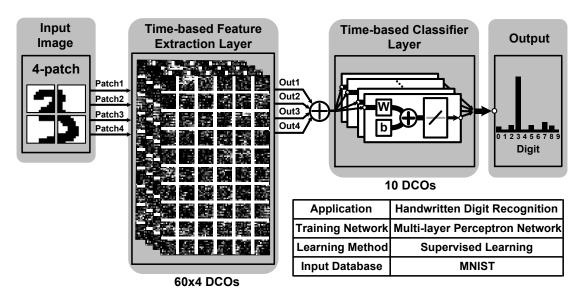

Figure 2.8: Multi-layer digit recognition test architecture and summary for timebased neuromorphic chip demonstration.

Figure 2.8 shows a 2-layer test architecture for handwritten digit recognition used to showcase the versatility of the proposed core. Handwritten text images were obtained from the MNIST database [19]. The original image size is 28x28 pixels. First, the image is reduced to 22x22 pixels by removing three pixels on each side as they contain little information. Each image is then divided into four regions so that they can be assigned to different cores for increased throughput. The first layer of the neural net can extract 60 distinct features from each patch. The outputs of the four patches from the first layer are summed, encoded, and used as the inputs for the second classifier layer. Weights of both layers are trained off-chip using supervised learning and downloaded to the chip.

tonor no roak and no EE, baolo Boo operation.

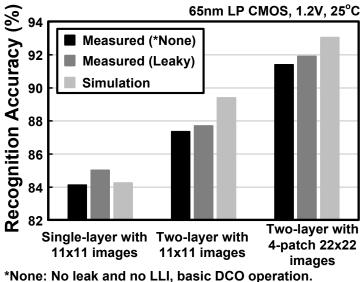

Figure 2.9: Measured application results.

Figure 2.9 compares the accuracy between different configurations. The 2-layer architecture with 4-patch inputs (=22x22 pixels) achieves a recognition accuracy of 91.4%. With the leak feature enabled, the accuracy increases modestly to 91.9%. The measured accuracy is comparable to software simulation results. As seen from the measurement results in Figure 2.9, the recognition accuracy of a single-layer architecture increases from 84.1% to 85.0% after enabling the leak feature, while the accuracy doesn't improve as much in the two-layer architecture. This is because in the two-layer architecture, there are more weights available to improve the contrast between the neuron outputs at training. This makes the leak feature less effective.

\*None: No leak and no LLI, basic DCO operation.

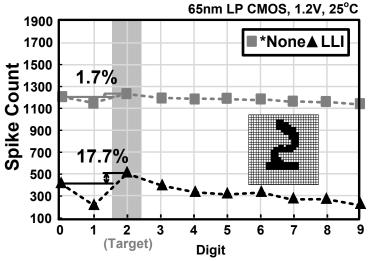

Figure 2.10: Example of measured output from one digit.

Figure 2.10 shows the output spike count with and without the LLI feature for an image containing handwritten digit "2". The spike count difference between digit "2" and runner-up digit "0" is improved from 1.7% to 17.7% using LLI. This greatly improves the confidence in the prediction.

**Table 2.1: Performance Comparison**

|                     | This work                                      | ISSCC'16 [20]                           | VLSI'16 [21]           | ISSCC'15 [22]          | ISSCC'14 [23]                  | CICC'11 [14]                    |

|---------------------|------------------------------------------------|-----------------------------------------|------------------------|------------------------|--------------------------------|---------------------------------|

| Application         | Hand writing recognition                       | Object detection + intention prediction | Object recognition     | Big data analysis      | Pattern recognition            | Hand writing recognition        |

| Function            | Multi-layer perceptron<br>network              | Deep neural<br>network                  | Deep neural<br>network | Deep neural<br>network | Unsupervised online clustering | Restricted<br>Boltzmann Machine |

| Circuit Type        | Time-based                                     | Analog + Digital                        | Digital                | Digital                | Analog + Floating gate         | Digital                         |

| Technology          | 65nm                                           | 65nm                                    | 40nm                   | 65nm                   | 0.13µm                         | 45nm                            |

| Area                | 0.24mm <sup>2</sup> (64 DCOs)                  | 16.0mm <sup>2</sup>                     | 1.4mm <sup>2</sup>     | 10.0mm <sup>2</sup>    | 0.36mm <sup>2</sup>            | 4.2mm <sup>2</sup>              |

| Voltage             | 1.2V                                           | 1.2V                                    | 0.9V                   | 1.2V                   | 3V                             | 0.85V                           |

| Frequency           | 99MHz (nominal DCO freq.)                      | 250MHz                                  | 240MHz                 | 200MHz                 | 8.3kHz                         | -                               |

| Power               | 320.4 μW/DCO                                   | 330mW                                   | 140.9mW                | 185mW                  | 11.4µW                         | 45pJ/spike                      |

| Performance         | 99M ÷ N spikes/s/DCO<br>(*N=spiking threshold) | 502.0GOPS                               | 898.2GOPS              | 411.3GOPS              | 0.012GOPS                      | -                               |

| Power<br>Efficiency | 309G ÷ N spikes/s/W (*N=spiking threshold)     | 862GOPS/W                               | 6.37TOPS/W             | 1.93TOPS/W             | 1.04TOPS/W                     | -                               |

\*N=16 in our measurements

Table 2.1 shows the performance comparison with recent neuromorphic chip designs [20], [21], [22], [23], [14]. It is worth noting that an apples-to-apples comparison between our time-based scheme and traditional ASIC chips can be tricky. Here, metrics (e.g. spikes/s/DCO) specific and relevant to our design are presented. The proposed DCO array can generate  $3.09 \times 10^{11}/16 = 1.93 \times 10^{10}$  spikes per second per watt, for a spiking threshold value of 16.

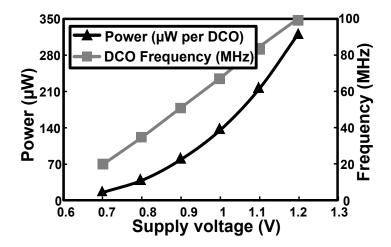

Figure 2.11: Measured power consumption and DCO frequency for the I&F core

Figure 2.12: Die photo and performance summary

Figure 2.11 shows the measured power consumption and DCO frequency under different supply voltages. The test chip has a wide operating voltage range of 1.2V to 0.7V. The DCO circuit oscillates at 99MHz consuming 320.4μW under a nominal 1.2V supply. At 0.7V, the DCO oscillates at 20MHz consuming 17.5μW. Figure 2.12 shows the chip micrograph and performance summary.

#### 2.2.4 Conclusions

In this section the idea of implementing neuromorphic function purely in time domain with programmable delay stages based on a leaky integrate-&-fire mechanism was presented. Brain-inspired leak and local lateral inhibition (LLI) are introduced to increase the contrast and confidence in the predictions. The time-based neuromorphic core is tested with digit recognition application and achieves 91.4% recognition accuracy. The energy-efficiency and versatility of the presented time-based DCO neuromorphic core makes it a promising building block for future large scale deep neural network applications.

# 2.3 An Energy Efficient Time-Based One-Shot Neuromorphic Chip

# 2.3.1 One-Shot Neuromorphic Architecture

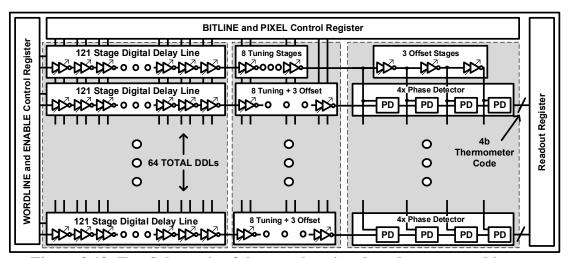

Figure 2.13: Top Schematic of the one-shot time-based neuromorphic core

Conventionally, Boolean computations are used to realize arithmetic operations in hardware. However, time domain circuits can also be used at an advantage of lower area and power per processing unit, and reduced design complexity. The kernel of all ML algorithms can be distilled into a dot product shown in Equation 2.1. The high level architecture is shown in Figure 2.13. An input pulse is presented on the left side of the core and the delay of each stage is modulated based on the application inputs. It is described as one-shot because each pulse gets evaluated once.

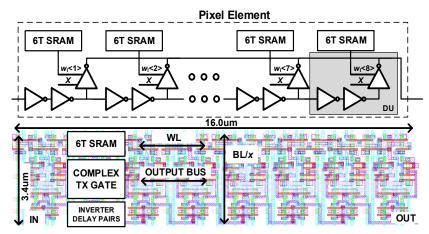

Figure 2.14: (Top) Schematic of pixel stage. (Bottom) Layout of pixel element.

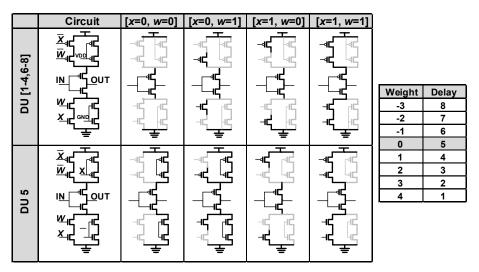

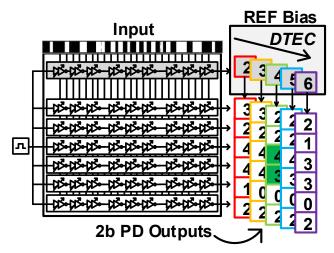

Figure 2.15: (Left) Complex tristate wiring. (Right) Trained weight to DU stages

Each stage has 8 delay units (DU) with output taps which the pulse travels through as seen in Figure 2.14. The number of DU enabled depends on the one-hot encoded weight, stored locally in SRAM cells, and the input pixel, which is applied across the array on the bitlines. Each DU has two inverters to retain consistent polarity between stages. This is critical in the event that the rising and falling propagation matched, as well as ensuring correct polarity at the TDC. The output tap is realized as a complex tristate gate and the functionality is described in Figure 2.15. The first column shows the circuit schematic and

corresponding connections between the different DU. The right four columns show the activated paths, shown with black lines, depending on the values of the input, x, and weight, w. DUs is the nominal stage delay, and is activated through the right branch of the circuit when the input bit is off, representing "zero delay." Figure 2.15 (right) shows the mapping between the algorithm-trained weights and the delays realized in the chip at each stage. When the input, x, is present the left branch is enabled in the DU corresponding the weight bit of the stage. Larger positive weights map to shorter delays relative to the reference DDL, and conversely negative weights correspond to longer delays. The accumulation in the MAC is achieved naturally as the pulse passes sequentially through the DDL, stage by stage. The layout of each DU in the stage is pitch matched to a 6T SRAM so the layout is regular, compact, and scalable. The bias vector is applied in the same way for the last eight units. Additionally, it can be used to tune process variation, so that during evaluation those pixels are always activated.

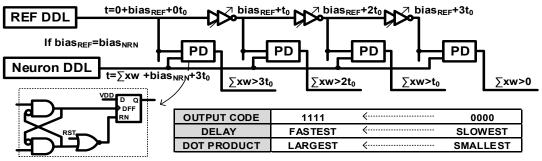

Figure 2.16: Timing details of the 2 bit TDC.

Figure 2.16 shows the relationship between the time domain computation in the chip and the expected arithmetic output. The phase detector output maps roughly to the rectified linear unit (ReLU) transfer function. When the reference pulse beats the neuron rising edge all four thermometer bits are zero, regardless of the magnitude. The transfer

function between the four bits is linear and then clips, or saturates, once the neuron pulse is faster than all the offsets.

# 2.3.2 TDC Performance Analysis

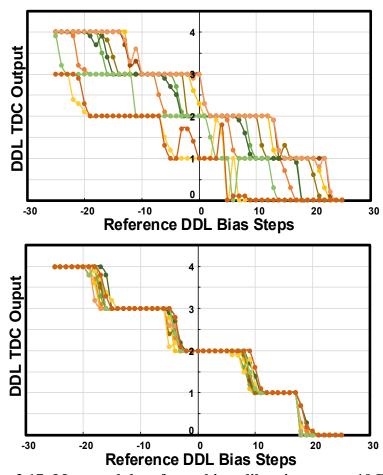

The delay of time-based circuits can be tuned to cancel out inter-DDL process variation. Measured one-time calibration results are shown in Figure 2.17. Calibration was performed by evaluating each DDL and measuring the DDL phase detector output. After each evaluation, the bias bits (8 Tuning in top DDL shown in Figure 2.13) of the reference was increased and the process repeated.

Figure 2.17: Measured data from chip calibration across 10 DDLs.

At each bias point, 10 additional evaluations were run due to quantify trial-to-trial temporal noise, seen as the slope between TDC levels. No other measurements are averaged in the following sections. The reference bias point at which the PD of each DDL trips is applied to the tuning bits of the respective bias to align all DDLs, thus, compensating process variation. The average of the 10 trials is plotted in the Figure 2.17. The inter-DDL spread before calibration is approximately 21 reference bias steps, or tuning steps. After calibration, the spread was reduced to less than three tuning steps. The curves are mostly monotonically decreasing which is expected even though there is meta-stability when the phase of the output and reference DDLs are nearly matched. This supports the effectiveness of the proposed time-based MAC methodology.

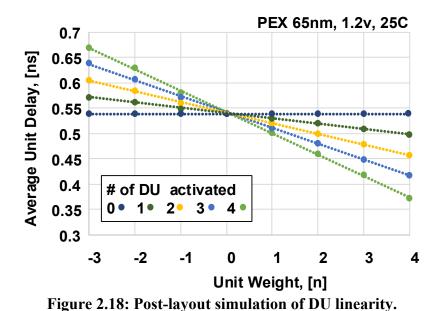

Figure 2.18 shows the simulated average unit delay as a function of the weight in each unit. In this simulation, the extracted layout of a four stage DDL was used to measure the delay of a single weight change. Each stage has the weight programmed from [-3, 4],

corresponding to the x-axis, and the number of active stages is swept from none to all four, corresponding to the different series. This confirms there are no systematic biases between the different weights.

Using both measured and simulated tuning curves it is possible to quantify the TDC performance [24]. It should be noted that while the TDC performance is important, the trade-offs between area, power, and application performance are paramount. For each bit of increased TDC resolution the area and power doubles. This incentivizes the designer to use a minimalistic design to keep overhead low while still managing to meet the requirements of the application, discussed further in section IV. The TDC gain is the slope of the output code to input code. The ideal slope is described by Equation 2.2,

$$k_{TDC} = \frac{1}{T_{LSB}}$$

2.2

where  $T_{LSB}$  is the minimum time interval that can be measured, which in this case would be 12 tuning bits. The gain error describes the difference in the last output code to the expected result based on the gain, quantified by Equation 2.3 [24].

$$E_{gain} = \frac{1}{T_{LSB}} (T_{1111} - T_{0001}) - (2^{N} - 2)$$

2.3

In this work,  $T_{LSB}=12$  tuning bits based on the calibrated tuning curve, thus  $E_{gain}=-\frac{1}{4}$ . Returning to the TDC gain, one can now use the gain error to accurately estimate the actual gain error.

$$k_{TDC} = \frac{1}{T_{LSB}} \left( 1 - \frac{E_{gain}}{N_{levels} - 2} \right) = \frac{3}{32}$$

2.4

This is 12.5% steeper than the ideal gain due to the reduced phase window at output code 0001. This could be due in part to the reduced load seen after the third reference buffer and rectified in future work by adding a dummy load to better match the delays of each branch of the TDC.

The previous paragraph studied the performance metrics that affect the linear performance. Next, the non-linear performance due to process variation and noise will be quantified. The total delay can be described as:

$$t_n = nT + \sum_{i=1}^n \varepsilon_i$$

2.5

where  $\varepsilon_i$  is the delay error caused by process variation at stage *i*. In Table 2.2,  $\mu$  is equivalent to the nT term, where n is chain length and T is the DU delay. If all the delay units are independent but derived from the same distribution, the standard deviation of the total time is  $\sigma(t_n) = \sigma(\varepsilon)\sqrt{n}$ .

Table 2.2: DDL Delay for increasing chain lengths

|                   | PEX 65nm, 1.2V, 250 |        |        |  |  |  |  |

|-------------------|---------------------|--------|--------|--|--|--|--|

| t <sub>fall</sub> |                     |        |        |  |  |  |  |

| Chain<br>Length   | μ                   | σ      | σ/μ    |  |  |  |  |

| 4                 | 2.25n               | 34.6p  | 0.0154 |  |  |  |  |

| 16                | 9.24n               | 68.3p  | 0.0074 |  |  |  |  |

| 128               | 72.92n              | 194.6p | 0.0027 |  |  |  |  |

| t <sub>rise</sub> |                     |        |        |  |  |  |  |

| Chain<br>Length   | μ                   | σ      | σ/μ    |  |  |  |  |

| 4                 | 2.25n               | 37.4p  | 0.0167 |  |  |  |  |

| 16                | 9.24n               | 67.1p  | 0.0073 |  |  |  |  |

| 128               | 73.00n              | 200.5p | 0.0027 |  |  |  |  |

<sup>\*</sup>Estimated via square root law [11]

This is supported by Table 2.2, where chains of length 4 and 16 were simulated after parasitic extraction for 100 Monte Carlo samples. The distribution of the delays were normally distributed and the standard deviation follows the square root law. Chain lengths of 128 were estimated by the square root law. This has two consequences; the first being a shorter delay chain will have less variation. This is better, however it has lower efficacy because there are fewer elements that can be multiplied at once reducing the throughput and increasing power. The second consequence is that the rate of increase decreases as more stages are added to the delay chain. This means that an increase of 8x stages only results in an increase of 2.8x in the standard deviation. From Figure 2.18 it is estimated that the tuning step delay is 10.5ps, which makes the standard deviation equal to roughly 18.5 tuning steps, or 1.53 output codes. This could be reduced by increasing the transistor size, W, to reduce the Johnson-Nyquist noise, where in saturation the power spectral density of the drain current is shown in Equation 2.6[25].

$$S_i = 4kT \frac{2}{3} \frac{W}{L} \mu C_{ox} (V_{GS} - V_T)$$

2.6

Reducing noise comes at a cost of higher power consumption. As temperature and voltage increases it can be seen the current will increase. These shifts would be seen at the global level since all DDLs share the same voltage supply. Additionally, temperature gradient across the small, dense array would be unlikely and if there was a global temperature shift, it would affect all DDLs together. Another method could utilize a closed-loop ring oscillator which integrates the noise over multiple cycles which reduces the total error at a cost of lower throughput and higher power per prediction [6]. With these trade-offs

identified the proposed circuit strikes a balance between performance and a light-weight solution.

## 2.3.3 Dynamic Threshold Error Correction (DTEC)

Figure 2.19: DTEC operating concept illustrated where reference DDL bias is swept to boost TDC resolution.

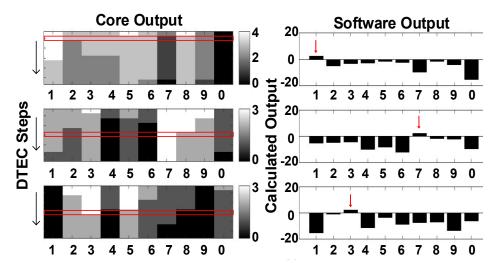

In the prior section the 2 bit TDC was described. It was selected due to the optimal tradeoff between small area and low power, and strong architecture performance. In networks with "winner-take-all" topologies, such as the last stage of classification networks, ambiguous predictions can occur. Unclear outputs in this work can stem from limited resolution between phase detector trip-points or activity outside of the range of the phase detector. To mitigate this issue, Dynamic Threshold Error Correction (DTEC) technique is proposed, which increases the effectiveness of the 2bit TDC. As shown in Figure 2.19, when two or more DDLs have the same output, DTEC works by increasing the threshold bias delay which moves the trip point of the phase detectors. DTEC is dynamic due to the fact that the bias sweep would be terminated after the third evaluation, when the dominant DDL was identified from the phase detectors. Additionally, DTEC can

be stopped after a fixed number of steps if no dominant DDL emerges to conserve power. In Figure 2.21the top row of colormaps shows ambiguous predictions from the core, while successive rows show the output as DTEC is applied. Red rectangles highlight where DTEC has successfully identified the target.

Figure 2.20: Measured effectiveness of DTEC, first rows show ambiguous prediction and as bias is swept winner is isolated.

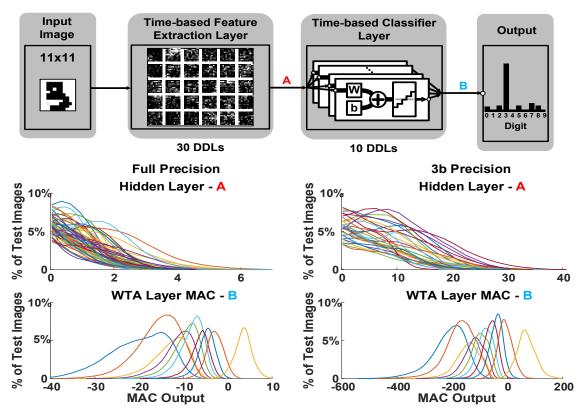

Figure 2.21 plots the distributions of outputs from the intermediate layers in a two-layer dense neural network with 30 hidden units and 10 output units for all 10,000 test images in the MNIST benchmark [19]. The left column corresponds to the output with full precision weights and the right column corresponds to our rounded three-bit weights. The first row shows the network model used for the analysis. The second row displays the distribution of the MAC output of all 30 hidden units after the ReLU transfer function. The third row shows the winner take all (WTA) output of network, but each curve plots the sorted output instead of each unit (i.e. the correct outputs for the ten cases are grouped to

one unit). The x-axis scales are not normalized to a unit weight. In the 3b precision network, the full precision weights have been scaled up to match the DU range (i.e. [-3,4]).

Figure 2.21: Distribution of activation outputs in a 2 layer neural network.

These curves support the assumption that a 2-bit TDC can cover the entire output range because according to Figure 2.17 the width of the PD is 40 units on the x-axis. The hidden layer output would be contained inside that range. In the hidden layer, the results are approximately zero-centered prior to the ReLU activation, but have a large range. Units in neural networks must have zero-centered activations otherwise the predictions would be biased resulting in reduced learning capacity. If the TDC had a unit step of 1 tuning bit (equal to 1 step of the x-axis) this would require at least a 6-bit TDC for each DDL. The area overhead would render this solution infeasible. Additionally, due to the effectiveness

of the training, the correct prediction output histogram has very little overlap with the remaining predictions. This outcome can be leveraged because in the majority of the cases a high precision TDC will not provide additional information when the only relevant outcome is which unit has the highest activation. Another observation is that full precision and fixed point traces match closely. There is a modest amount of spread between the fixed and full precision hidden layer outputs. Nearly all hardware implementations utilize fixed point weights and this is an acceptable transform as the curves match.

Analysis of results from the 3b single layer application (section 2.3.4) show that by applying just two DTEC steps 81.64% of the correctible errors are recovered. This comes at a cost of just 41% additional evaluations per image. After the one-shot evaluation, 73% of all images have a dominant output. The remaining 2,668 images begin DTEC. After the first step 46% are resolved and 37% after the second step leaving less than 1,000 images ambiguous. Thus, 4,108 DTEC evaluations improves the total accuracy from 69.16% to 82.14%. If three DTEC steps are applied 88.8% of errors can be recovered at an overhead of 51%, demonstrating the dynamic scalability of the technique. Hardware results show that DTEC is an economical and scalable approach to significantly improve application performance.

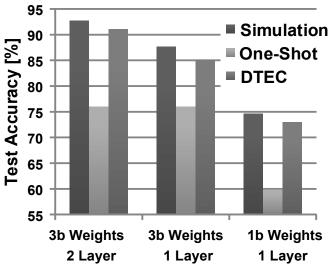

## 2.3.4 Application and Measurement Results

The core was evaluated on the MNIST benchmark [19]. Figure 2.22 shows the comparison of classification accuracy on an 11x11 image for single and two layer networks between expected simulated software results, one-shot evaluation, and DTEC. To reduce the 28x28 grayscale images to 11x11 binary images, 3 pixels are sliced from all four sides

of the image. Then, a fixed resizing command is applied, and finally the pixels are binary thresholded.

Figure 2.22: Measurement results on MNIST application

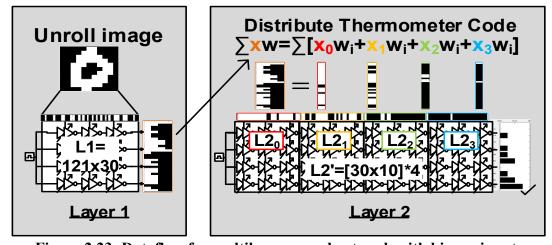

Figure 2.23: Dataflow for multilayer neural network with binary inputs.

Figure 2.23 shows how the core can be used in a multi-layer deep neural net application. Each bit of the thermometer code is expanded as the input in the next layer. The input is divided into four segments, and the weight matrix is copied four times (L2<sub>0</sub>-L2<sub>3</sub>), which gives each bit equal weighting. In the example shown in Fig. 12, 30 neurons in layer 1 yield a 120 bit input to layer 2. By applying DTEC, the ambiguous results are

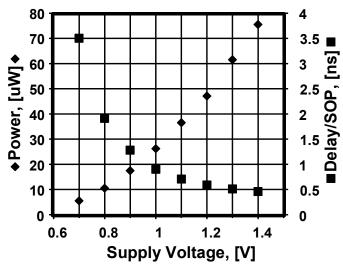

almost completely recovered and the slight loss in accuracy is due to output differences smaller than a single tuning bit. Figure 2.24 shows the tradeoff between power consumption and nominal stage delay for various supply voltages. Power is kept exceptionally low because rarely are more than two stages switching at a time in a DDL. A wide operating voltage range is enabled, due to the all-digital time-based design choices.

Figure 2.24: Power dissipation of a single DDL and delay/stage across VDD.

If the design incorporated pipelining, it could achieve even greater throughput. That is, multiple pulses could be pushed into the DDL and the input could shift as well. This is ideally suited for convolutional nets where a weight filter slides across an image. In this case, the image could slide across the weights while input pulses are applied to the DDL. Die photo and design specs are highlighted in Figure 2.25.

Figure 2.25: Chip micrograph and chip summary (metrics reported at nominal supply).

**Table 2.3: Performance Comparison Table**

|                                | This        | Work                    | A-SSCC'16 [26] | CICC'17 [6] | ISSCC'17 [7] | ISSCC'17 [27] | ISSCC'16[28] | ISSCC'16[9] | Science'14[4] |

|--------------------------------|-------------|-------------------------|----------------|-------------|--------------|---------------|--------------|-------------|---------------|

| Chip Architecture              | Time-Based  |                         | Time-Based     | Time-Based  | Digital      | Digital       | Digital      | Sw. Cap     | Digital       |

| Algorithm Target               | FCDNN & CNN |                         | FCDNN & CNN    | FCDNN & CNN | FCDNN & CNN  | FCDNN & FFT   | CNN          | CNN & SGD   | FCDNN & CNN   |

| Technology [nm]                | 65          |                         | 65             | 65          | 28 FDSOI     | 40            | 65           | 40          | 28            |

| Chip Area [mm²]                | 0.644       |                         | 3.61           | 0.24        | 1.87         | 7.1           | 12.25        | 0.012       | 430           |

| Precision* [b]                 | [B,T,2,3]   |                         | В              | 3           | [4-16]       | [6-32]        | 16           | 3           | [B,T]         |

| On-Chip SRAM [kB]              | 8.06        |                         | 20             | 3           | 144          | 270           | 181.5        | [-]         | 256MB         |

| VDD [V]                        | 1.2 (Nom.)  | 0.7 (E <sub>MAx</sub> ) | 1              | 1.2         | 0.6          | 0.65          | 0.82         | 1           | 0.85          |

| Frequency [MHz]                | 1700        | 285                     | 23041          | 792         | 200          | 19.3          | 250          | 1000        | 0.001         |

| Energy Efficiency** [TSop/s/W] | 36.2        | 52.4                    | 48.2           | 2.47        | 5.0          | 0.19          | .18          | 3.86        | 0.04          |

| Hardware Efficiency [GE/PE][1] | 38.4        |                         | 76.5           | 33.2        | 7456         | 18269         | 50637        | 288         | 6.5           |

\*B=Binary, T=Ternary \*\*Synaptic Op=MAC