## CIRCUIT TECHNIQUES FOR COGNITIVE RADIO RECEIVER FRONT-ENDS

A DISSERTATION

# SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL

### OF THE UNIVERSITY OF MINNESOTA

$\mathbf{B}\mathbf{Y}$

**BODHISATWA SADHU**

### IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

### FOR THE DEGREE OF

Doctor of Philosophy

June, 2012

### © BODHISATWA SADHU 2012

ALL RIGHTS RESERVED

## Acknowledgements

This thesis is hardly a lone effort. I would like to express my gratitude to my advisor, Prof. Ramesh Harjani, whose guidance, motivation, friendship, and support has made this thesis feasible, and shaped my life and career over the last five years. I am indebted to him for his unfailing support and his unbiased advice at all times during my PhD. Looking back, I now feel astonished at the immense patience with which he guided me when I first joined the lab with my embarrassing lack of knowledge about circuit design. Over the years, our discussions, ranging from circuit theory to Sartre and Hesse, have become a dear part of my life. In years to come, I will remember and cherish all our animated conversations, the joyous parties at his home, and Savita ma'am's wonderful company.

Along with Prof. Harjani, the lab exposed me to an infectious zeal for circuits research to which I owe a large part of my enthusiasm. During my PhD, I had the privilege of working with some of the most wonderful people I now know. I was introduced into research in circuit design by Narasimha Lanka and Satwik Patnaik. I learned one of the most important lessons of my PhD from Satwik, that of unswerving perseverance. For that, as for a lot of other things, I will be ever grateful to him. I am indebted to Sudhir Kudva for his unfailing friendship and support every single day of my PhD. With him around, hard times never seemed that hard, and work became enjoyable. I was privileged to work with Martin Sturm on the CRAFT project. I am grateful to him for sharing the intense work-load that the project often demanded. He has taught me a lot during the course of the project, and my PhD. I could not have learned about chip testing from a better engineer. I am also grateful to Sachin Kalia, Ashutosh Mehra and Mohammad Elbadry for their friendship. Our discussions have been a great learning experience for me. Also, with them around, there was never a dull moment in the lab. I am thankful to Jaehyup Kim for sharing his expertise in analog layout, and to Taehyoun Oh for his help and friendship during the last few years. I will also fondly remember the invigorating (and sometimes unending) discussions I have shared with Rakesh Palani during the final year of my PhD.

I am thankful to Prof. Anand Gopinath for his unconditional help and precious advice throughout my PhD. I have thoroughly enjoyed his stories filled with wit, inspiration, and humor. I am grateful to Prof. Chris Kim and Brian Sadler for their advice and support. Also, I would like to express my sincere thanks to Prof. Anand Gopinath, Prof. Chris Kim, Prof. Richard Moeckel and Brian Sadler for serving on my final defense committee. My experience during internships at IBM Watson Laboratories was of great learning and stimulating research. I am deeply thankful to Alexander Rylyakov and J-O. Plouchart for their patient and encouraging mentorship. I am also grateful to José Tierno, Mark Ferriss, Scott Reynolds, Daniel Friedman, Arun Natarajan, Alberto Valdes-Garcia, Mihai Sanduleanu, Ankur Agrawal and Soner Yaldiz for making my internships some of the most enjoyable and productive periods of my graduate studies.

Carlos Soria and Chimai Nguyen have been incredible in their support of all the computer systems that we rely on for our livelihood. I am grateful to them for stretching their support beyond the stipulated work hours and work days, and treating our deadlines as theirs. Jamie Halleckson, Linda Jagerson, Parker Smith, Kyle Dukart, Dan Dobrick, Gina McCabe and Becky Colberg have worked hard to shade us from all the bureaucracy, and often do thankless jobs to make all this research possible. Thank you.

I am grateful to MOSIS, TAPO and IBM for providing fabrication of prototype chips. I would also like to express my gratitude toward the funding agencies: Center for Circuits and Systems Solutions (C2S2), Semiconductor Research Corporation (SRC), the U.S. Army Research Laboratories (ARL) and Defense Advanced Research Projects Agency (DARPA) who made this research possible.

Life as a graduate student would not have been as fulfilling without the company of several friends. I am grateful to Sonia Das and Ajay Yekkirala for their friendship, and their unfailing concern for my well-being (especially during those tape-outs). My room-mates, Parthiv Daggolu and Reetam Chakrabarti have had to endure me during my deadlines as well as their aftermath, and borne both equally well. I will cherish the numerous refreshing discussions I have had with Gaurab Samanta and Shameek Bose, over dinner, coffee, or long drives to Chicago. I am thankful to Vidhi Zalani for her cheerful companionship, and her exemplary patience. I feel blessed to have the love and generosity of such wonderful people as Vivian Fu and Douglas Ewing touch my life. My undergraduate years at BITS, Pilani have shaped my life and career in numerous ways. I am indebted to Anurup Mitra and Prof. L. K. Maheshwari for introducing me to analog electronics. I am deeply grateful to Raghavendra Rao, Shibanka Das Biswas, Ramya Prayaga, Raghav Mehta, Ravish Patel and Naveen Karnam for their love, friendship, and support. I have been fortunate to have mentors such as Tania Roy and Madhurjya Banerjee who have always had the time for me when I needed it most. I am indebted to Samik Bhar for his love, and unfailing friendship since our childhood days.

Finally, but most importantly, I am grateful to my parents, grandparents, and my sister for everything they have given me. Fairtytales do not boast of happier families. I am grateful to my father for unraveling to me the world of science, teaching, and research, and making my life much richer than it would have otherwise been. My mother has been a pillar of support, patience, and understanding through all my endeavors. I could not have done all this without her. Soumi does a brilliant job of tolerating her elder brother, of patiently listening to his rants, and yet adoring him (and even proof-reading his entire thesis overnight). I owe all of this to them.

Dedicated to my parents, and my little sister

#### Abstract

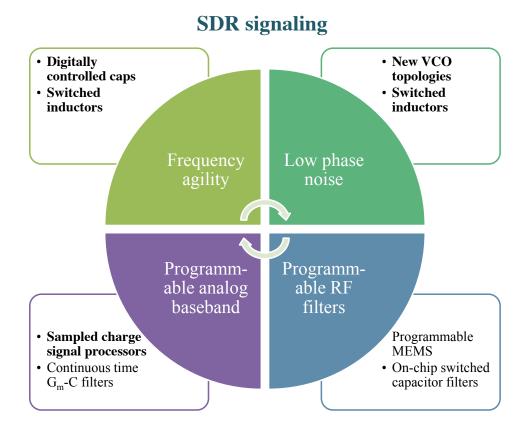

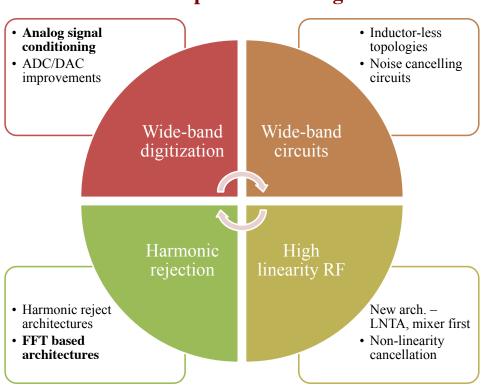

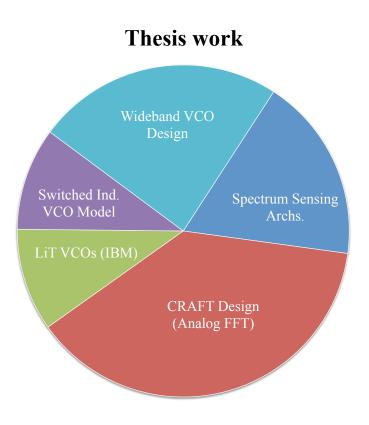

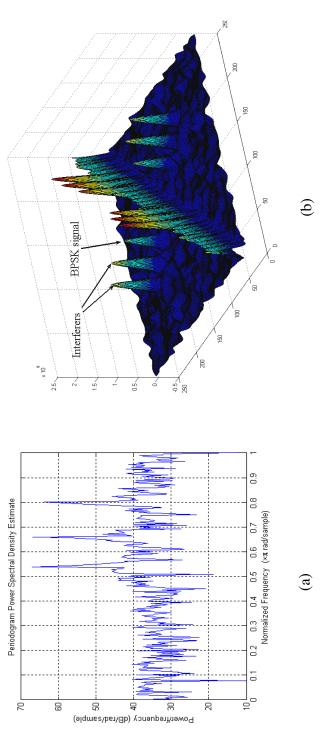

This thesis discusses the design of the receiver front-end for software defined radio (SDR) based cognitive radio applications. Two aspects of SDRs for cognitive radios are distinguished: signaling and spectrum sensing. Narrowband wide tuning signaling architectures and instantaneous wideband spectrum sensing architectures are identified as candidates for feasible SDR implementations. Several architectures and circuit implementations are reviewed. Wide tuning range, low phase noise frequency synthesizers for signaling, and RF samplers and signal processors for spectrum sensing are identified as critical circuit design blocks.

A number of voltage controlled oscillator (VCO) techniques for wide-tuning range, and low phase noise frequency synthesis techniques are developed. Wide-tuning range techniques based on switched inductors are proposed as a way to design inductorcapacitor (LC) VCOs with wide-tuning ranges that maintain a good phase noise and power dissipation performance over the entire tuning range. Switched inductor VCOs are analyzed in detail, and a design framework is developed. Optimized capacitor array design techniques for wide-tuning ranges are discussed. Based on these techniques, measurements from two prototype designs are presented, that achieve tuning ranges of 87% and 157% in measurement. They also maintain good phase noise, power consumption, and figure of merit (FOM) over the entire tuning range. In addition, a new family of VCOs that achieve superior phase noise is introduced. This set of novel topologies are based on linearized transconductance using capacitive feedback techniques. They achieve higher amplitudes of oscillation, and consequently, a superior phase noise performance. A wide tuning range is also maintained. The VCOs are analyzed, and detailed measurement results from a design prototype are presented.

For spectrum sensing, the design of CRAFT (Charge Re-use Analog Fourier Transform): an RF front-end channelizer for software defined radios (SDR) based on a 16 point analog domain FFT is described. The design relies on charge re-use to achieve 47dB average output SNDR on a 5GS/s input, and consumes only 12.2pJ/conv. These numbers represent orders of magnitude improvement on the work reported previously in literature. The thesis also briefly discusses the modeling of circuit non-idealities in CRAFT, and outlines circuit techniques for mitigating these. These design principles enable this implementation to achieve a large dynamic range even at high speeds. Additionally, these techniques can be easily extended to improve the performance of other passive switched capacitor designs.

# Contents

| A             | cknov    | vledgements i           |  |  |  |

|---------------|----------|-------------------------|--|--|--|

| A۱            | Abstract |                         |  |  |  |

| $\mathbf{Li}$ | st of    | Tables xiv              |  |  |  |

| Li            | st of    | Figures xv              |  |  |  |

| 1             | Intr     | oduction 1              |  |  |  |

|               | 1.1      | Wireless Growth         |  |  |  |

|               | 1.2      | Spectral Congestion     |  |  |  |

|               | 1.3      | Dynamic Spectrum Access |  |  |  |

|               | 1.4      | Cognitive Radio         |  |  |  |

|               |          | 1.4.1 Spectrum Sensing  |  |  |  |

|               |          | 1.4.2 Signaling         |  |  |  |

|               | 1.5      | Organization            |  |  |  |

| 2 | Cog | gnitive | Radio Architectures                       | 13 |

|---|-----|---------|-------------------------------------------|----|

|   | 2.1 | Introd  | luction                                   | 13 |

|   | 2.2 | Signal  | ing                                       | 15 |

|   |     | 2.2.1   | Receiver                                  | 16 |

|   |     | 2.2.2   | Transmitter                               | 26 |

|   | 2.3 | Spectr  | rum Sensing                               | 27 |

|   | 2.4 | Conclu  | usions                                    | 35 |

| 3 | Wie | leband  | l Voltage Controlled Oscillator           | 37 |

|   | 3.1 | Introd  | luction                                   | 37 |

|   | 3.2 | Freque  | ency Tuning Options in LC Tank VCOs       | 38 |

|   |     | 3.2.1   | Tuning range                              | 38 |

|   |     | 3.2.2   | Phase Noise                               | 40 |

|   |     | 3.2.3   | Power                                     | 44 |

|   | 3.3 | Reson   | ator Synthesis                            | 47 |

|   | 3.4 | Protot  | type I                                    | 49 |

|   |     | 3.4.1   | Simple Model for Design Space Exploration | 50 |

|   |     | 3.4.2   | Proposed Switched Inductor Implementation | 56 |

|   |     | 3.4.3   | Detailed Prototype Design and Simulation  | 59 |

|   |     | 3.4.4   | Measurement Results                       | 62 |

|   | 3.5 | Protot  | type II                                   | 66 |

|   |     | 3.5.1   | Switched Inductor Implementation          | 68 |

|   |     | 3.5.2  | Capacitor Array Implementation                 | 72  |

|---|-----|--------|------------------------------------------------|-----|

|   |     | 3.5.3  | Measurement Results                            | 86  |

|   | 3.6 | Concl  | usions                                         | 89  |

| 4 | Low | 7 Phas | e Noise VCO Topologies                         | 92  |

|   | 4.1 | Introd | luction                                        | 92  |

|   | 4.2 | A Fan  | nily of Linearized Transconductance (LiT) VCOs | 94  |

|   |     | 4.2.1  | Cross-coupled Topology                         | 94  |

|   |     | 4.2.2  | Drain Divider                                  | 100 |

|   |     | 4.2.3  | Gate-Divider or Base-Divider                   | 101 |

|   |     | 4.2.4  | Gate-Divider Type B                            | 105 |

|   |     | 4.2.5  | Gate & Drain Divider Type A                    | 107 |

|   |     | 4.2.6  | Gate & Drain Divider Type B                    | 112 |

|   | 4.3 | High s | swing capacitor switch design                  | 116 |

|   | 4.4 | Biasin | ıg                                             | 117 |

|   | 4.5 | Drain  | -Divider LiTVCO                                | 124 |

|   |     | 4.5.1  | Transconductance Linearization                 | 124 |

|   |     | 4.5.2  | Implementation                                 | 129 |

|   |     | 4.5.3  | Measurement Results                            | 132 |

|   | 4.6 | Concl  | usions                                         | 140 |

| 5 | RF  | Samp   | ling and Signal Processing                     | 142 |

|   | 5.1 | Introduction                                         | 142         |

|---|-----|------------------------------------------------------|-------------|

|   | 5.2 | Sampled Charge Processing                            | 143         |

|   | 5.3 | Passive Computations                                 | 145         |

|   |     | 5.3.1 Addition                                       | 145         |

|   |     | 5.3.2 Multiplication                                 | 146         |

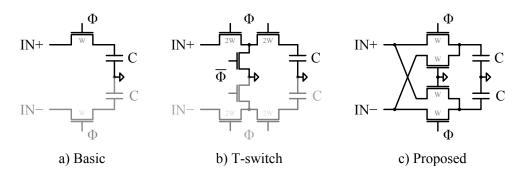

|   |     | 5.3.3 Switching Schemes                              | 148         |

|   | 5.4 | Non-idealities                                       | 149         |

|   | 5.5 | Example Comparison                                   | 150         |

|   | 5.6 | Conclusions                                          | 157         |

| 6 | CR  | AFT: Charge Re-use Analog Fourier Transform          | L <b>60</b> |

|   | 6.1 | Introduction                                         | 160         |

|   | 6.2 | CRAFT Design Concept                                 | 164         |

|   | 6.3 | CRAFT Implementation                                 | 173         |

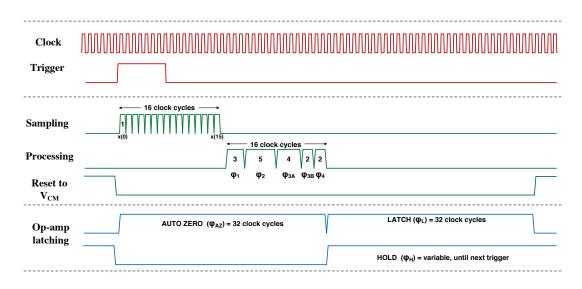

|   |     | 6.3.1 Sampler                                        | 175         |

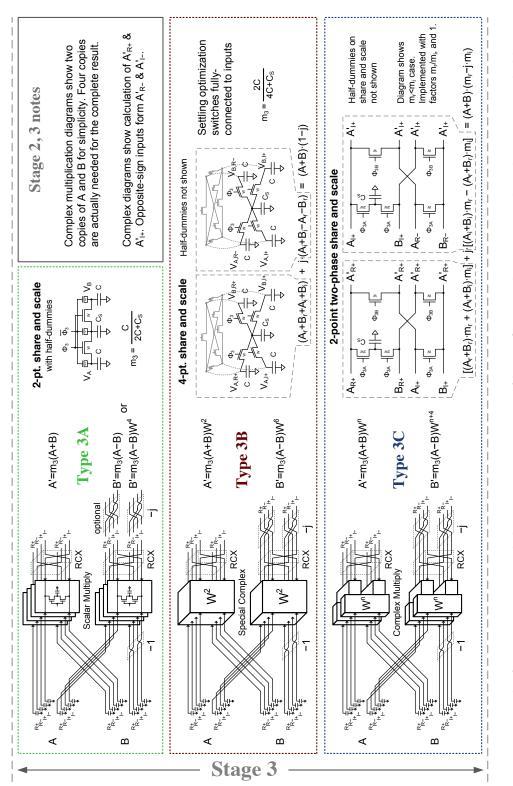

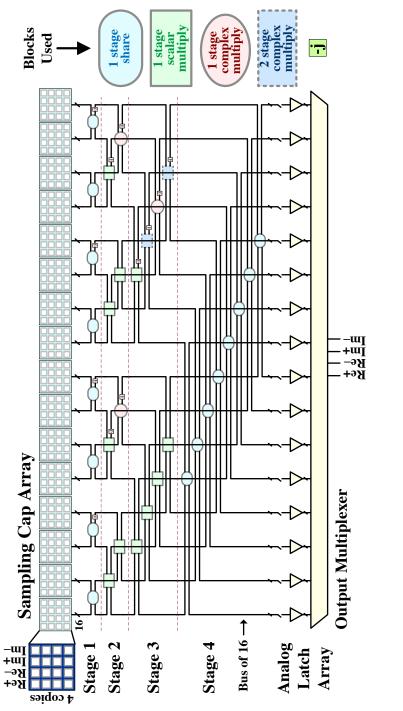

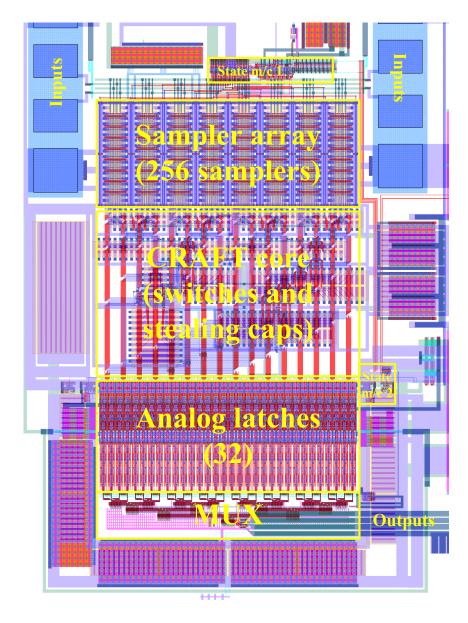

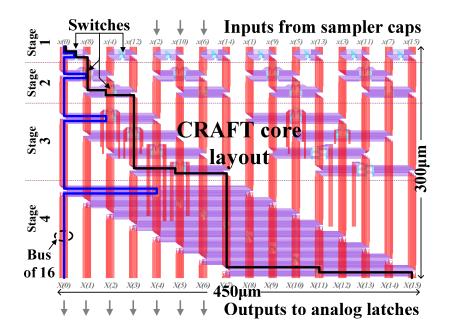

|   |     | 6.3.2 CRAFT Core                                     | 180         |

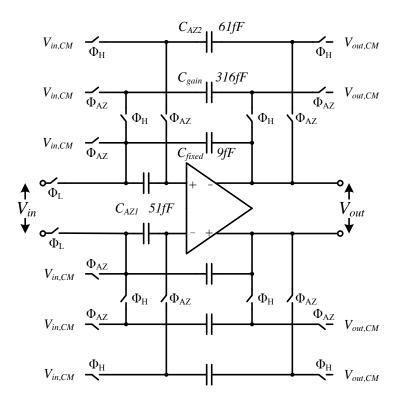

|   |     | 6.3.3 Output Latch                                   | 185         |

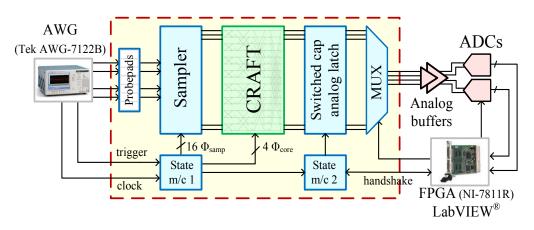

|   |     | 6.3.4 State Machines                                 | 187         |

|   | 6.4 | Circuit Non-idealities and Optimization              | 188         |

|   |     | 6.4.1 Noise                                          | 189         |

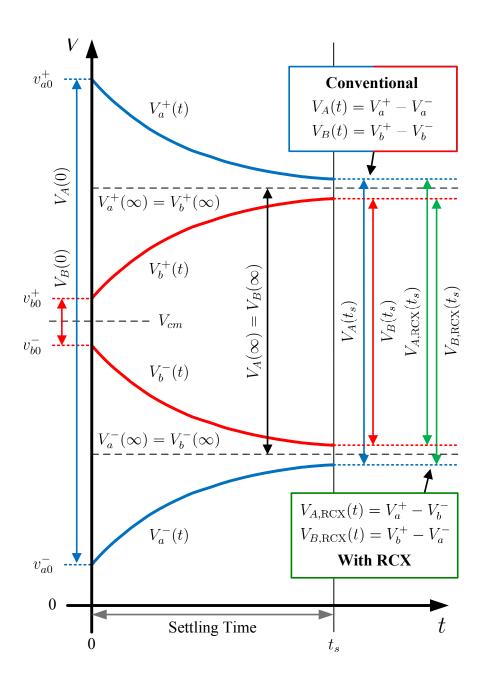

|   |     | 6.4.2 Incomplete Settling                            | 192         |

|   |     | 6.4.3 Operand-dependent Processing-switch Resistance | 198         |

|   |       | 6.4.4  | Clock Feed-through                                         | 198 |

|---|-------|--------|------------------------------------------------------------|-----|

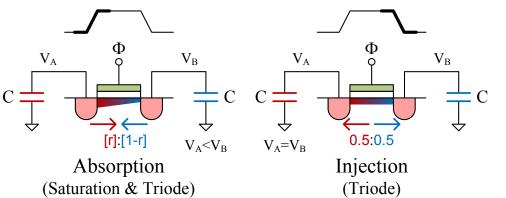

|   |       | 6.4.5  | Charge Injection and Absorption                            | 200 |

|   | 6.5   | Desigr | Methodology and Optimization                               | 202 |

|   |       | 6.5.1  | Architecture Choice                                        | 203 |

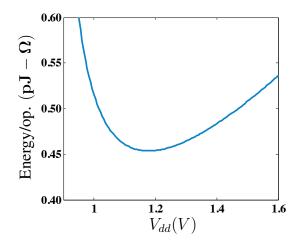

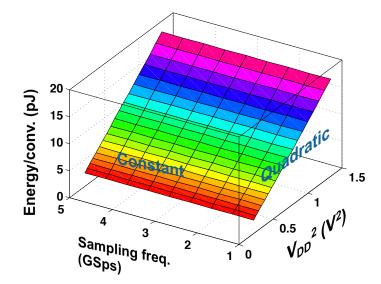

|   |       | 6.5.2  | Energy Optimization                                        | 204 |

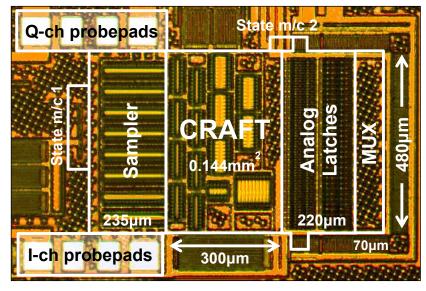

|   | 6.6   | Measu  | rement Results                                             | 206 |

|   |       | 6.6.1  | Calibration                                                | 206 |

|   |       | 6.6.2  | Test Setup                                                 | 208 |

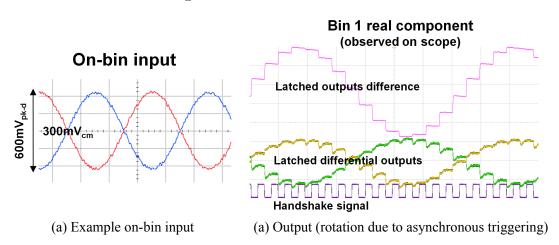

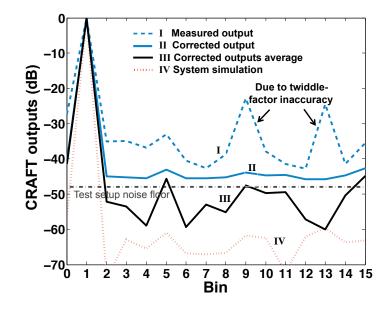

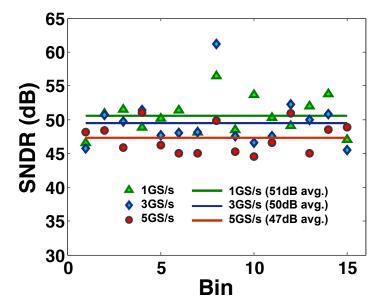

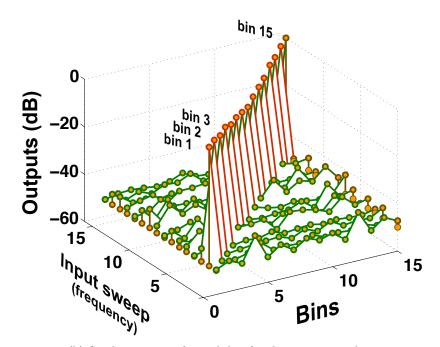

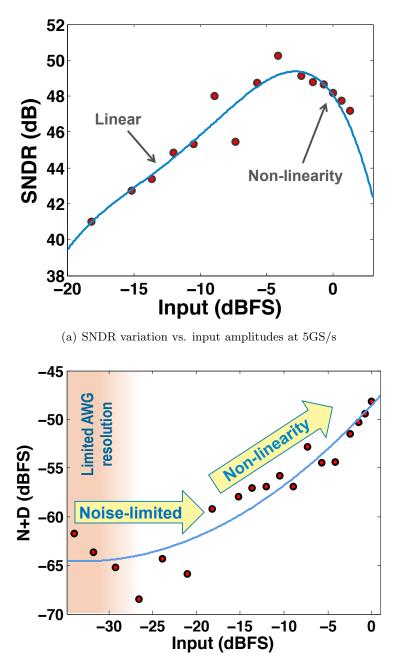

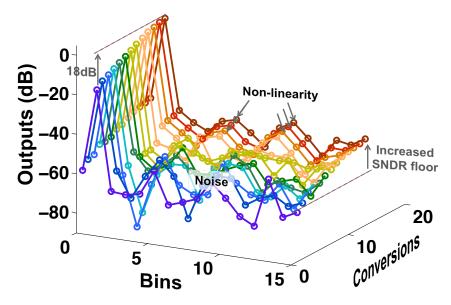

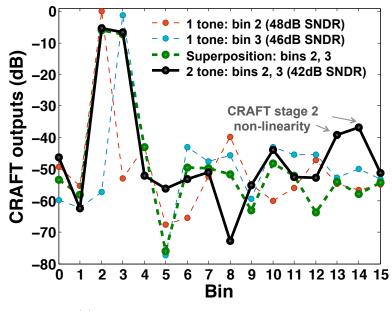

|   |       | 6.6.3  | On-bin 1-tone Measurements                                 | 210 |

|   |       | 6.6.4  | On-bin 2-tone Measurements                                 | 212 |

|   |       | 6.6.5  | Power Consumption                                          | 213 |

|   | 6.7   | Conclu | usion                                                      | 213 |

| 7 | Con   | clusio | ns & Contributions                                         | 220 |

|   | 7.1   | Remai  | rks                                                        | 221 |

|   | 7.2   | Contri | ibutions                                                   | 224 |

|   |       | 7.2.1  | Signaling: Frequency Agility using Wide-tuning VCOs        | 225 |

|   |       | 7.2.2  | Spectrum Sensing: Charge Domain RF Front-end for Low-power |     |

|   |       |        | Digitization                                               | 226 |

| R | efere | nces   |                                                            | 228 |

| A | ppei  | ndix A | . SCF                                                      | 250 |

| Appendix B. Further VCO Capacitor Array Optimization | 255 |

|------------------------------------------------------|-----|

| B.0.3 Capacitance Boosting                           | 256 |

| B.0.4 Simulation Results                             | 258 |

| Appendix C. CRAFT matrices                           | 262 |

| Appendix D. Acronyms                                 | 267 |

| D.1 Acronyms                                         | 267 |

# List of Tables

| 3.1 | Summary of switched inductances                                  | 72  |

|-----|------------------------------------------------------------------|-----|

| 3.2 | Capacitor array switch sizing (lower frequency bank)             | 85  |

| 3.3 | VCO Performance Comparison                                       | 91  |

| 4.1 | VCO summary                                                      | 119 |

| 4.2 | Table for comparison with other PLLs                             | 140 |

| 6.1 | Summary of noise contribution in CRAFT                           | 192 |

| 6.2 | Table showing the CRAFT output SNDR and SFDR with full-scale in- |     |

|     | puts for single-tone on-bin inputs                               | 212 |

| 6.3 | Table for comparison with other FFT implementations              | 219 |

| B.1 | VCO Performance Comparison                                       | 261 |

| D.1 | Acronyms                                                         | 267 |

# List of Figures

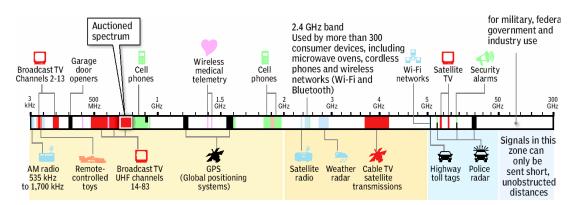

| 1.1 | Frequency spectrum allocation in the United States (Source: New Amer-                |    |

|-----|--------------------------------------------------------------------------------------|----|

|     | ica Foundation, MCT, howstuffworks.com; Graphic: Nathaniel Levine,                   |    |

|     | Sacramento Bee)                                                                      | 2  |

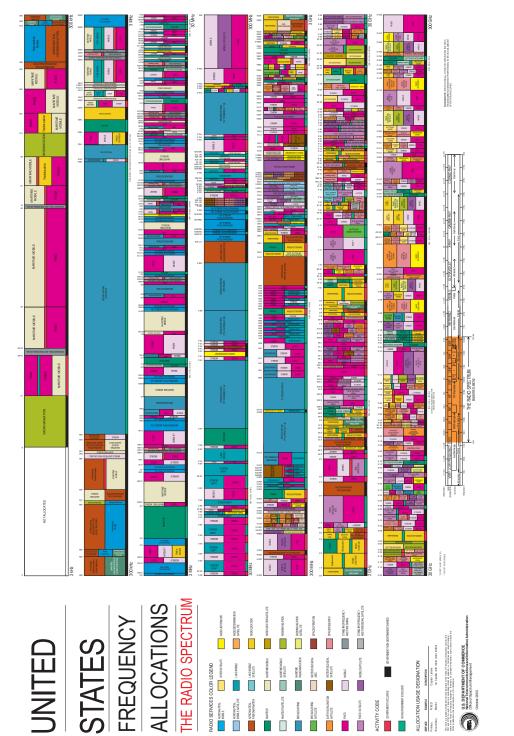

| 1.2 | FCC spectrum allocation in the USA                                                   | 4  |

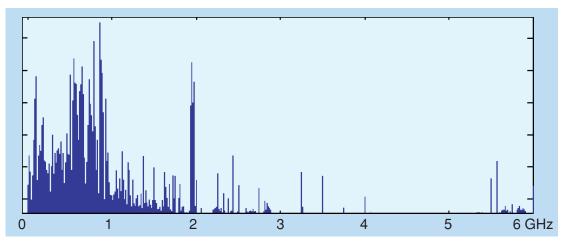

| 1.3 | Spectrum utilization in downtown Berkeley showing $30\%$ usage below                 |    |

|     | 3GHz and 0.5% between $3-6$ GHz [3] $\ldots$ $\ldots$ $\ldots$                       | 5  |

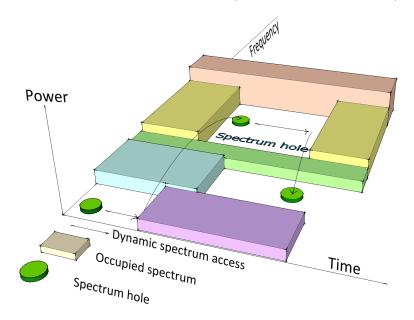

| 1.4 | Concept of DSA                                                                       | 6  |

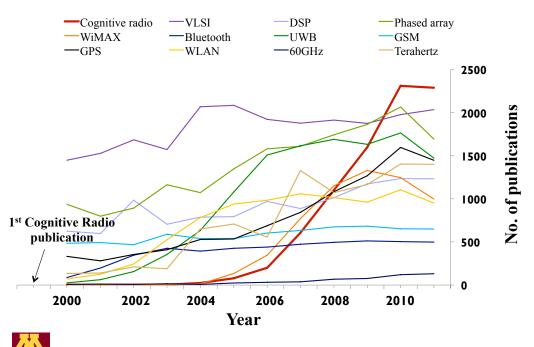

| 1.5 | Number of publications on different research areas in the last decade                | 8  |

| 1.6 | Functionality of an envisioned cognitive radio                                       | 9  |

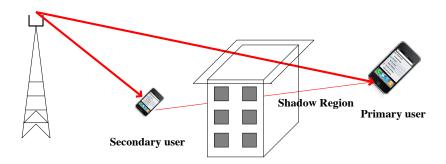

| 1.7 | The hidden terminal problem in cognitive radios $\ldots \ldots \ldots \ldots \ldots$ | 10 |

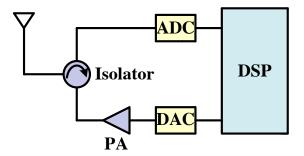

| 2.1 | Functionality of an envisioned software radio by J. Mitola [7] $\ldots$              | 14 |

| 2.2 | A narrowband, wide-tuning signaling/scanning approach for signal recep-              |    |

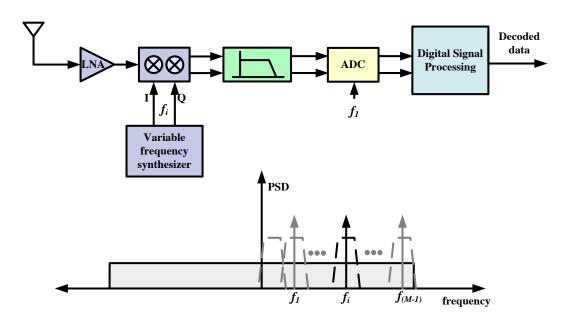

|     | tion and decoding                                                                    | 17 |

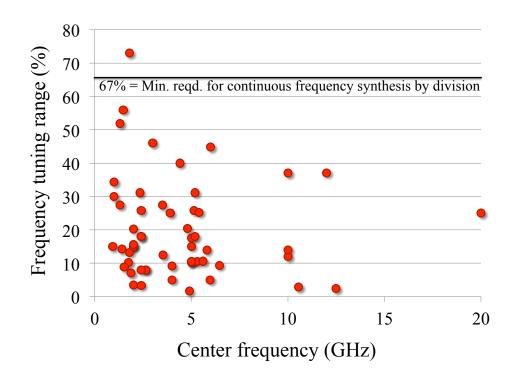

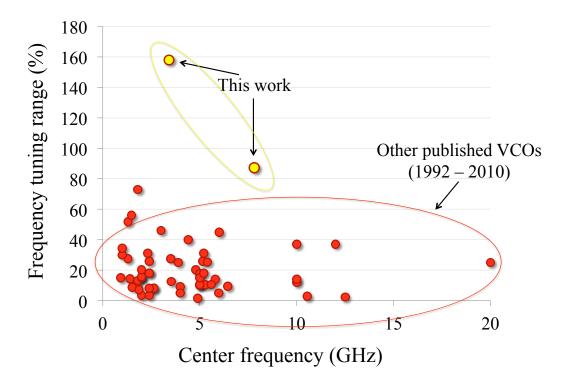

| 2.3  | A survey of frequency tuning range of LC VCOs published in IEEE jour-      |    |

|------|----------------------------------------------------------------------------|----|

|      | nals and conference proceedings appearing between 1992 and 2010 $$         | 21 |

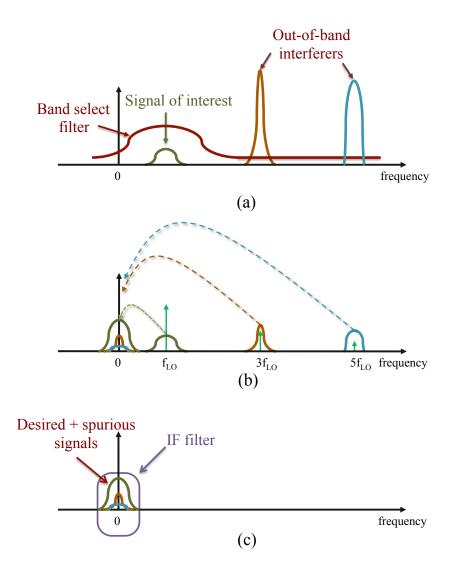

| 2.4  | The problem of harmonic down-conversion in a receiver                      | 23 |

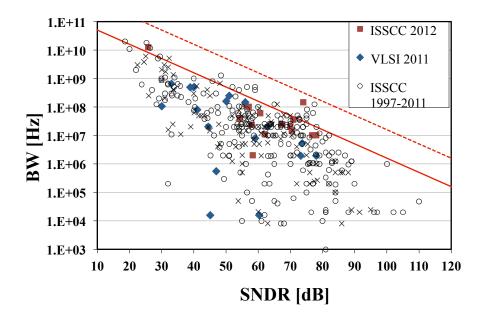

| 2.5  | A survey of ADCs from 1997-2012 [60]                                       | 27 |

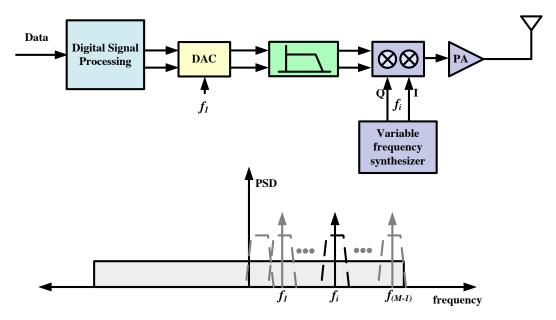

| 2.6  | A narrowband, wide-tuning approach for signal transmission $\ . \ . \ .$ . | 28 |

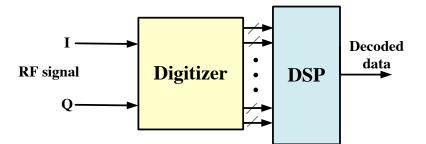

| 2.7  | A wideband RF to digital conversion architecture for spectrum sensing .    | 31 |

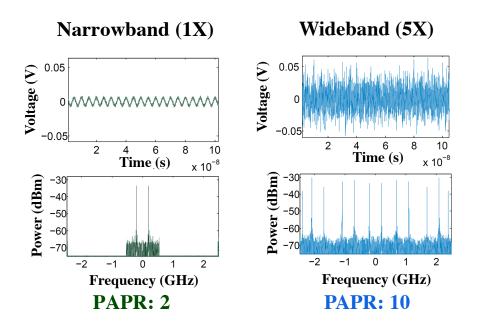

| 2.8  | PAPR increase in wideband signals compared to narrowband signals           | 32 |

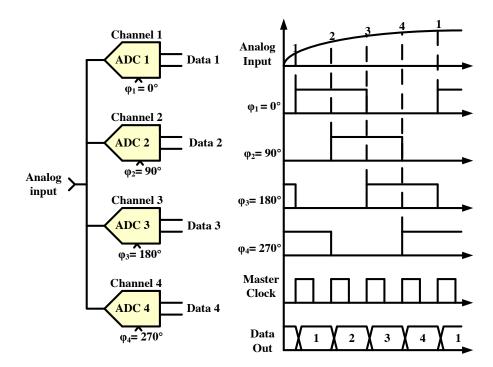

| 2.9  | Time interleaved ADCs for broadband channelization                         | 33 |

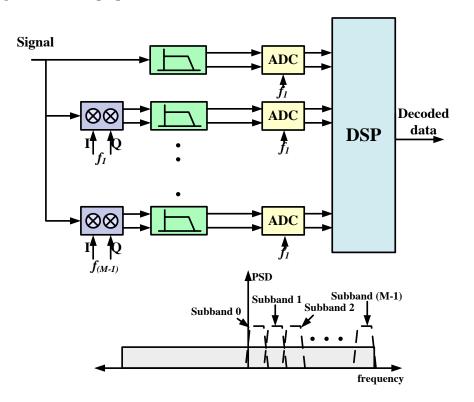

| 2.10 | Low pass filterbank approach for channelization                            | 34 |

| 2.11 | An envisioned SDR architecture enabled by CRAFT $\hdotspace{1.5}$          | 35 |

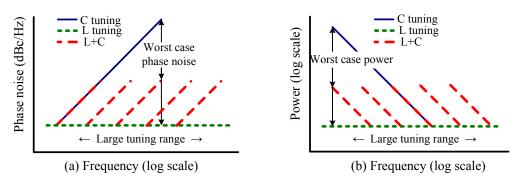

| 3.1  | VCO power and phase noise for alternate frequency tuning options           | 42 |

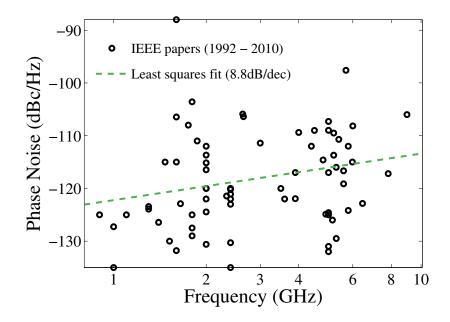

| 3.2  | A literature survey of LC VCO phase noise versus frequency (log scale) in  |    |

|      | IEEE journals and conference proceedings appearing between 1992 and        |    |

|      | 2010                                                                       | 43 |

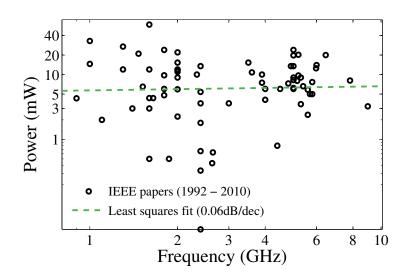

| 3.3  | A literature survey of LC VCO power versus frequency (log log plot) in     |    |

|      | IEEE journals and conference proceedings appearing between 1992 and        |    |

|      | 2010                                                                       | 46 |

| 3.4  | Summary of design methodology described in Section 3.3 $\ldots$            | 50 |

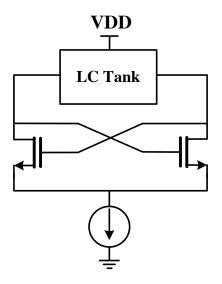

| 3.5  | Cross-coupled nMOS pMOS topology used for the prototype design             | 51 |

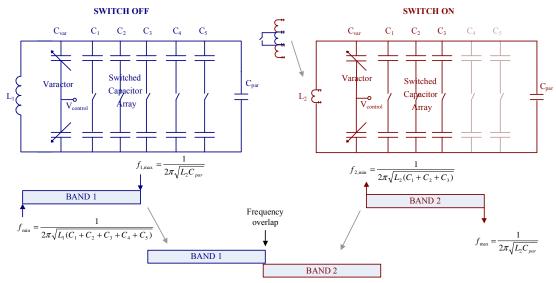

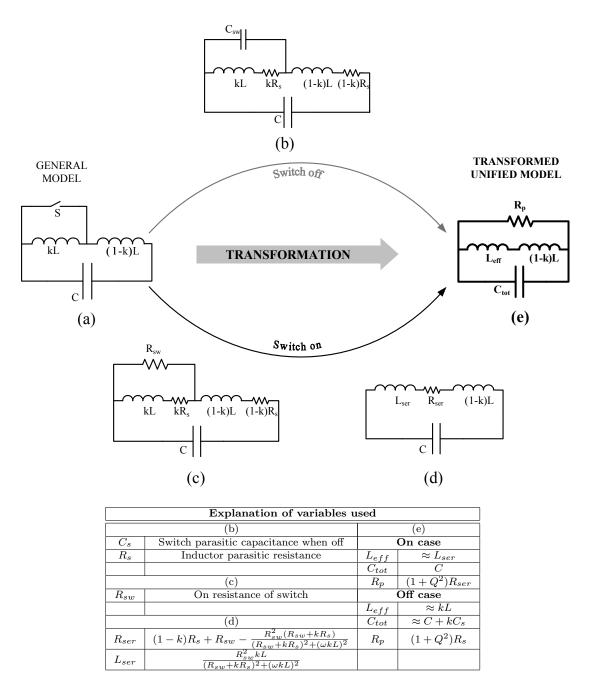

| 3.6  | Modeling of the switched resonator, and parallel series transformations:                         |    |

|------|--------------------------------------------------------------------------------------------------|----|

|      | (a) Simple model for switched resonator (b) Resonator when the switch                            |    |

|      | is off (c) Resonator when the switch is on (d) All parasitic resistances                         |    |

|      | absorbed into Rs when the switch is on (e) Parallel RLC equivalent for                           |    |

|      | both switch on and off cases                                                                     | 52 |

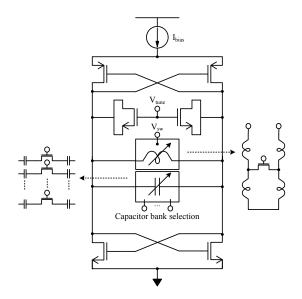

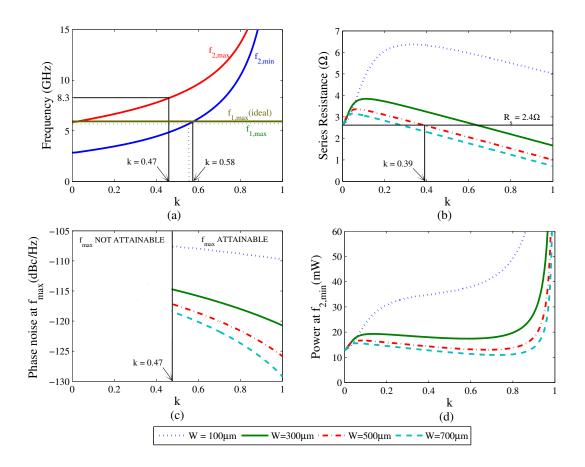

| 3.7  | Calculated values vs. switching ratio $(k)$ and nMOS switch widths (W                            |    |

|      | for a constant L = 120nm) (a) Frequencies $f_{1,max}$ , $f_{2,min}$ , and $f_{2,max}$            |    |

|      | which provides a lower and an upper limit for $k$ based on the given                             |    |

|      | specifications, (b) $R_{ser}$ (see Fig. 3.6(d)); here $r(\text{Fig. 3.6(d)}) = 2.64\Omega$ , (c) |    |

|      | Worst case phase noise calculated at $f_{max}$ , and (d) Worst case power                        |    |

|      | dissipation calculated at $f_{2,min}$                                                            | 54 |

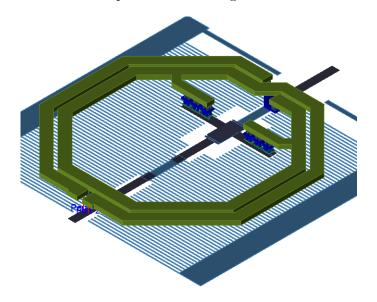

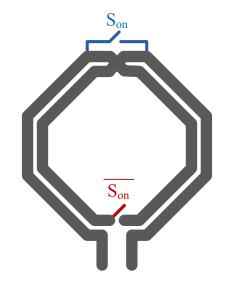

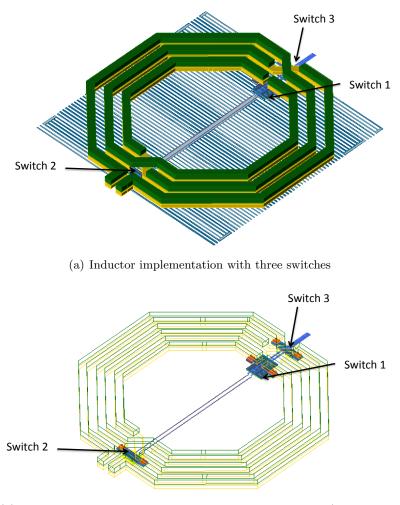

| 3.8  | 3-D view of the switched inductor with the switch shown at a lower tier                          |    |

|      | in the center of the inductor                                                                    | 57 |

| 3.9  | A scheme to eliminate the parasitic current in the inner inductor loop for                       |    |

|      | a switched inductor                                                                              | 59 |

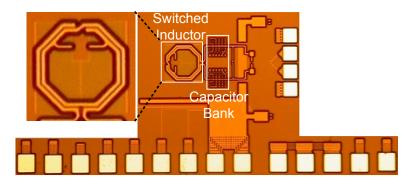

| 3.10 | Die photograph of wide tuning range VCO prototype                                                | 62 |

| 3.11 | Measured tuning range versus capacitance in terms of the 'x', where 'x'                          |    |

|      | is the capacitance of an unit switched capacitor $\ldots \ldots \ldots \ldots \ldots$            | 64 |

| 3.12 | Measured power dissipation versus frequency (log log plot)                                       | 65 |

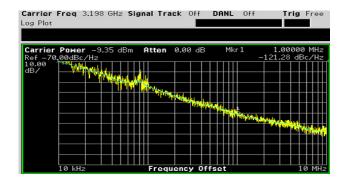

| 3.13 | Measured VCO phase noise across offset frequencies from a $3.28 \text{GHz}$ carrier              | 67 |

| 3.14 | Measured phase noise at 1MHz offset versus frequency (log scale)                                 | 67 |

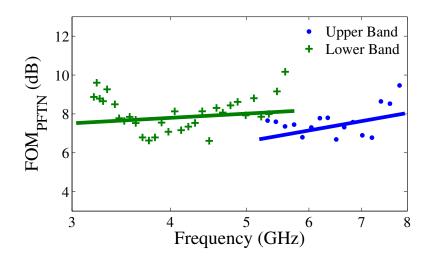

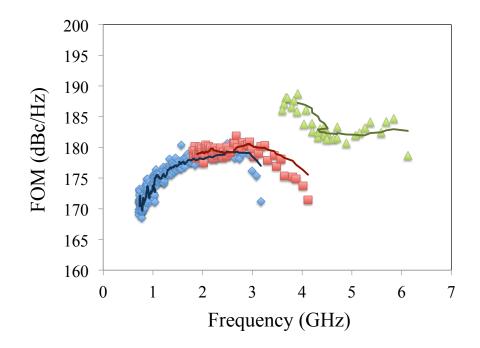

| 3.15 | $FOM_{PFTN}$ versus frequency (log scale)                                                                                                                 | 68 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

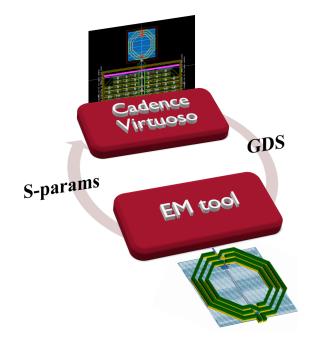

| 3.16 | Summary of partial EM simulation techniques used for VCO design $~$ .                                                                                     | 69 |

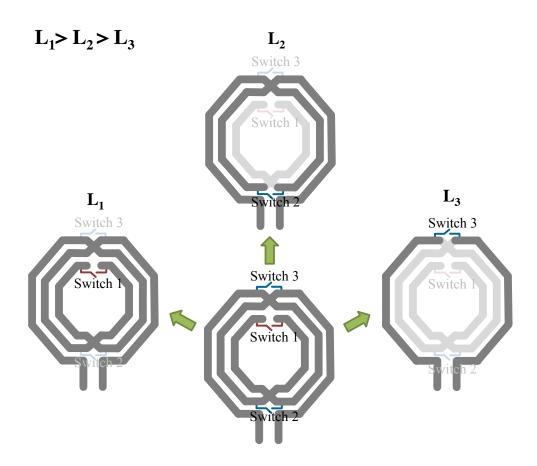

| 3.17 | An inductor with 3 switches producing 3 inductances                                                                                                       | 70 |

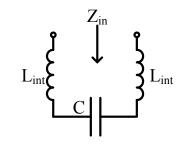

| 3.18 |                                                                                                                                                           | 71 |

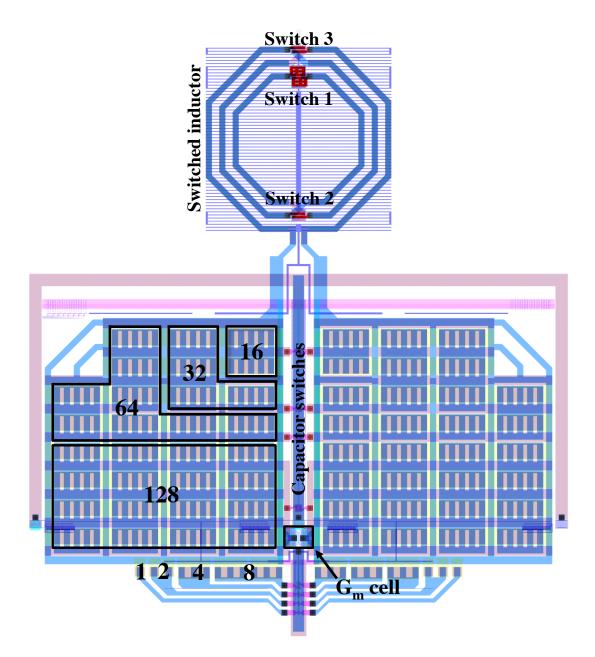

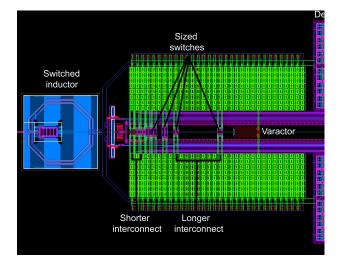

| 3.19 | A layout snapshot of the VCO prototype II showing the switched capac-                                                                                     |    |

|      | itor array design                                                                                                                                         | 74 |

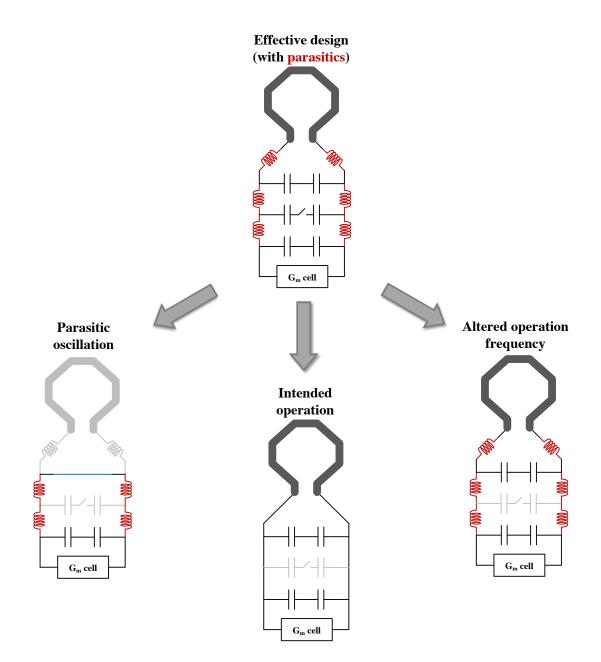

| 3.20 | The adverse effects of interconnect inductance on VCO performance; par-                                                                                   |    |

|      | asitic inductors are shown in red                                                                                                                         | 75 |

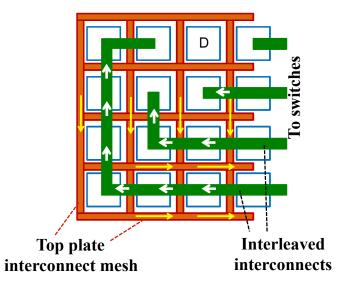

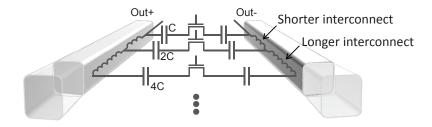

| 3.21 | Interleaved interconnects to reduce the effect of interconnect inductance                                                                                 | 80 |

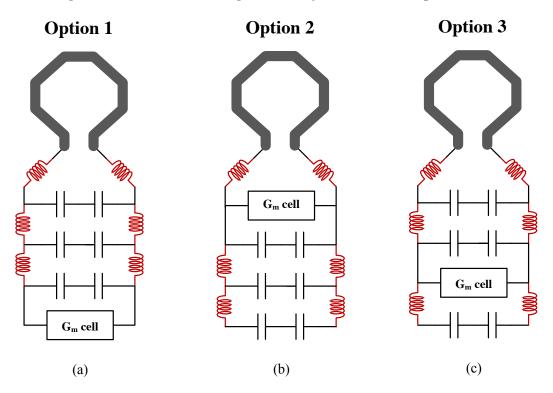

| 3.22 | Different options to place the $G_m$ cell with respect to the tank; intercon-                                                                             |    |

|      | nect parasitic inductance is shown in red                                                                                                                 | 81 |

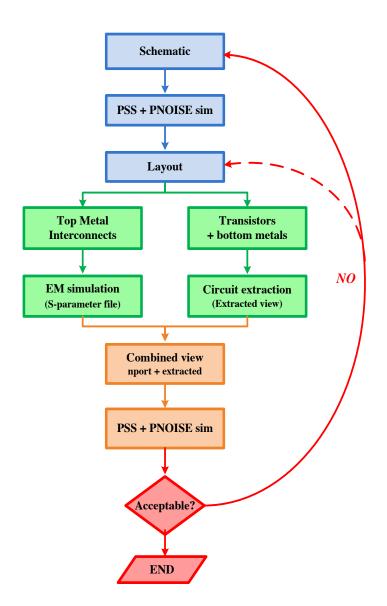

| 3.23 | Electromagnetic simulation assisted VCO design flow                                                                                                       | 83 |

| 3.24 | Diagram showing the connection of capacitors in a capacitor array                                                                                         | 84 |

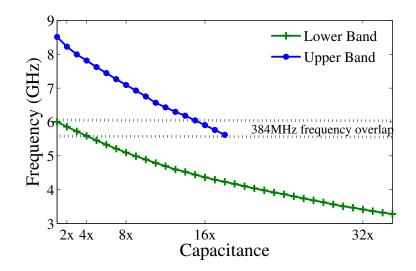

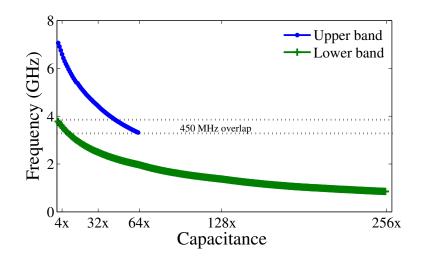

| 3.25 | Frequency tuning range versus capacitance in terms of the 'x', where 'x'                                                                                  |    |

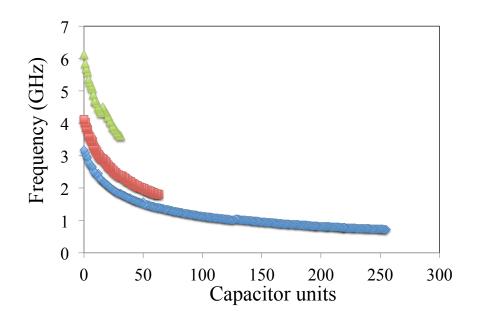

|      | is the capacitance of a unit switched capacitor                                                                                                           | 87 |

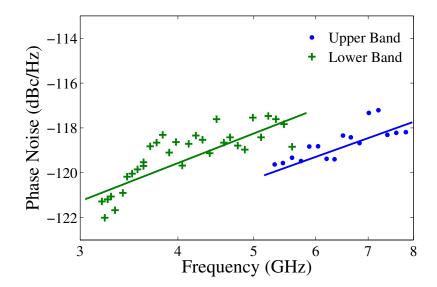

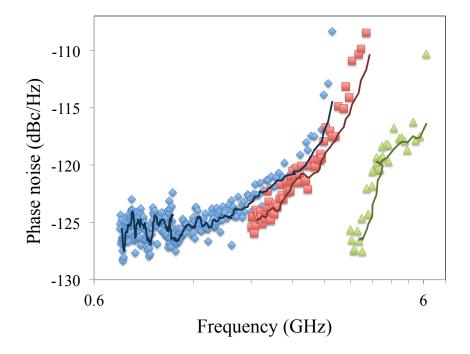

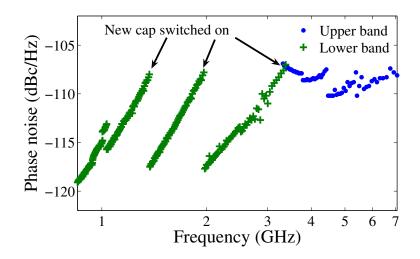

| 3.26 | Variation of phase noise at 1MHz offset with frequency (log scale) $~~.~.~$                                                                               | 88 |

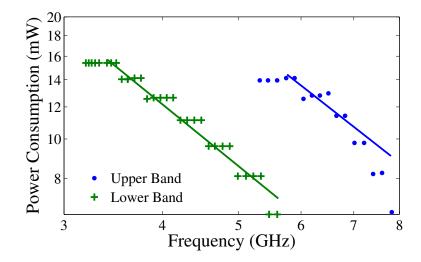

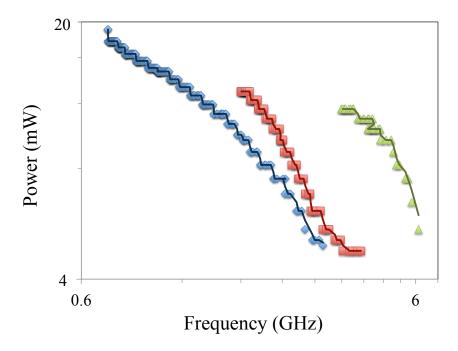

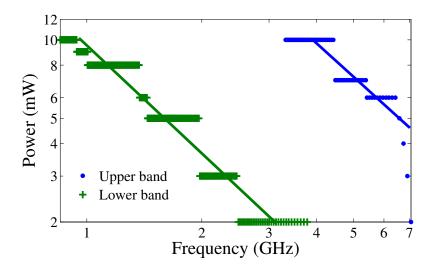

| 3.27 | Variation of VCO core power dissipation with frequency (log log plot) $% \left( \left( {{{\left( {{\left( {\left( {\left( {\left( {\left( {\left( {\left$ | 89 |

| 3.28 | Variation of VCO FOM with frequency (log log plot)                                                                                                        | 90 |

| 3.29 | A comparison of the VCO implementations in this chapter with other                                                                                        |    |

|      | measured implementations between 1999 and 2010 $\ldots \ldots \ldots \ldots$                                                                              | 91 |

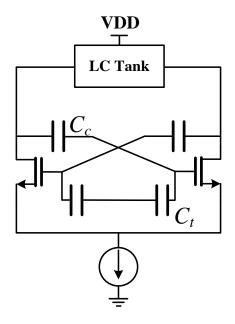

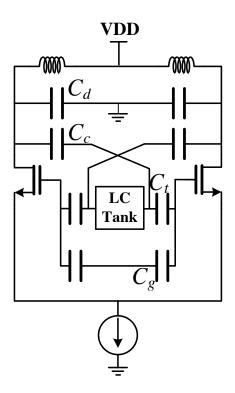

| 4.1  | Cross-coupled VCO: Full circuit                                                                                                                           | 95 |

| 4.2  | Cross-coupled VCO: Half circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

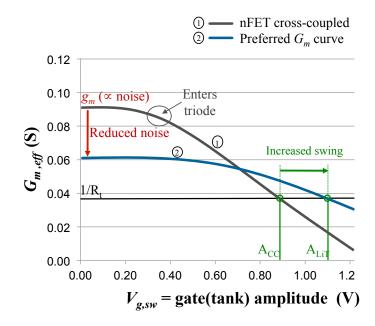

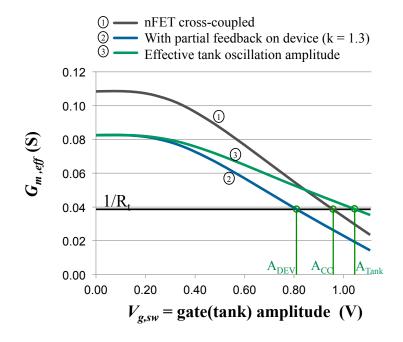

| 4.3  | Transconductance vs. voltage swing showing a typical oscillator $G_m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | curve, and a preferred curve for improved phase noise $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfi$ | 97  |

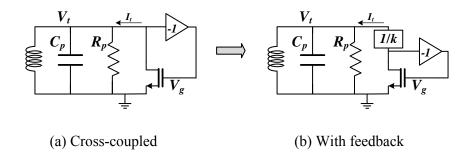

| 4.4  | Feedback concept for $G_m$ linearlization using lower voltage swing on the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | drain node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 98  |

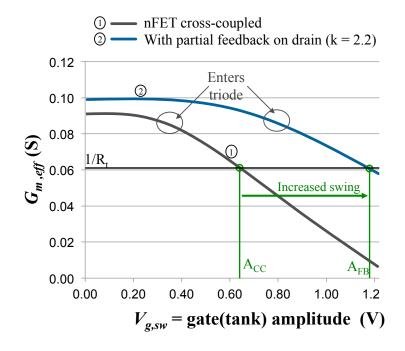

| 4.5  | Transconductance vs. voltage swing showing a typical oscillator $G_m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | curve, and one that uses lower drain voltage swing for linearization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 98  |

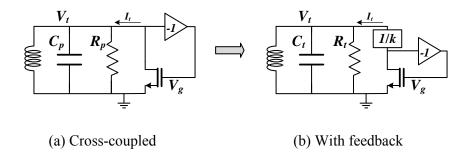

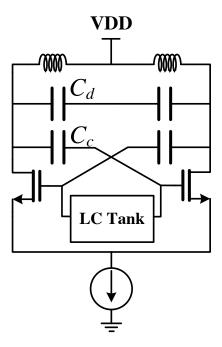

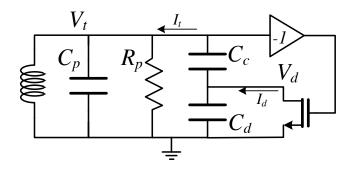

| 4.6  | Feedback concept for $G_m$ linearlization using lower voltage swing for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | active device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 99  |

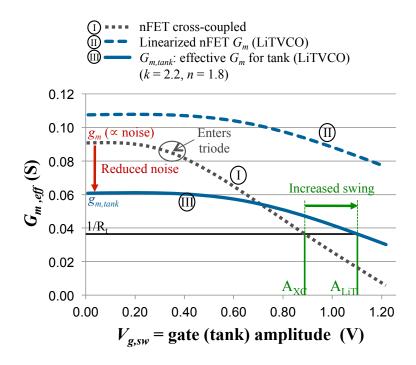

| 4.7  | Transconductance vs. voltage swing showing a typical oscillator $G_m$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|      | curve, and one that uses lower active device swing for linearization $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99  |

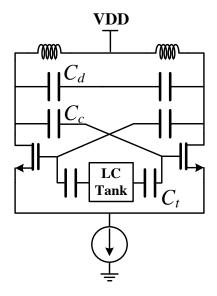

| 4.8  | Drain divider VCO: Full circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 102 |

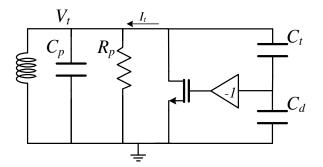

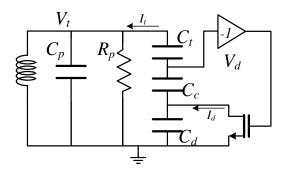

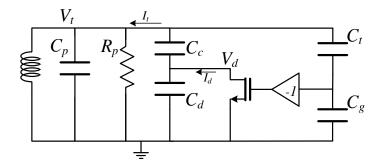

| 4.9  | Drain divider VCO: Half circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 102 |

| 4.10 | Transconductance linearization in LiT VCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 103 |

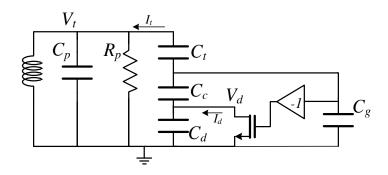

| 4.11 | Gate divider / base divider VCO: Full circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104 |

| 4.12 | Gate divider / base divider VCO: Half circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 104 |

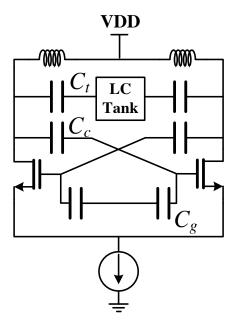

| 4.13 | Gate divider / base divider VCO Type B: Full circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 106 |

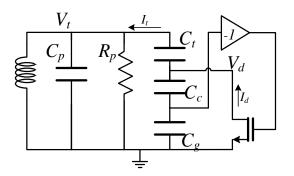

| 4.14 | Gate divider / base divider VCO Type B: Half circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 106 |

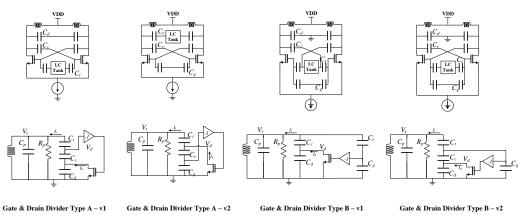

| 4.15 | Gate & drain divider Type A - v1 VCO: Full circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

| 4.16 | Gate & drain divider Type A - v1 VCO: Half circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 108 |

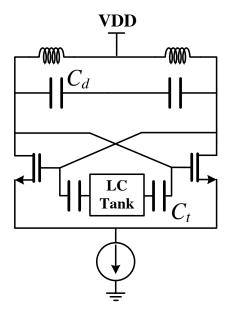

| 4.17 | Gate and drain divider Type A - v2 VCO: Full circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 111 |

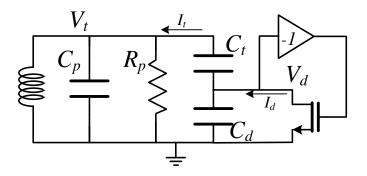

| 4.18 Gate and drain divider Type A - v2 VCO: Half circuit                                |

|------------------------------------------------------------------------------------------|

| 4.19 Gate & drain divider Type B - v1 VCO: Full circuit 113                              |

| 4.20 Gate & drain divider Type B - v1 VCO: Half circuit                                  |

| 4.21 Gate & drain divider Type B - v2 VCO: Full circuit 115                              |

| 4.22 Gate & drain divider Type B - v2 VCO: Half circuit 115                              |

| 4.23 A proposed switch scheme for the high amplitude LiTVCO tank switched                |

| capacitors                                                                               |

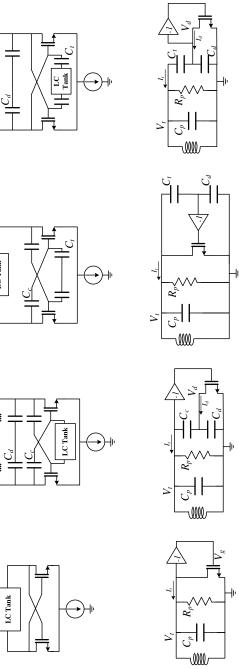

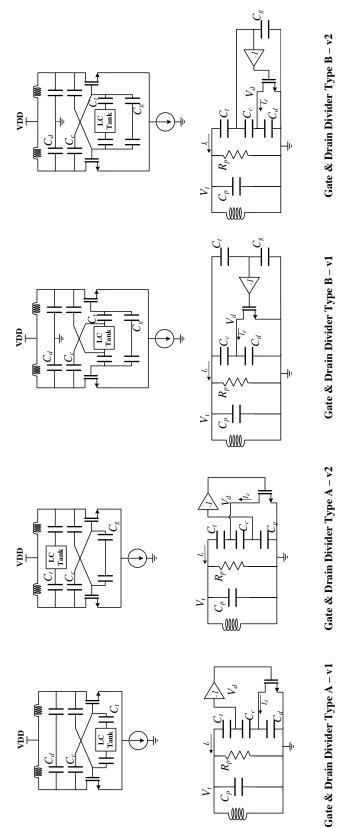

| 4.24 A (diagrammatic) summary of the different VCO topologies discussed (I) $122$        |

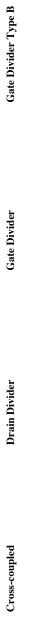

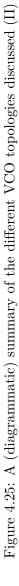

| 4.25 A (diagrammatic) summary of the different VCO topologies discussed (II) $123$       |

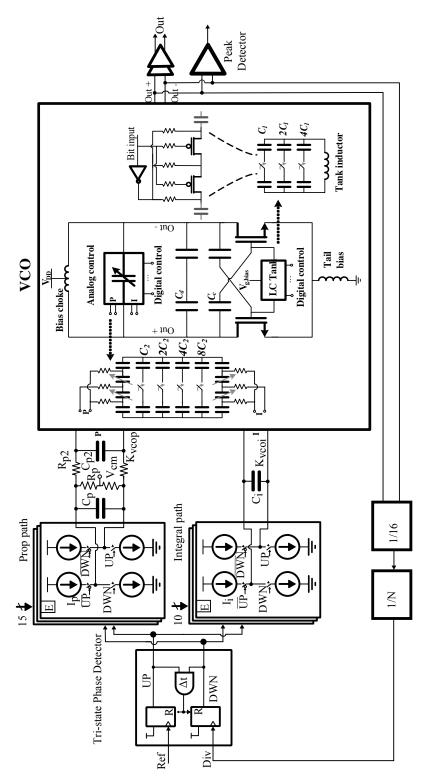

| 4.26 Block diagram of the PLL showing the detailed VCO schematic including               |

| frequency tuning schemes 126                                                             |

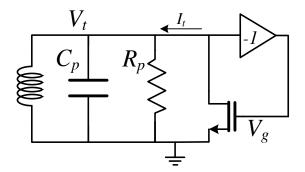

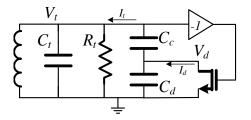

| 4.27 An equivalent half circuit model of the LiT VCO showing the capacitive              |

| feedback technique employed (biasing details not shown) 127                              |

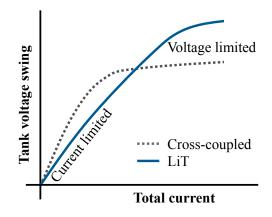

| 4.28 Voltage limited regime extension in LiT VCO                                         |

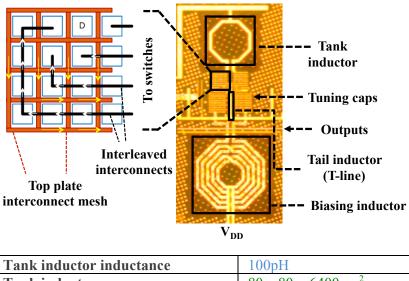

| 4.29 Die photo of the LiT VCO showing the capacitor array design details for             |

| minimizing interconnect inductance, and other implementation details $.$ 131             |

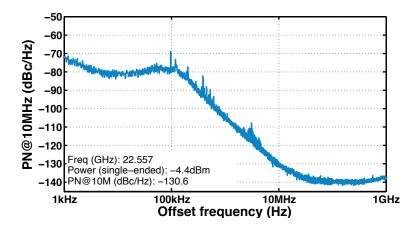

| 4.30 Phase noise vs. frequency offset from a 22GHz carrier                               |

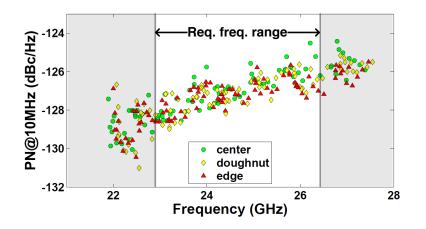

| 4.31 Phase noise over the tuning range for different die locations on a wafer . $133$    |

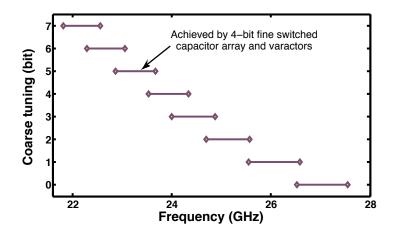

| 4.32 Coarse frequency tuning showing frequency overlap                                   |

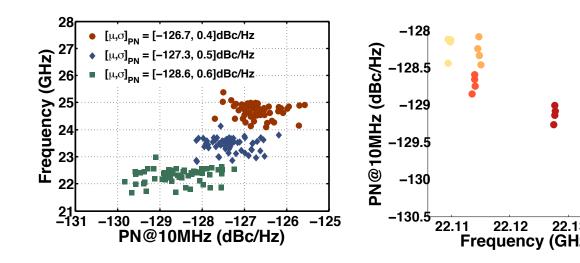

| 4.33 Robustness of the LiT VCO design to process variations (die to die) $\ . \ . \ 134$ |

| 4.34 Robustness of the LiT VCO design to temperature variations $\ldots \ldots 134$      |

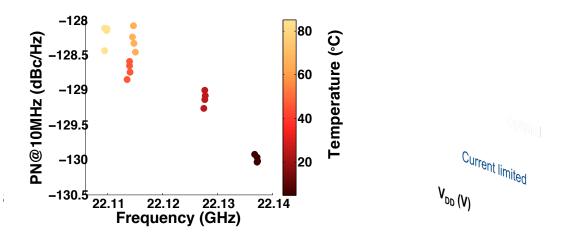

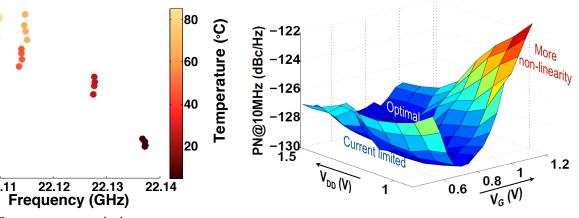

| 4.35 | Robustness of the LiT VCO design to supply variations                        | 135 |

|------|------------------------------------------------------------------------------|-----|

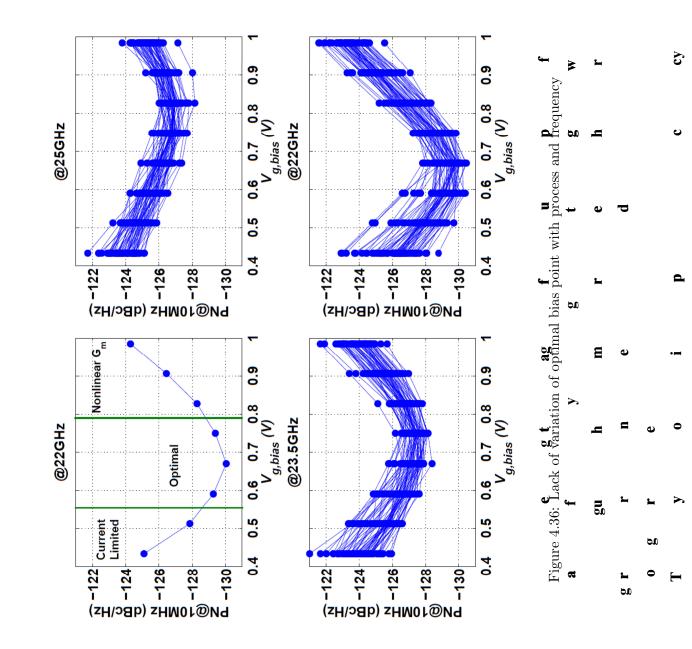

| 4.36 | Lack of variation of optimal bias point with process and frequency $\ . \ .$ | 136 |

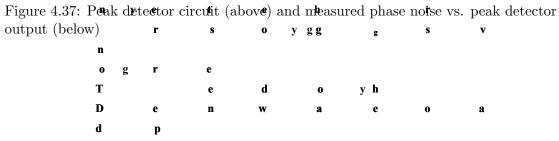

| 4.37 | Peak detector circuit (above) and measured phase noise vs. peak detector     |     |

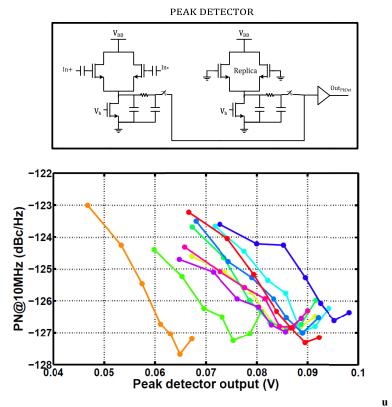

|      | output (below)                                                               | 138 |

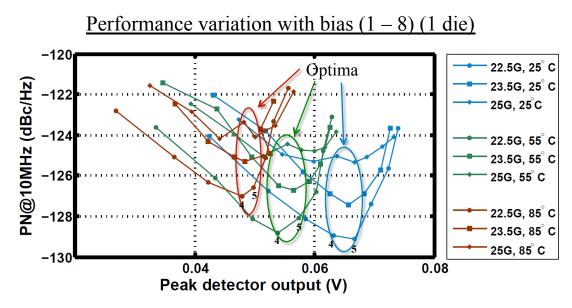

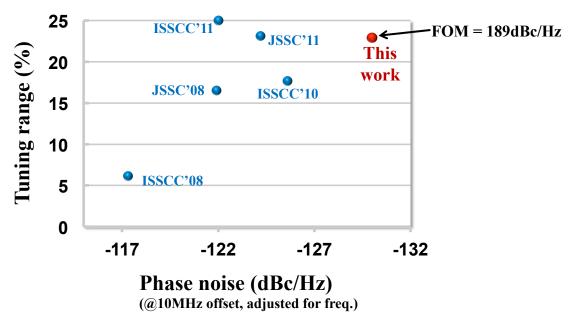

| 4.38 | Phase noise vs. peak detector output across frequency and temperature        | 139 |

| 4.39 | Phase noise and tuning range comparison with other PLLs for 60GHz            |     |

|      | applications                                                                 | 141 |

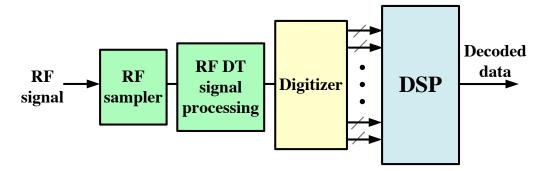

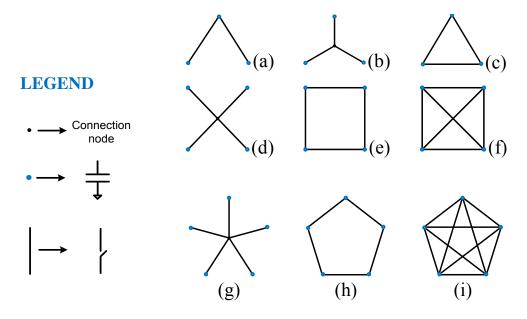

| 5.1  | A spectrum sensing architecture based on RF sampling and signal pro-         |     |

|      | cessing                                                                      | 143 |

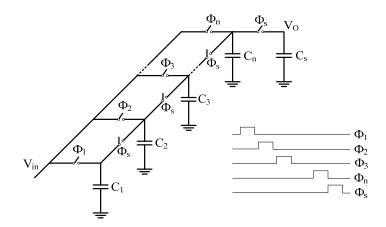

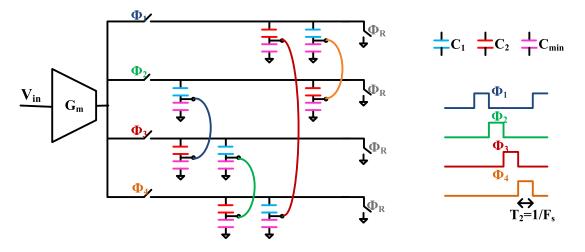

| 5.2  | Switched capacitor implementation of a passive N-tap FIR with a deci-        |     |

|      | mation by N                                                                  | 144 |

| 5.3  | Techniques for charge domain addition and multiplication operations          | 146 |

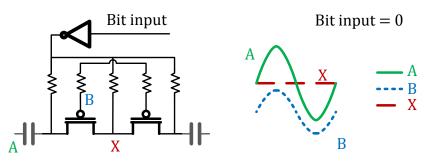

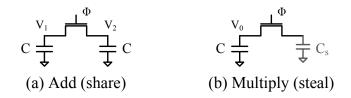

| 5.4  | Different switching topologies for charge domain operations $\ldots \ldots$  | 149 |

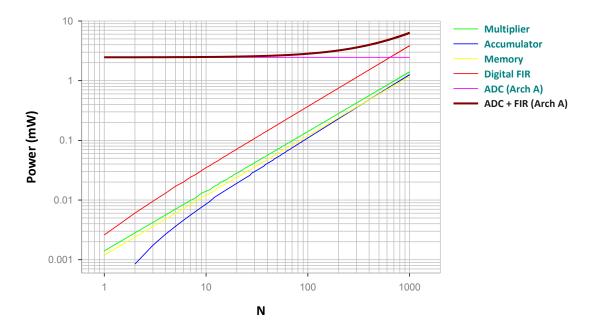

| 5.5  | Receiver architecture incorporating digital domain FIR filtering             | 151 |

| 5.6  | Receiver architecture incorporating analog domain FIR filtering              | 152 |

| 5.7  | Power dissipation for different functions in Arch A vs. number of taps in    |     |

|      | the FIR filter                                                               | 153 |

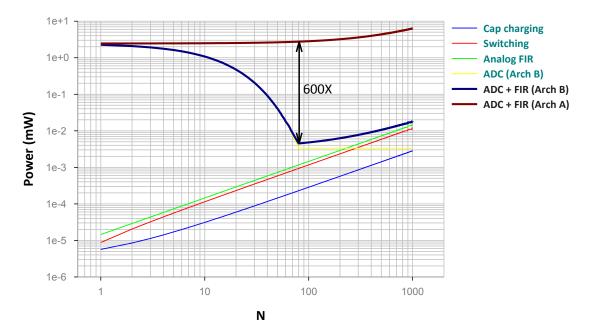

| 5.8  | Architecture for analog 2-tap FIR using passive switched capacitors $~$      | 155 |

| 5.9  | Power dissipation for different functions in Arch B vs. number of taps       |     |

|      | in the FIR filter; also shown is the total (ADC and FIR) Arch A power        |     |

|      | dissipation for comparison purposes                                          | 158 |

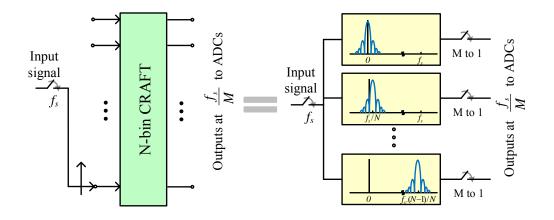

| 6.1  | The frequency domain functional equivalent of a DFT comprising of N-    |     |

|------|-------------------------------------------------------------------------|-----|

|      | path bandpass filters                                                   | 161 |

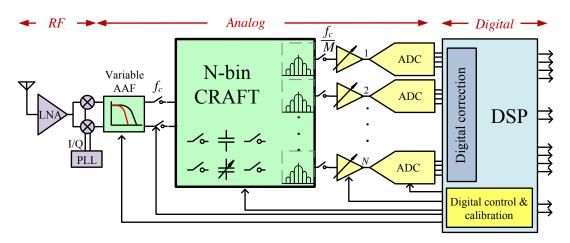

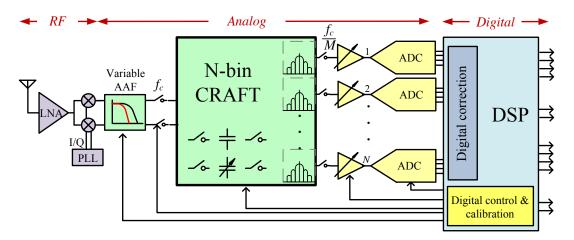

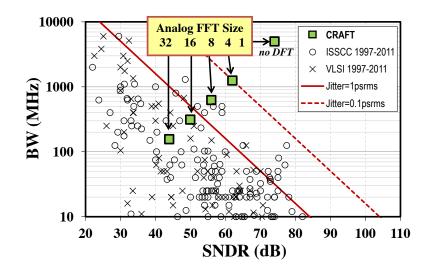

| 6.2  | An envisioned SDR architecture enabled by CRAFT                         | 162 |

| 6.3  | Feasibility of ADCs vs. bin size of the CRAFT front-end                 | 163 |

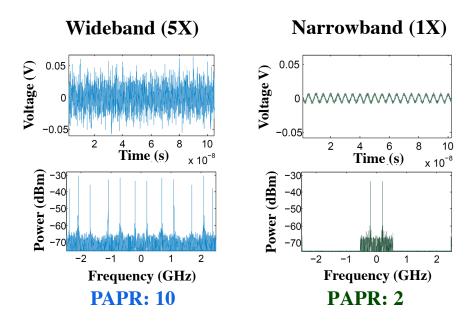

| 6.4  | Wideband and channelized signals showing dynamic range reduction        | 164 |

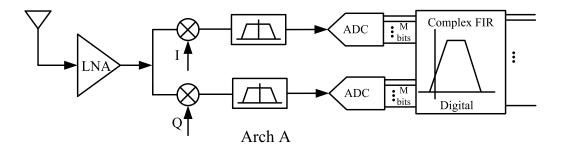

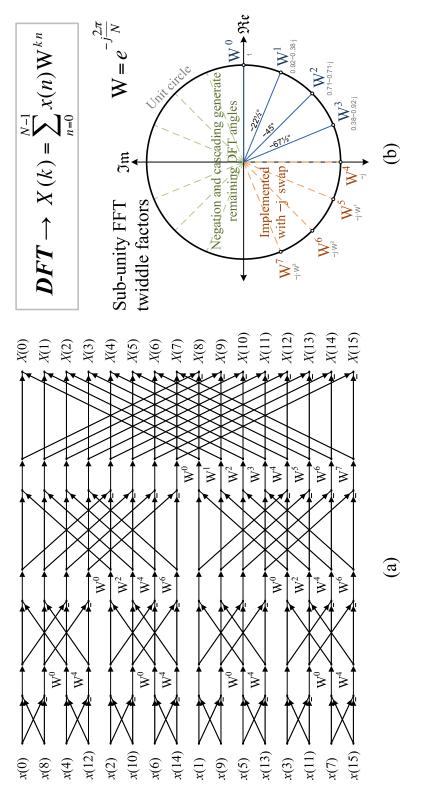

| 6.5  | (a) A 16 point radix-2 FFT signal flow diagram using the decimation-    |     |

|      | in-time algorithm, and (b) DFT sub-unity twiddle factors on the unit    |     |

|      | circle                                                                  | 166 |

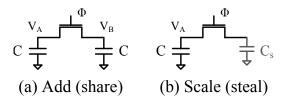

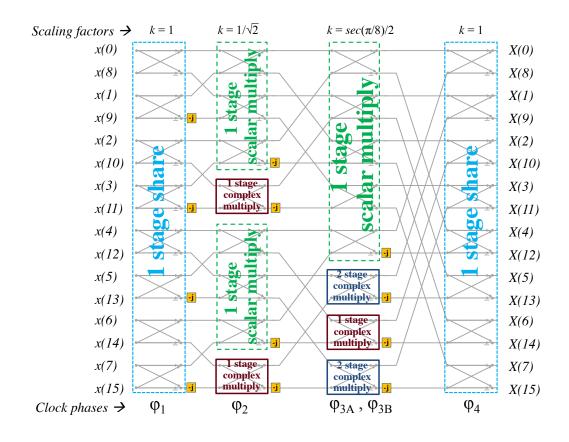

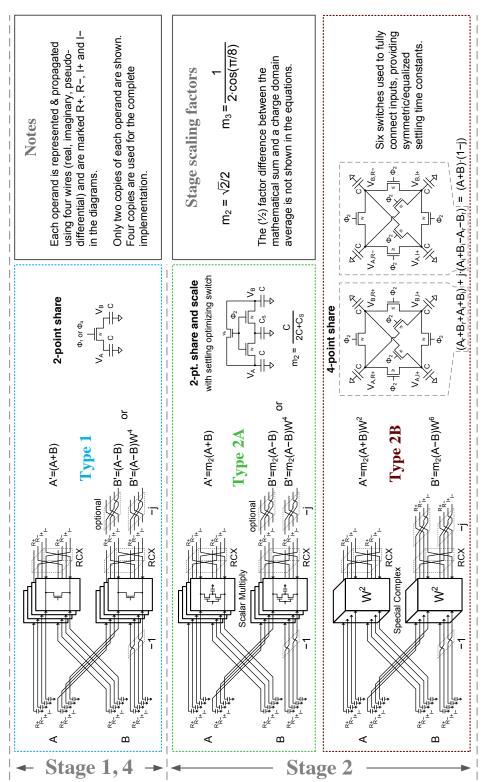

| 6.6  | Conceptual implementation of addition and sub-unity scaling operations  |     |

|      | on which CRAFT is based                                                 | 167 |