## LOW-LATENCY LOW-COMPLEXITY CHANNEL DECODER ARCHITECTURES FOR MODERN COMMUNICATION SYSTEMS

# A DISSERTATION SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA BY

Chuan Zhang

## IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Professor Keshab K. Parhi, Advisor

December 2012

#### Acknowledgements

First of all, I wish to thank my advisor, Professor Keshab K. Parhi, for his continuing and fatherly encouragement, guidance, and financial support throughout my entire Ph.D. study at the University of Minnesota. Before I got the admission to University of Minnesota, I was always dreaming to join this group. I am very lucky and grateful that I have had research opportunities under Professor Parhi's supervision in the area of VLSI digital signal processing. Professor Parhi will still be my mentor even after my graduation.

I would like to thank Professor Gerald E. Sobelman, Professor Marc Riedel, and Professor Victor Reiner for their support as members of my Ph.D. committee. I would like to thank the Graduate School of University of Minnesota for their financial support by the Three-Year Graduate School Fellowship and Doctoral Dissertation Fellowship.

My thanks also go to current and former members of our research group. I would like to thank Bo Yuan for our numerous discussions on a variety of research topics. I would like to thank Yun Sang Park for his consistent engagement and help even after his graduation. I am lucky and happy to have Sohini Roy Chowdhury as one of my best friends. Also, I am grateful to Tingting Xu, Yingbo Hu, Sayed Ahmad Salehi, Te-Lung Kung, Manohar Ayinala, Yingjie Lao, Zisheng Zhang, and Lan Luo, for their kind support in my Ph.D. life.

I would like to also thank my friends at University of Minnesota and in my country China, especially Professor Andreas Stein, Zhenzhen Jiang, Ying Zhu, Jianfeng Zheng, Yao Wang, Fei Zheng, Lian Huai, Juan Du, Zhe Zhang, Jieming Yin, Huan Li, Meng Yang, and Changjiang Liu, for their assistance and engagement to continue my studies.

Lastly, I am forever grateful to my parents, my parents in law, and especially my lovely wife, Xiaoqing Chen, for their love, support, and encouragement throughout the years. Without them, I would not have completed my Ph.D. successfully, and my whole life could be of no meanings.

#### **Abstract**

Nowadays, along with the economic and technical progress, modern communication industry is playing a more and more important role in people's lives. The rapid growth of communication industry is benefiting and gradually changing our work, learning, and life styles. It is difficult to imagine what life will be like without smartphones, HDTVs, high-speed networks, and Wi-Fi hotspots. On the other hand, the ever-increasing users' demands force the modern communication systems to be faster, more portable, more reliable, and safer. As an indispensable and important part of modern communication systems, channel decoders are expected to be low-latency, low-complexity, low-error, and wiretap-free. However, developing channel decoders to meet those requirements is quite a struggle. Fortunately, VLSI digital signal processing techniques offer us great facilities to enable channel decoders to advance to new generations.

This thesis commits itself to the efficient VLSI implementation of low-latency low-complexity channel decoders. In order to make our approaches more applicable for variant real-time communication applications, formal design methodologies are proposed. Novel non-binary QC-LDPC decoders with efficient switch networks are presented. For the newly invented polar codes, a family of latency-reduced decoder architectures is also proposed. Comparisons with prior works have demonstrated that the proposed designs show advantages in both decoding throughput and hardware efficiency.

First, a novel design methodology to design low-complexity VLSI architectures for non-binary LDPC decoders is presented. By exploiting the intrinsic shifting and symmetry properties of non-binary quasi-cyclic LDPC (QC-LDPC) codes, significant reduction of memory size and routing complexity can be achieved. These unique features lead to two network-efficient decoder architectures for Class-I and Class-II non-binary QC-LDPC codes, respectively. Comparison results with the state-of-the-art designs show that for the code example of the 64-ary (1260, 630) rate-0.5 Class-I code, the proposed scheme can save up to 70.6% hardware required by switch network, which demonstrates the efficiency of the proposed technique. The proposed design for the 32-ary (992, 496) rate-0.5 Class-II code can achieve a 93.8% switch network complexity reduction compared with conventional approaches. Furthermore, with the help of a generator for possible solution sequences, both forward and backward steps can be eliminated to offer processing convenience of check node unit (CNU) blocks. Results show that the proposed 32-ary (992, 496) rate-0.5 Class-II decoder can achieve 4.47 Mb/s decoding throughput.

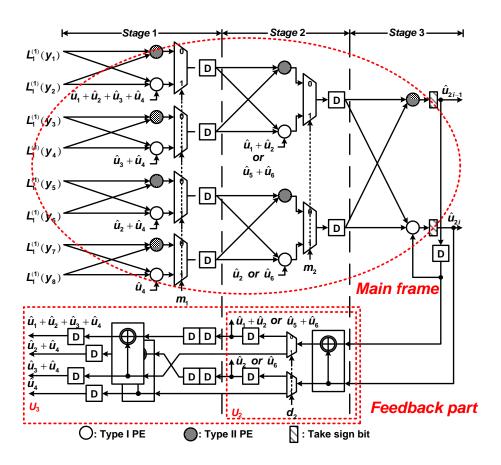

Second, the low-latency sequential SC polar decoder is proposed based on the DFG analysis. The complete gate-level decoder architecture is proposed. The *feedback part* is proposed to generate control signals on-the-fly. The proposed design method is universal and can be employed to design the low-latency sequential SC polar decoder for any codelength. Compared with prior works, this design can achieve twice throughput with similar hardware consumption.

Third, in order to meet the requirements of high-throughput communication systems, both *time-constrained* (TC) and *resource-constrained* (RC) interleaved SC polar decoders are proposed. Analysis shows that the TC interleaved decoders can multiply the throughput and achieve much higher utilization. Also, the RC interleaved decoders can improve the decoding throughput while keeping the hardware complexity low. Compared

with our pre-computation sequential polar decoder design, the RC 2-interleaved decoder given here can achieve 200% throughput with only 50% hardware consumption.

Finally, the decoder design issue of the newly proposed *simplified* SC (SSC) decoding algorithm for polar codes is investigated. Since the decoding latency for SSC algorithm changes with the choice of codes, a systematic way to determine the decoding latency is derived. By following a simple equation, we can calculate the decoding latency for any given polar code easily. A formal DFG-based design flow for the SSC decoder architecture is developed also. Furthermore, in order to always achieve a lower decoding latency than previous works, a novel pre-computation SSC decoder architecture is also proposed. A (1024, 512) decoder example is employed to demonstrated the advantages of the proposed approaches.

## **Table of Contents**

| Acknowled   | dgements                                             | i |

|-------------|------------------------------------------------------|---|

| Abstract    | i                                                    | i |

| Table of C  | Contents                                             | V |

| List of Tal | oles                                                 | X |

| List of Fig | uresxi                                               | i |

| Chapter 1   | Introduction                                         | 1 |

| 1.1 Int     | roduction                                            | 1 |

| 1.2 Su      | mmary of Contributions                               | 5 |

| 1.2.1       | Non-Binary QC-LDPC Decoders with Efficient Networks  | 5 |

| 1.2.2       | Low-Latency Successive Cancellation Polar Decoders   | 6 |

| 1.2.3       | Simplified SC Polar Decoder Architecture             | 8 |

| 1.3 Ou      | tline of the Thesis                                  | 8 |

| Chapter 2   | Non-Binary LDPC Decoders with Efficient Networks10   | 0 |

| 2.1 Int     | roduction10                                          | O |

| 2.1.1       | Construction Method of Class-I Codes                 | 1 |

| 2.1.2       | Construction Method of Class-II Codes                | 2 |

| 2.2 Pri     | or Works on Non-Binary LDPC Decoders                 | 2 |

| 2.2.1       | Decoding Algorithms for Non-Binary LDPC Codes        | 2 |

| 2.2.2       | Existing Non-Binary LDPC Decoder Architectures       | 3 |

| 2.3 Ge      | ometry Properties of Non-Binary QC-LDPC Codes14      | 4 |

| 2.3.1       | Shifting Properties of Class-I Codes                 | 5 |

| 2.3.2       | Symmetry Properties of Class-II Codes                | 5 |

| 2.4 Lay     | yer Partition Choice for Layered Decoding Algorithm2 | 1 |

| 2.    | 4.1   | Review of Layered Decoding Algorithm                  | 21 |

|-------|-------|-------------------------------------------------------|----|

| 2.    | 4.2   | Layer Partition and Related Decoding Performances     | 22 |

| 2.5   | ΑF    | Reduced-Complexity Decoder Architecture               | 23 |

| 2.    | 5.1   | Overall Architecture of Reduced-Complexity Decoder    | 24 |

| 2.    | 5.2   | Algorithm for Generating Local Switch Network of VNUs | 25 |

| 2.    | 5.3   | Architectures of VNUs' Local Switch Network           | 30 |

| 2.    | 5.4   | Hardware Architectures of VNU Block                   | 33 |

| 2.    | 5.5   | Hardware Architectures of CNU Block                   | 34 |

| 2.6   | Cor   | nparison with Prior Decoder Designs                   | 40 |

| 2.7   | Cor   | nclusion                                              | 45 |

| Chapt | ter 3 | Low-Latency Sequential SC Polar Decoder               | 46 |

| 3.1   | Intr  | oduction                                              | 46 |

| 3.    | 1.1   | SC Decoding Algorithm                                 | 48 |

| 3.    | 1.2   | SC Decoding Algorithm in Logarithm Domain             | 50 |

| 3.    | 1.3   | Min-Sum SC Decoding Algorithm                         | 51 |

| 3.2   | Prio  | or Works on SC Polar Decoder Designs                  | 52 |

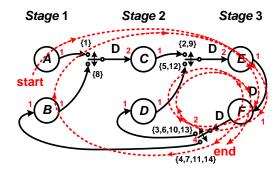

| 3.3   | DF    | G Analysis of the SC Polar Decoder                    | 54 |

| 3.    | 3.1   | DFG Construction for the SC Polar Decoder             | 54 |

| 3.    | 3.2   | DFG with Pre-Computation Look-Ahead Techniques        | 58 |

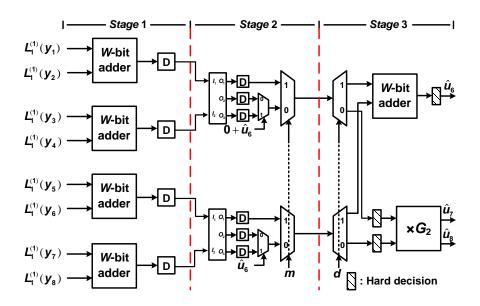

| 3.4   | Pip   | elined Tree Decoder Architecture                      | 60 |

| 3.    | 4.1   | Complete SC Tree Decoder Architecture Design          | 60 |

| 3.    | 4.2   | Architecture of Type I PE                             | 61 |

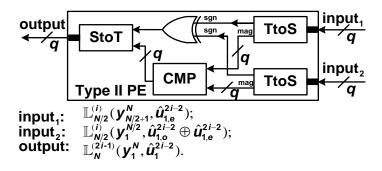

| 3.    | 4.3   | Architecture of Type II PE                            | 62 |

| 3.    | 4.4   | Architecture of the Feedback Part                     | 63 |

| 3.    | 4.5  | Selecting Signals for De-/Multiplexers                  | 67  |

|-------|------|---------------------------------------------------------|-----|

| 3.5   | Pre  | -Computation Look-Ahead Sequential Decoder              | 69  |

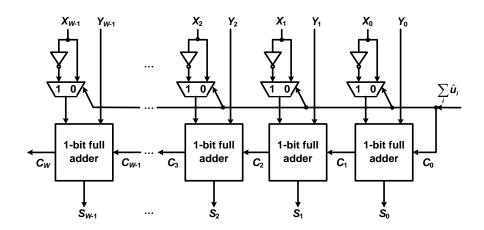

| 3.    | 5.1  | Architecture of the Revised Type I PE                   | 70  |

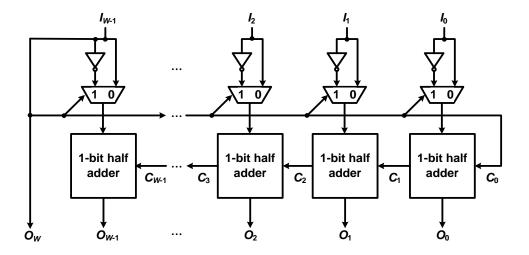

| 3.    | 5.2  | Architecture of the Merged PE                           | 73  |

| 3.    | 5.3  | Decoder Architecture Construction                       | 74  |

| 3.    | 5.4  | Architecture of the Revised Feedback Part               | 75  |

| 3.6   | Co   | mparison of Latency and Hardware                        | 78  |

| 3.7   | Cor  | nclusion                                                | 81  |

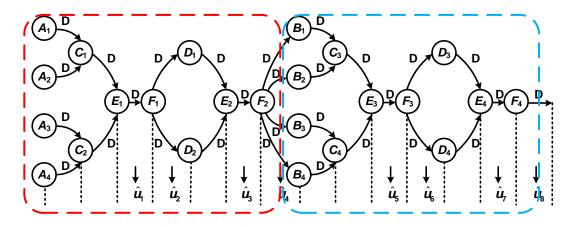

| Chapt | er 4 | High-Throughput Interleaved SC Polar Decoders           | 82  |

| 4.1   | Intı | oduction                                                | 82  |

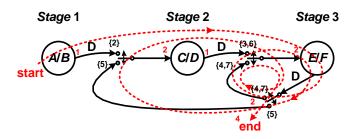

| 4.2   | 3-C  | Overlapped SC Polar Decoder Example                     | 84  |

| 4.    | 2.1  | 3-Overlapped Decoding Schedule                          | 84  |

| 4.    | 2.2  | 3-Overlapped SC Decoder Architecture                    | 85  |

| 4.3   | Pro  | perties of Overlapped SC Decoder Architectures          | 86  |

| 4.4   | The  | e Construction Approach with Folding Technique          | 91  |

| 4.    | 4.1  | Preliminaries of Folding Transformation Technique       | 92  |

| 4.    | 4.2  | Previous Decoders with Folding Transformation Technique | 93  |

| 4.5   | The  | e Parallel Pre-Computation Look-Ahead Decoder           | 96  |

| 4.6   | Co   | mparison with Other Works                               | 102 |

| 4.7   | Coı  | nclusion                                                | 105 |

| Chapt | er 5 | Design of Simplified SC Polar Decoders                  | 106 |

| 5.1   | Inti | oduction                                                | 106 |

| 5.2   | Rev  | view of the SSC Algorithm                               | 108 |

| 5.    | 2.1  | Tree Representation of the SC Decoding Algorithm        | 108 |

| 5.2.2                                                                | The SSC Decoding Algorithm                                                                                                                                                                          | 111       |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 5.3 T                                                                | ne Latency Analysis of the SSC Decoder                                                                                                                                                              | 113       |

| 5.3.1                                                                | A Simple Example                                                                                                                                                                                    | 113       |

| 5.3.2                                                                | Latency Analysis for the General Code Length                                                                                                                                                        | 116       |

| 5.4 P                                                                | oposed SSC Decoder Architecture                                                                                                                                                                     | 119       |

| 5.4.1                                                                | DFG Analysis of the SSC Decoding Process                                                                                                                                                            | 119       |

| 5.4.2                                                                | The SSC Decoder Architecture Design                                                                                                                                                                 | 119       |

| 5.5 P                                                                | re-Computation Look-Ahead SSC Polar Decoder                                                                                                                                                         | 122       |

| 5.5.1                                                                | Look-Ahead SSC Polar Decoder Architecture                                                                                                                                                           | 122       |

| 5.5.2                                                                | Latency of the Look-Ahead SSC Polar Decoder                                                                                                                                                         | 123       |

| 5.6 L                                                                | atency and Complexity Comparison                                                                                                                                                                    | 125       |

| 5.7 C                                                                | onclusion                                                                                                                                                                                           | 127       |

|                                                                      |                                                                                                                                                                                                     |           |

| Chapter                                                              | 6 Conclusions and Future Research Directions                                                                                                                                                        |           |

| _                                                                    |                                                                                                                                                                                                     | 129       |

| _                                                                    | 6 Conclusions and Future Research Directions                                                                                                                                                        | 129       |

| 6.1 C                                                                | 6 Conclusions and Future Research Directions                                                                                                                                                        | 129129130 |

| 6.1 C<br>6.1.1                                                       | 6 Conclusions and Future Research Directions onclusions Non-Binary LDPC Decoders with Efficient Networks                                                                                            |           |

| 6.1 C<br>6.1.1<br>6.1.2                                              | Onclusions and Future Research Directions  Onclusions  Non-Binary LDPC Decoders with Efficient Networks  Low-Latency Sequential SC Polar Decoder                                                    |           |

| 6.1 C<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                            | 6 Conclusions and Future Research Directions  Onclusions  Non-Binary LDPC Decoders with Efficient Networks  Low-Latency Sequential SC Polar Decoder  High-Throughput SC Polar Decoder Architectures |           |

| 6.1 C<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                            | 6 Conclusions and Future Research Directions                                                                                                                                                        |           |

| 6.1 C<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.2 F                   | 6 Conclusions and Future Research Directions                                                                                                                                                        |           |

| 6.1 C<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.2 F<br>6.2.1          | 6 Conclusions and Future Research Directions                                                                                                                                                        |           |

| 6.1 C<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.2 F<br>6.2.1<br>6.2.2 | 6 Conclusions and Future Research Directions                                                                                                                                                        |           |

| Bibliography | <br>13 | 7 |

|--------------|--------|---|

| DIDITUSIUPIL | <br>-  | • |

## **List of Tables**

| Table 2.1 | Proposed surjective function example for $F'_t$                        | 18             |

|-----------|------------------------------------------------------------------------|----------------|

| Table 2.2 | Comparisons for different non-binary QC-LDPC code decoders             | 11             |

| Table 3.1 | Decoding schedule for 8-bit SC decoder.                                | 57             |

| Table 3.2 | 8-bit pre-computation look-ahead decoding schedule                     | 59             |

| Table 3.3 | Calculation of switching time for $m_n$ .                              | 58             |

| Table 3.4 | Select signals for 8-bit decoder example.                              | 59             |

| Table 3.5 | Truth table of both full adder and subtractor.                         | 71             |

| Table 3.6 | Revised calculation of switching time for $m_n$ .                      | 76             |

| Table 3.7 | Comparison for different polar decoder architectures.                  | 79             |

| Table 4.1 | The TC 3-interleaved decoding schedule for 8-bit decoder               | 34             |

| Table 4.2 | The TC 1-, 3-, and 7-interleaved decoding schedule for 8-bit decoder 8 | 38             |

| Table 4.3 | The TC 3-, 5-, and 7-interleaved decoding schedule for 8-bit decoder 9 | <del>)</del> 0 |

| Table 4.4 | Number of active <i>merged</i> PEs for the original decoder            | €7             |

| Table 4.5 | Control signals for the RC 2-interleaved decoder.                      | 98             |

| Table 4.6 | Number of active <i>merged</i> PEs for RC 2-interleaved decoder        | )()            |

| Table 4.7 | Number of active <i>merged</i> PEs for RC 3-interleaved decoder        | )2             |

| Table 4.8 | Comparison between the two proposed works and others 10                | )3             |

| Table 4.9 | The TC 2-interleaved decoding schedule for 8-bit decoder               | )4             |

| Table 5.1 | The SSC decoding schedule for the (8, 3) polar decoder                 | 16             |

| Table 5.2 | The SSC decoding schedule for the (8, 5) polar decoder                 | 18             |

| Table 5.3 | Pre-computation schedule for the (8, 3) decoder                        | 22             |

| Table 5.4 | Pre-computation schedule for the (8, 5) decoder                        | 24             |

| Table 5.5 | Comparison between the proposed SSC decoders and others                | 26             |

## **List of Figures**

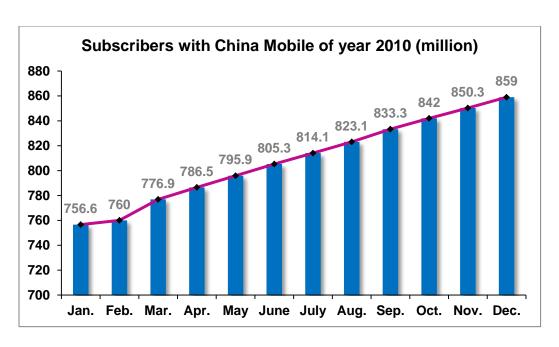

| Figure 1.1 Subscribers with China Mobile of the year 2010 [2]                    |

|----------------------------------------------------------------------------------|

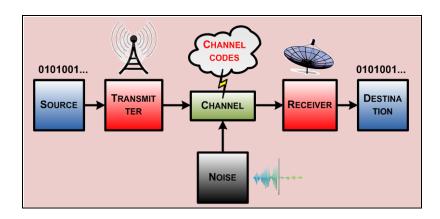

| Figure 1.2 Simple block diagram of modern communication systems                  |

| Figure 2.1 Performances of codes with different surjective functions             |

| Figure 2.2 PER comparisons between different algorithms for a Class-I code 23    |

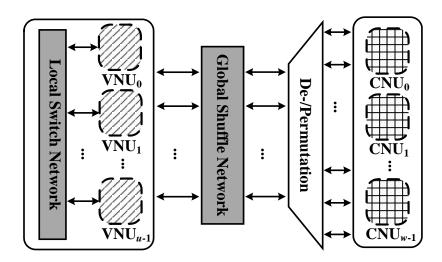

| Figure 2.3 Block diagram of proposed layered non-binary QC-LDPC decoder 24       |

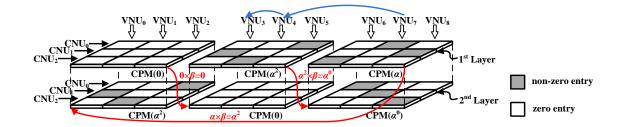

| Figure 2.4 Layered decoding example of the 4-ary (9, 3) rate-1/3 Class-I code 28 |

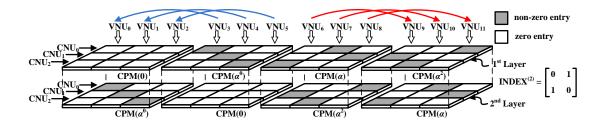

| Figure 2.5 Layered decoding example of the 4-ary (12, 6) rate-½ Class-II code 30 |

| Figure 2.6 Local switch network of Class-I codes case                            |

| Figure 2.7 Local switch network of the Class-II code defined by Eq. (2-15) 32    |

| Figure 2.8 Hardware implementation of the variable node unit (VNU)               |

| Figure 2.9 Internal structure of generator for possible solution sequences       |

| Figure 2.10 Data sorter structure with length of $n_m$                           |

| Figure 2.11 Proposed CNU block architecture employing data sorter                |

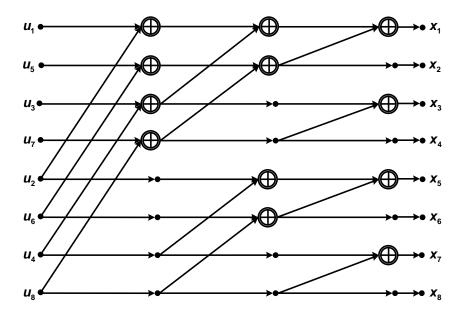

| Figure 3.1 Channel polarization for binary erasure channel (BEC) of rate 0.5 47  |

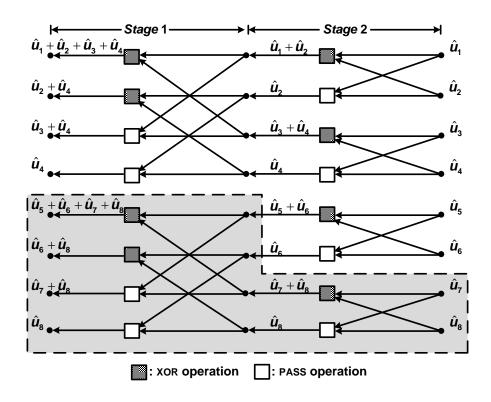

| Figure 3.2 Encoding operation of the 8-bit polar code [28]                       |

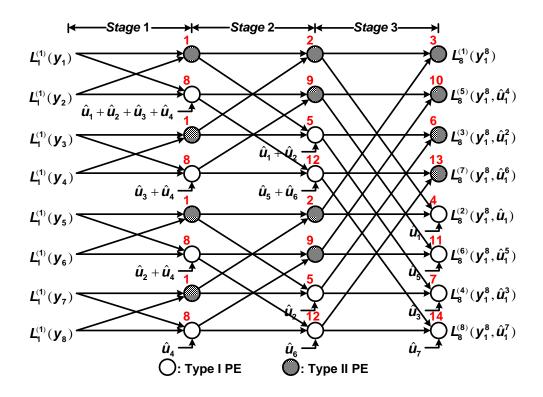

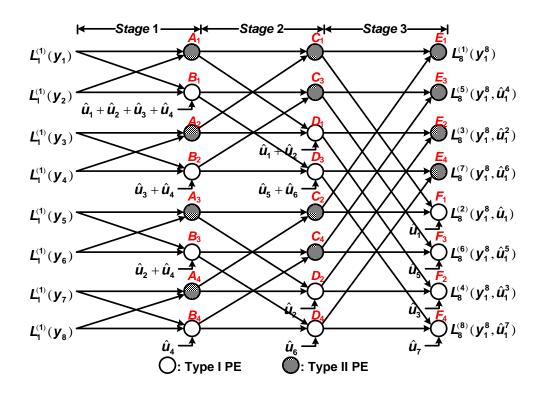

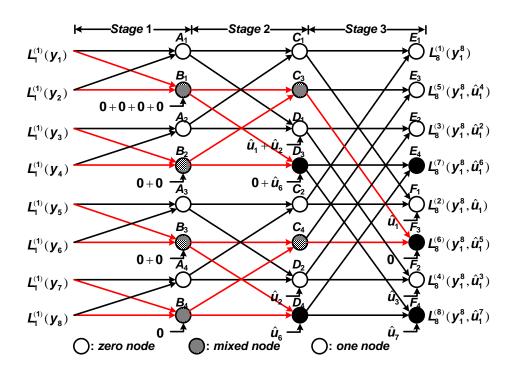

| Figure 3.3 SC decoding process of polar codes with length $N = 8$                |

| Figure 3.4 SC decoding process with new labels                                   |

| Figure 3.5 DFG for the 8-bit SC decoding process                                 |

| Figure 3.6 Simplified DFG for 8-bit SC decoding process                          |

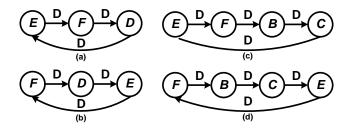

| Figure 3.7 Four loops of the simplified DFG                                      |

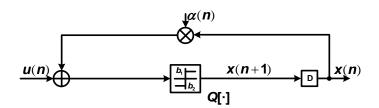

| Figure 3.8 A quantizer example for pre-computation look-ahead approach [99] 58   |

| Figure 3.9 DFG for 8-bit pre-computation look-ahead SC decoding process 59       |

| Figure 3.10 The 8-bit conventional tree decoder architecture                     |

| Figure 3.11  | Proposed Type I PE architecture.                                    | 61   |

|--------------|---------------------------------------------------------------------|------|

| Figure 3.12  | Proposed architecture of Type II PE.                                | 62   |

| Figure 3.13  | Proposed structure of the <i>TtoS</i> block                         | 62   |

| Figure 3.14  | Flow graph of feedback part for 8-point polar decoder               | 63   |

| Figure 3.15  | Simplified flow graph of the proposed feedback part                 | 65   |

| Figure 3.16  | Pipelined feed-forward architecture for 8-bit feedback part         | 66   |

| Figure 3.17  | The 2-parallel version of the architecture in Figure 3.16           | 66   |

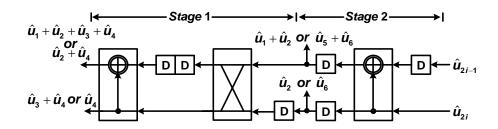

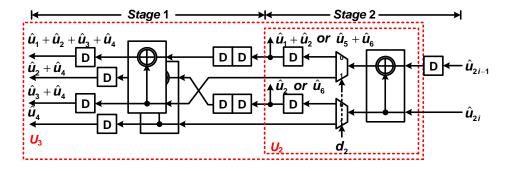

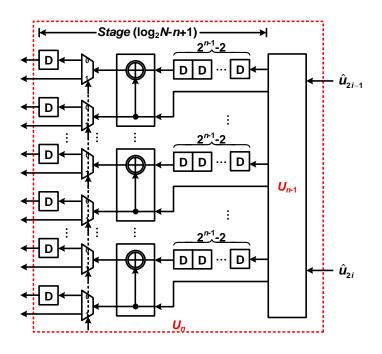

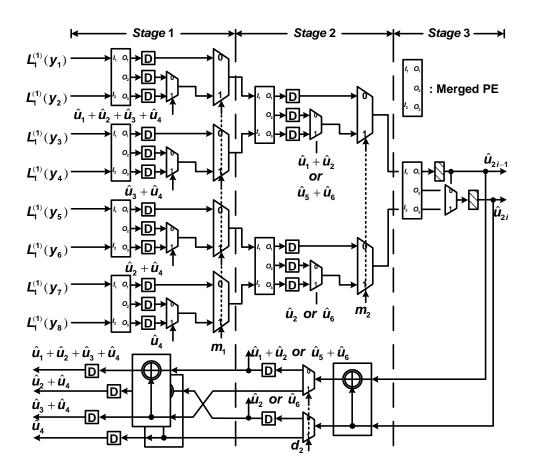

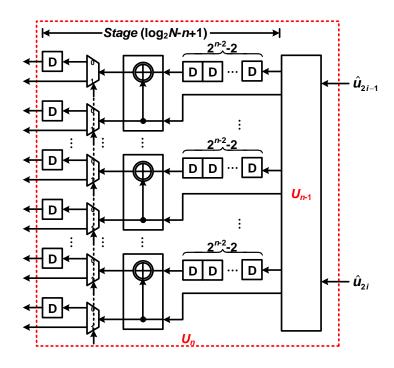

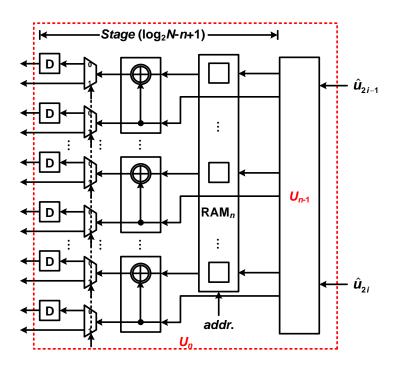

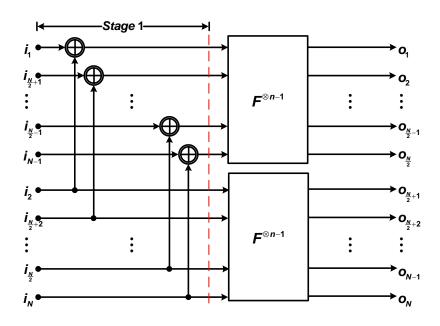

| Figure 3.18  | Recursive construction of $U_n$ based on $U_{n-1}$ .                | 67   |

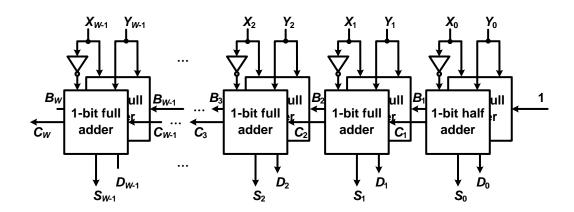

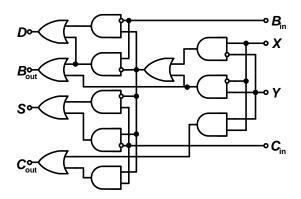

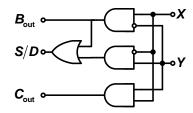

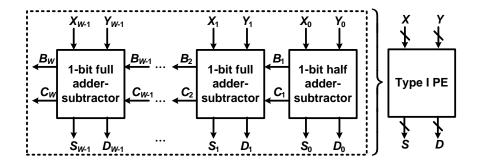

| Figure 3.19  | The W-bit parallel adder-subtractor architecture                    | 70   |

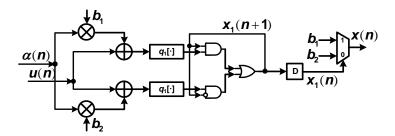

| Figure 3.20  | Proposed 1-bit parallel adder-subtractor architectures              | 72   |

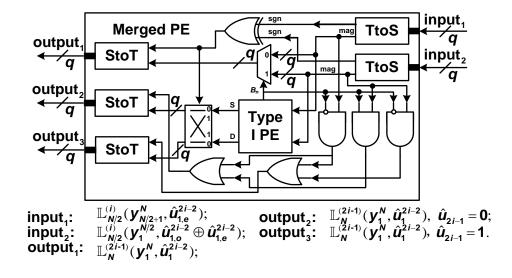

| Figure 3.21  | The revised Type I PE architecture.                                 | 73   |

| Figure 3.22  | Proposed structure of the <i>merged</i> PE.                         | 73   |

| Figure 3.23  | 8-bit pre-computation look-ahead polar decoder architecture         | 75   |

| Figure 3.24  | Revised recursive construction of $U_n$ based on $U_{n-1}$          | 76   |

| Figure 3.25  | Revised recursive construction of $U_n$ using the memory bank       | . 77 |

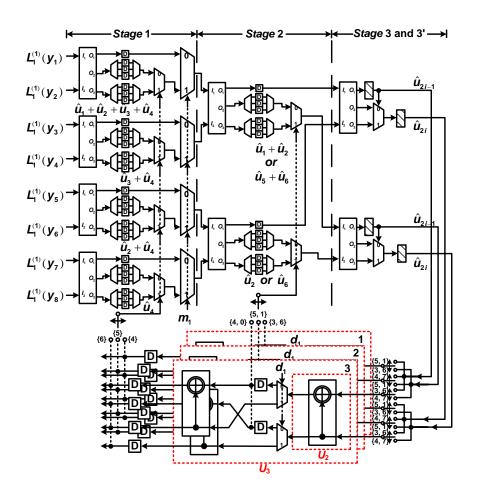

| Figure 4.1   | The 8-bit TC 3-interleaved SC polar decoder                         | 85   |

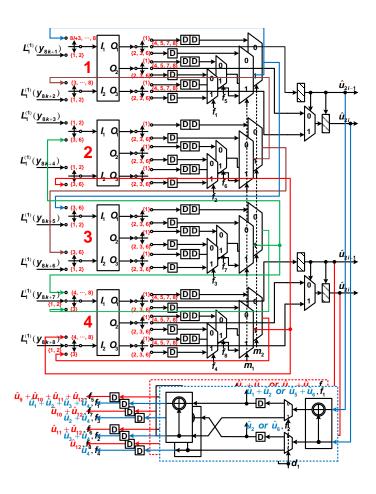

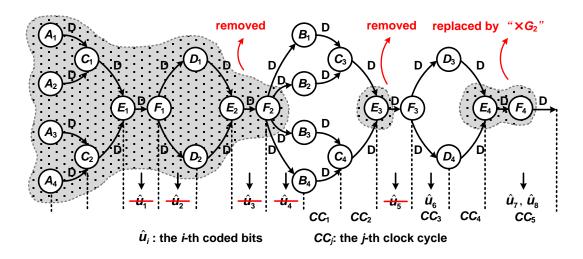

| Figure 4.2   | The RC 2-interleaved architecture for 8-bit polar decoder           | 99   |

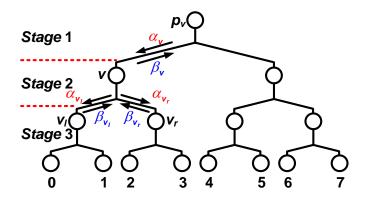

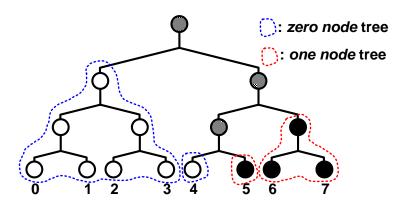

| Figure 5.1   | Γree representation of the 8-bit SC polar decoder                   | 108  |

| Figure 5.2 I | Decoding process of the 8-bit SC decoder with tree representation 1 | 110  |

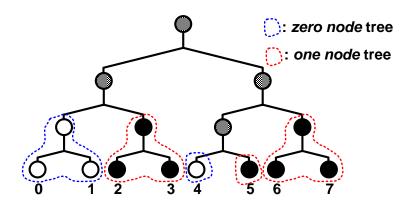

| Figure 5.3   | The revised tree representation of the 8-bit SC polar decoder       | 112  |

| Figure 5.4   | Conventional SC decoding process.                                   | 113  |

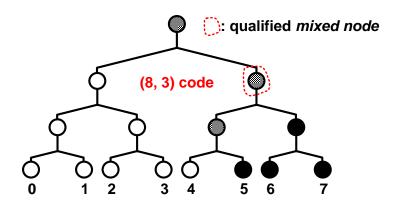

| Figure 5.5   | SSC decoding process of the (8, 3) polar code                       | 114  |

| Figure 5.6 1 | Nodes categorization with circled binary trees                      | 115  |

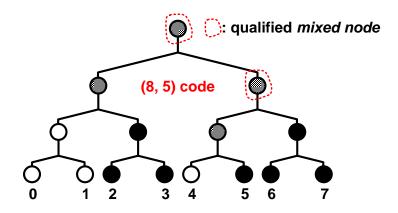

| Figure 5.7   | Sub-trees identification for an (8, 5) code example                 | 118  |

| Figure 5.8 The DFG for the SSC decoding approach.                                | 119 |

|----------------------------------------------------------------------------------|-----|

| Figure 5.9 The SSC decoder architecture for the (8, 3) codes                     | 120 |

| Figure 5.10 The fully-pipelined implementation for $F^{\otimes 3}$               | 121 |

| Figure 5.11 Recursive construction of the fully-pipelined implementation         | 121 |

| Figure 5.12 Pre-computation SSC decoder architecture for the (8, 3) polar codes. | 123 |

| Figure 5.13 The qualified <i>mixed node</i> for the (8, 3) code                  | 124 |

| Figure 5.14 The qualified <i>mixed node</i> for the (8, 5) code                  | 125 |

## Chapter 1

### Introduction

#### 1.1 Introduction

Along with the emergence and rapid development of modern communication technologies, people's lives have been enormously changed by a list of new concepts such as streaming media, cloud storage, smart phone, and so on. The corresponding markets are huge and of great potential. Take the mobile phone market as an example. China Mobile is the world's largest individual mobile operator by subscribers [1]. Illustrated in Figure 1.1, China Mobile has over 859 million mobile phone subscribers by the end of the year 2010 [2]. By the end of 2009, more than 50 mobile operators have over 10 million subscribers each. And more than 150 operators had at least one million subscribers [2]. Not only the number of subscribers has expanded drastically, the data transmission rate of a single mobile phone has increased a lot. The data-optimized 4th-generation technologies such as the WiMAX standard [3] and the LTE standard [4] can achieve up to 10-fold speed improvements over 3G technologies [5]. And still researchers are now working towards the 5G systems [6], which would like to be implemented around the year 2020 [7]. Therefore, it becomes very challenging for modern communication systems to handle those increasing heavy tasks.

Figure 1.1 Subscribers with China Mobile of the year 2010 [2].

As illustrated in Figure 1.2, any modern communication system can be decomposed into five parts, which are the source, the transmitter, the noisy channel, the receiver, and the destination [8]. In order to protect the data transmitted over channels, we need to effectively suppress the influence of the noise. Therefore, channel codes are always of high necessity [9, 10]. Ever since the notation of channel capacity was defined by Claude E. Shannon during World War II [11], channel codes have experienced a rapid development [12]. From Gray codes [13], we had at the very beginning, nowadays we have much more choices: Hamming codes [14], Reed-Solomon (RS) codes [15], Bose-Chaudhuri-Hocquenghem (BCH) codes [16, 17], Turbo codes [18], fountain codes [19], and low-density parity-check (LDPC) codes [20]. The history of channel codes is actually the annals of modern communication systems' development. This reminds us of the emergence of Turbo codes, LDPC codes, and the iterative decoding methodology in 1990's. These channel coding techniques have promoted the growth of modern communication systems such as 10 Giga-bit/s Ethernet [21], Digital video broadcasting [22], Wi-Fi [23], and 3G wireless communications [5]. On the other hand, the always-

existing pressing need to develop "the next generation" communication systems drives the development of channel codes move forward. Now, we are at the new turn again. Here comes the first question: what error channel codes can we expect for the next generation modern communication systems?

Figure 1.2 Simple block diagram of modern communication systems.

Aside from the issue of developing new channel codes, the efficient implementation of corresponding decoders is of equal importance [24]. For modern communication systems, to fulfill the long-distance high-quality information exchanges among a large number of people, the corresponding decoders for channel codes are required to be fast, portable, reliable, and safe [25]. This means that the channel decoder implementation should be low-latency, low-complexity, low-error rate, and wiretap-free. Therefore, the second question is: can we design low-complexity low-latency channel decoders to meet the requirements of modern communication systems?

In order to answer the first question, recently two kinds of error correction codes have been proposed by the coding society, which are non-binary LDPC codes [26, 27] and polar codes [28-34], respectively. Compared with their binary counterparts, non-binary LDPC codes are defined over finite field GF(q) with q>2. Previous literatures such as [26] have shown that non-binary LDPC codes can show better decoding performance over

their binary counterparts with proper encoding approaches and code lengths. This advantage makes the non-binary LDPC codes very attractive for real-time applications. However, the straightforward implementation of non-binary LDPC decoders results in the computation complexity of  $(q^2)$ . This high hardware complexity makes it difficult to adopt non-binary LDPC codes for modern communication applications. Therefore, further methodologies which can reduce the complexity of non-binary LDPC decoders to an acceptable level are in need. For polar codes, now they are considered as the most favorable capacity-approaching channel codes due to the low encoding complexity and good secrecy [35]. But the disadvantage is also obvious. Since the successive cancellation (SC) polar decoders are only able to produce decoded bits in a serial manner, the corresponding decoding latency turns out to be 2(N-1) clock cycles, where N is the length of the codeword [36]. Considering N is always set to be greater than  $2^{10}$  [28], the resulting latency becomes impractical. How to design low-latency low-complexity SC polar decoder is still challenging.

VLSI digital signal processing (DSP) design techniques can be widely applied to the implementation of different application scenarios [37]. We believe that with proper VLSI DSP design techniques, practical decoder designs for modern communication systems can be obtained. This thesis is devoted to developing design methodologies for feasible low-complexity low-latency channel decoders in modern communication systems, especially on non-binary LDPC decoders and SC polar decoders. Our contributions are listed in the next section as follows.

#### 1.2 Summary of Contributions

#### 1.2.1 Non-Binary QC-LDPC Decoders with Efficient Networks

As mentioned in Section 1.1, non-binary LDPC codes are of great interest due to their better performance over binary ones when the code length is moderate. However, the cost of decoder implementation for these non-binary LDPC codes is still very high [27]. Generally speaking, the hardware consumption for an LDPC decoder usually comes from two parts: the processing units, which include both the check node units (CNUs) and the variable node units (VNUs), and the switch networks connecting those processing units. Previous literatures [38-44] mainly focused on the low-complexity design of processing units, especially on the hardware-efficient implementation of CNUs. However, the methodologies on how to reduce the complexity of switch networks have not been well addressed yet.

We have proposed a low-complexity VLSI architecture for non-binary LDPC decoders [45]. It should be mentioned that the specific non-binary LDPC codes we are dealing with are called non-binary quasi-cyclic LDPC (QC-LDPC) codes [46-56]. Like their binary counterparts, non-binary QC-LDPC codes are hardware-friendly and can also achieve promising decoding performance. According to Figure 2 of [49], with 50 decoding iterations, the 64-ary (1260, 630) non-binary QC-LDPC code can attain 3.78 dB code gain over the (1260, 630, 631) shortened RS code.

The non-binary QC-LDPC codes introduced in [49] can be categorized into to families. The first one is called Class-I non-binary QC-LDPC codes or Class-I codes for short. Their algebraic construction is mainly based on cyclic subgroups of the multiplicative group of GF(q). The other family is named as Class-II non-binary QC-LDPC codes or Class-II codes for short. Their construction is similar to the first one but

based on additive subgroups of the finite field. We will show that by exploiting the intrinsic shifting and symmetry properties of non-binary QC-LDPC codes, significant reduction of memory size and routing complexity can be achieved. These unique features directly lead to two different network-efficient decoder architectures for Class-I and Class-II codes, respectively.

Comparison results with the state-of-the-art designs show that for the code example of the 64-ary (1260, 630) rate-0.5 Class-I code, the proposed scheme can save up to 70.6% hardware required by the switch network, which demonstrates the efficiency of the proposed design methodology. The proposed design for the 32-ary (992, 496) rate-0.5 Class-II code can achieve a 93.8% switch network complexity reduction compared with conventional approaches. Those comparison results have demonstrated that the proposed approaches are feasible and efficient.

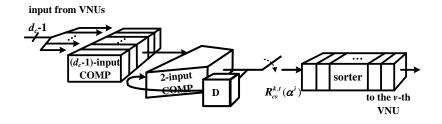

Furthermore, we also try to reduce the hardware complexity of the CNUs. With the help of a generator for possible solution sequences, both forward and backward steps can be eliminated to offer processing convenience of the CNU blocks. Results show that the proposed 32-ary (992, 496) rate-0.5 Class-II decoder can achieve 4.47 Mb/s decoding throughput.

#### 1.2.2 Low-Latency Successive Cancellation Polar Decoders

Polar codes have recently emerged as one of the most favorable capacity-achieving error correction codes due to their low encoding and decoding complexity [28]. Polar codes are constructed with a method called channel polarization to achieve the symmetric capacity of any given binary-input discrete memoryless channel (B-DMC). It has been reported that polar codes under list decoding with CRC are competitive with the best LDPC codes at lengths as short as  $N = 2^{11}$  [57].

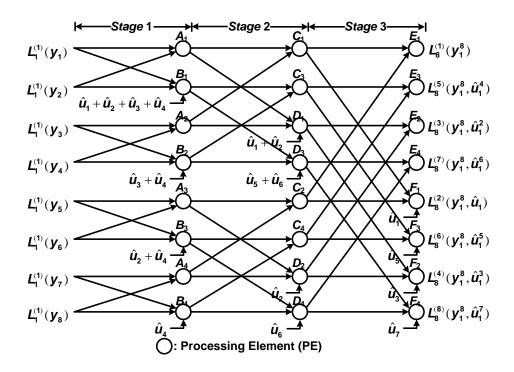

However, because of the large code length required by practical applications ( $N \ge 2^{10}$ ), the few existing SC decoder implementations still suffer from not only high hardware cost but also long decoding latency. Therefore, SC polar decoders with less decoding latency are required by modern communication systems. In this thesis, a data-flow graph (DFG) for the SC decoder is derived. Based on the DFG analysis, a family of low-latency SC polar decoders is derived formally [36, 58].

#### **Low-Latency Sequential SC Polar Decoder**

According to the DFG analysis, a low-latency sequential SC polar decoder architecture is proposed to reduce the achievable minimum decoding latency. Pre-computation lookahead techniques are employed to halve the latency. The *feedback part* is presented for the first time. Sub-structure sharing is used to design a *merged* processing element (PE) for higher hardware utilization.

#### TC Interleaved SC Polar Decoder

In order to meet throughput requirements for a diverse set of application scenarios, a systematic approach to construct different TC interleaved SC polar decoder architectures is also presented. Compared with the conventional N-bit tree SC decoder, the proposed TC interleaved architectures can achieve as high as (N-1) times speedup with only 50% decoding latency and  $(N\cdot\log_2N)/2$  merged PEs.

#### **RC 2-Interleaved SC Polar Decoder**

Another approach to meet the high-speed requirements for modern communication system applications is introducing RC interleaved processing. However, the design of an RC interleaved SC decoder is challenging due to the inherent serial decoding schedule. Straightforward RC interleaved designs usually introduce significant decoding latency

overhead. To this end, in this paper a low-latency low-complexity RC 2-interleaved SC decoder is proposed with the folding technique [59]. Compared with similar designs in previous literatures, the proposed design can achieve 4 times speed-up while only consumes similar hardware.

#### 1.2.3 Simplified SC Polar Decoder Architecture

Although the low-latency SC polar decoder family could reduce the latency by 50%, we believe that we do better. Recently, a low-latency decoding scheme referred as the *simplified* successive cancellation (SSC) algorithm has been proposed for the decoding of polar codes [60]. It is claimed that significant latency reduction is achieved over a wide range of code rates. However, since this approach highly depends on the specific code it is dealing with, the corresponding latency is not easy to predict.

In this thesis, we present the first systematic approach to formally derive the SSC decoding latency for any given polar code [61]. The method to derive various SSC polar decoder architectures for any specific code is also presented. Moreover, it is shown that with the pre-computation technique, the decoding latency can be further reduced. Similarly, the latency-reduced SSC decoder's latency can also be calculated with a simple equation. Compared with the state-of-the-art SC decoder designs, the two SSC polar decoders can save up to 39.6% decoding latency with the same hardware cost.

#### 1.3 Outline of the Thesis

The thesis is organized as follows. Chapter 2 gives a brief review of non-binary QC-LDPC codes. Based on the geometry properties of Class-II and Class-II codes, two different switch networks are proposed. A generator for possible solution sequences is also introduced to further reduce the complexity of CNUs.

Chapter 3 introduces the design of low-latency sequential SC polar decoder. The DFG of SC decoding process is proposed for the first time. Then the novel precomputation look-ahead SC decoder architecture is described in detail.

Chapter 4 presents two kinds of SC polar decoder architectures towards high-speed applications. First, a systematic methodology for designing the TC interleaved SC polar decoders is described. Afterwards, the RC 2-interleaved SC polar decoder architecture is constructed based on the folding technique.

Chapter 5 proposes a method to determine the decoding latency of SSC algorithm. A design approach for corresponding SSC polar decoder is given also.

Finally, Chapter 6 summarized of the contribution of the entire thesis and provides future research directions.

## Chapter 2

# Non-Binary LDPC Decoders with Efficient Networks

In this chapter, we present two network-efficient decoder architectures for non-binary QC-LDPC codes [45]. Section 2.1 provides a brief introduction of non-binary LDPC codes and their sub-class, non-binary QC-LDPC codes. Section 2.2 briefly reviews prior works on non-binary LDPC decoder designs. Section 2.3 investigates the geometry properties of both Class-I and Class-II codes. Decoding schemes with different choices of layers are evaluated in Section 2.4. Section 2.5 presents message passing schedules via proposed networks and corresponding low complexity non-binary QC-LDPC decoder architectures. The hardware cost estimations and comparisons are presented in Section 2.6. Section 2.7 concludes this chapter finally.

#### 2.1 Introduction

Rediscovered by MacKay [62], binary LDPC codes have shown near-Shannon limit performance [22, 63-66]. They have been extensively adopted in next-generation communication system standards. Recently, LDPC codes over GF(q) with q>2 are

reported to show even better decoding performance over the binary ones [26] when encoding approach and code length are proper. However, the introduced high decoding complexity is also significant.

To this end, a sub-class of non-binary LDPC codes is proposed in [46-55]. Non-binary QC-LDPC codes are architecture-aware and can achieve good performance. In [49], two algebraic construction methods based on *array dispersions* of matrices over non-binary subgroups are presented and referred as Class-I and Class-II, respectively.

#### 2.1.1 Construction Method of Class-I Codes

Assume the *Galois* field GF(q) has a primitive element  $\alpha$ . In this case, elements within GF(q) can be represented by powers of the primitive element  $\alpha$ :  $\alpha^{-\infty} = 0$ ,  $\alpha^0 = 1$ ,  $\alpha^1$ , ...,  $\alpha^{q-2}$ . Define  $\mathbf{z}(\alpha^i) = (z_0, z_1, ..., z_{q-2})$  as a (q-1)-ary location-vector. Here the i-th component  $z_i = \alpha^i$ , and all the other ones are 0's. Specially,  $\mathbf{z}(0)$  is defined as the all-zero (q-1)-tuple. The *circulant permutation matrix* (CPM) of  $\delta$  is defined as  $(\mathbf{z}(\delta), \mathbf{z}(\alpha\delta), ..., \mathbf{z}(\alpha^{q-2}\delta))^T$ , where  $\delta$  can be any element in GF(q). The construction method of Class-I codes is described as follows:

#### Construction of Class-I Non-Binary QC-LDPC Codes

**1: Factorization:**  $q-1=c\times n, \gcd(c,n)=1$ ;

**2: Element definition:**  $\beta = \alpha^c$ ,  $\delta = \alpha^n$ ;

3: Subgroup expansion:

$$\begin{cases} G_1 = \{\beta^0 = 1, \beta, ..., \beta^{n-1}\}, \\ G_2 = \{\delta^0 = 1, \delta, ..., \delta^{c-1}\}; \end{cases}$$

4: Matrix formation:

$$\begin{cases} \mathbf{W}^{(1)} = [\mathbf{W}_{i,j}^{(1)}]_{0 \le i < c, 0 \le j < c}, \\ \mathbf{W}_{i,j}^{(1)} = [\delta^{j-i}\beta^k - \beta^l]_{0 \le k < n, 0 \le l < n}; \end{cases}$$

**5: Substitution:** Replace each entry of  $\mathbf{W}^{(1)}$  by its CPM

to get

$$\mathbf{A}^{(1)} = [\mathbf{A}_{i,j}^{(1)}]_{0 \le i,j < q}$$

;

**6: Truncation:**  $\mathbf{H}^{(1)} = \mathbf{A}^{(1)}(\gamma, \rho) = [\mathbf{A}_{i,j}^{(1)}]_{0 \le i < \gamma, 0 \le j < \rho};$

7: Output: H<sup>(1)</sup>.

#### 2.1.2 **Construction Method of Class-II Codes**

Using the additive subgroups instead of the cyclic ones, we have the construction method of Class-II codes as follows.

#### Construction of Class-II Non-Binary QC-LDPC Codes

- **1: Factorization:**  $q = 2^m$ ,  $c = 2^{m-t}$ , and  $n = 2^t$ ;

- 2: Elements definition:  $\begin{cases} f_t' = \{\alpha^0, \alpha^1, \dots, \alpha^{t-1}\}, \\ f_{m-t}'' = \{\alpha^t, \alpha^{t+1}, \dots, \alpha^{m-1}\}; \end{cases}$

- **5: Substitution:** Replace each entry of  $\mathbf{W}^{(2)}$  by its CPM

to get

$$\mathbf{A}^{(2)} = [\mathbf{A}_{i,j}^{(2)}]_{0 \le i,j < q}$$

;

- **6: Truncation:**  $\mathbf{H}^{(2)} = \mathbf{A}^{(2)}(\gamma, \rho) = [\mathbf{A}_{i,j}^{(2)}]_{0 \le i < \gamma, 0 \le j < \rho};$

- **7: Output: H**<sup>(2)</sup>.

#### 2.2 **Prior Works on Non-Binary LDPC Decoders**

Much research has been carried out on non-binary LDPC decoder designs. A brief review of previous works on non-binary LDPC decoding algorithms and decoder architectures is given as follows.

#### 2.2.1 **Decoding Algorithms for Non-Binary LDPC Codes**

The belief propagation (BP) algorithm is the locally optimal, yet the most complex, iterative decoding algorithm of non-binary LDPC codes. Because the size of messages is q, the straightforward implementation of BP algorithm has the complexity of  $(q^2)$ , which is very high for hardware designers. To this end, several revised decoding algorithms

have been proposed. The log-domain decoding scheme [67] is mathematically equivalent to the BP algorithm. It has shown advantages in both decoding complexity and numerical robustness. By employing a p-dimensional two-point fast Fourier transform (FFT), the computation complexity can be further reduced, where  $p = \log_2 q$ . However, the FFT algorithm is not suitable for the log domain. Then, a mixed-domain implementation has been presented in [68]. In this algorithm, FFT operation is carried out in real-domain. And the operations of CNU and VNU are carried out in log-domain. To implement the exponential and logarithm computations, the look-up table (LUT) is employed for the data conversion between log-domain and real-domain.

Unfortunately, for high-order field applications, all the above approaches are of limited interests. This is because the number of LUT accesses grows with a complexity of (*qp*) for a single message. To solve this problem, a complexity-reduced variant of the Min-Sum (MS) decoding, called Extended Min-Sum (EMS), was proposed in [27, 69, 70]. In this algorithm, the CNUs only deal with a *selective* part of the incoming messages. Moreover, some other low-complexity quasi-optimal iterative algorithms are proposed in [71]. The Min-Max algorithm is the most attractive one of them. It reduces the total number of operations with minimum decoding degradation.

#### 2.2.2 Existing Non-Binary LDPC Decoder Architectures

Although in the past few years, the research on binary LDPC decoder design has experienced a significant growth [72-74], very few publications on non-binary LDPC decoder implementations have appeared. A straightforward implementation of the EMS decoding algorithm was proposed in [41]. This is the first implementation of a non-binary LDPC decoder with  $q \ge 64$ . [68] presented a mixed-domain non-binary LDPC decoder for small codes. But the decoding throughput is only 1 Mb/s, which is not enough for modern communication systems. In [42-44], several non-binary QC-LDPC decoder architectures

using semi-parallel processing scheme are proposed. Another two efficient non-binary LDPC decoders have been proposed by [38] and [39]. Moreover, a flexible decoder which is suitable for both binary and non-binary LDPC codes has been given in [40]. However, all those architectures suffer from high-complexity networks. This is because they use either a bi-directional network or two full-size switch networks for shuffling and reshuffling messages.

In this chapter, we present novel non-binary LDPC decoder architectures with both high network efficiency and low hardware complexity. The layered decoding algorithm is employed for the proposed decoders. By investigating the geometry properties of the corresponding **H** matrices, two kinds of *local switch networks* for VNUs are introduced for Class-I and Class-II codes, respectively. The proposed decoders are memory efficient, highly parallel, and have low routing complexity. Comparison results have shown that 70.6% switch network hardware can be reduced compared with the state-of-the-art design for decoding Class-I codes. And 93.8% can be reduced for Class-II decoders. Finally, by uncovering the actual identity of parity check equations for different layers, low-complexity CNUs are implemented.

### 2.3 Geometry Properties of Non-Binary QC-LDPC Codes

The parity-check matrix of non-binary QC-LDPC codes is simply composed of square sub-matrices. [42-44] have addressed some straightforward properties of them. However, for more efficient decoder architectures, more thorough investigations on the geometry properties of the check matrix **H** are required now.

#### 2.3.1 Shifting Properties of Class-I Codes

According to the construction method of Class-I codes, the identity of  $\mathbf{W}_{i,j}^{(1)}$  and its neighbor  $\mathbf{W}_{(i-1)\bmod c,(j-1)\bmod c}^{(1)}$  can be verified by the following equation:

$$\mathbf{W}_{i,j}^{(1)} = [\delta^{j-i}\beta^k - \beta^l]$$

$$= [\delta^{((j-1)\bmod c) - ((i-1)\bmod c)}\beta^k - \beta^l]$$

$$= \mathbf{W}_{(i-1)\bmod c, (j-1)\bmod c}^{(1)}.$$

(2-1)

Therefore, each row of the base matrix  $\mathbf{W}^{(1)}$ , except for the first row, is the 1-step right cyclic-shift of the row above it. The first row is the 1-step right cyclic-shift of the last row.

Moreover, further exploitation of sub-matrix  $\mathbf{W}_{i,j}^{(1)}$  can show that similar permutation property holds at a lower level. Let  $\mathbf{w}_{(i,j)(k,l)}^{(1)}$  be the entry of sub-matrix  $\mathbf{W}_{i,j}^{(1)}$  located at the k-th row and l-th column. The property can be expressed as follows,

$$\mathbf{w}_{(i,j)(k,l)}^{(1)} = \delta^{j-i} \beta^{k} - \beta^{l}$$

$$= \beta (\delta^{j-i} \beta^{(k-1) \bmod n} - \beta^{(l-1) \bmod n})$$

$$= \beta \mathbf{w}_{(i,j)((k-1) \bmod n,(l-1) \bmod n}^{(1)}.$$

(2-2)

Note that except for the permutation operation, one multiplication with  $\beta$  is also required.

Combined with the definition of CPM, the geometry properties of Class-I codes can be summarized as follows:

**Proposition 1** The Class-I non-binary QC-LDPC codes satisfy the shifting properties at three different levels:

- 1. The *i*-th row of the base matrix  $\mathbf{W}^{(1)}$  is exactly the 1-step right cyclic-shift of the  $[(i-1) \mod c]$ -th row. Therefore,  $\mathbf{W}^{(1)}_{i,j} = \mathbf{W}^{(1)}_{(i-1) \mod c,(j-1) \mod c}$ ;

- 2. The k-th row of the sub-matrix  $\mathbf{W}_{i,j}^{(1)}$  is exactly the 1-step right cyclic-shift of the  $[(k-1) \mod n]$ -th row multiplied by  $\boldsymbol{\beta}$ , that is,  $\mathbf{w}_{(i,j)(k,l)}^{(1)} = \boldsymbol{\beta} \mathbf{w}_{(i,j)(k-1,l-1)}^{(1)}$ .;

3. The *m*-th row of the CPM corresponding to  $\mathbf{w}_{(i,j)(k,l)}^{(1)}$  is the 1-step right cyclic-shift of the  $[(m-1) \bmod n]$ -th row multiplied by  $\alpha$ , which is given by the definition of CPM.

Here is a simple example.  $GF(2^4)$  has minimal polynomial  $p(x) = 1 + x + x^4$ Following the construction steps, we can determine that  $\beta = \alpha^c = \alpha^3$  and  $\delta = \alpha^n = \alpha^5$ . Therefore, the sub-groups can be obtained as follows:

$$\begin{cases}

G_1 = \{\beta^0 = 1, \beta, ..., \beta^{n-1}\} = \{\alpha^0 = 1, \alpha^3, ..., \alpha^{12}\}, \\

G_2 = \{\delta^0 = 1, \delta, ..., \delta^{c-1}\} = \{\alpha^0 = 1, \alpha^5, ..., \alpha^{10}\}.

\end{cases}$$

(2-3)

Accordingly, a  $3\times3$  array of  $5\times5$  sub-matrices can be constructed. **Proposition 1.1** and **1.3** can be verified. Now we only check the validation of **Proposition 1.2**. For the entry  $\mathbf{W}_{0.0}^{(1)}$ , we can find out that **Proposition 1.1** holds:

$$\mathbf{W}_{0,0}^{(1)} = \begin{bmatrix} 0 & \alpha^{14} & \alpha^{13} & \alpha^{7} & \alpha^{11} \\ \alpha^{14} & 0 & \alpha^{2} & \alpha & \alpha^{10} \\ \alpha^{13} & \alpha^{2} & 0 & \alpha^{5} & \alpha^{4} \\ \alpha^{7} & \alpha & \alpha^{5} & 0 & \alpha^{8} \\ \alpha^{11} & \alpha^{10} & \alpha^{4} & \alpha^{8} & 0 \end{bmatrix}.$$

(2-4)

Here we have  $\mathbf{w}_{(0,0)(i,j)}^{(1)} = \alpha^3 \mathbf{w}_{(0,0)(i-1,j-1)}^{(1)} = \beta \mathbf{w}_{(0,0)(i-1,j-1)}^{(1)}$ .

#### 2.3.2 Symmetry Properties of Class-II Codes

Compared with the Class-I codes, uncovering geometry properties of Class-II codes is non-trivial. This is because the construction method of Class-II codes does not specify the exact surjective function from the elements of subgroups  $F'_t$  and  $F''_{m-t}$  to powers of  $\alpha$ .

Given this degree of design freedom, we develop one specific surjective function to construct Class-II codes with symmetry properties. Without loss of generality, the construction of subgroup  $F'_t$  is illustrated here as an example.

#### **Index Assignment of Surjective Function**

1: Suppose

$$\beta_i = \sum_{m=m_0}^{m_p} \alpha^m$$

,  $\beta_j = \sum_{n=n_0}^{n_q} \alpha^n$ , with  $0 \le m, n < t$ ;

2: if  $p < q$  then  $i < j$ ;

3: elseif  $p > q$  then  $i > j$ ;

4: else

5: for  $l = 0, l + +, l \le p$  do

6: if  $m_l < n_l$  then  $i < j$  break;

7: else  $m_l > n_l$  then  $i > j$  break;

8: endfor

9: endif

Table 2.1 denotes an example with t=4. Here the minimal polynomial is given as  $p(x)=1+x+x^4$ . Based on the construction steps, the subgroup  $F_t'$  is spanned by the t elements within the set of  $f_t'=\{\alpha^0,\alpha^1,\alpha^2,\alpha^3\}$ . According to the proposed surjective function, we can check that for any element  $\beta_i$  within sub-group  $F_t'$ , the following equation holds,

$$\beta_i + \beta_{(2^t - 1) - i} = \beta_{2^t - 1} \tag{2-5}$$

Similarly, for the other sub-group  $F''_{m-t}$ , the same symmetry property holds,

$$\delta_i + \delta_{2^{m-t}-1-i} = \delta_{2^{m-t}-1}. \tag{2-6}$$

Therefore, the symmetry property for each sub-matrix of  $\mathbf{W}^{(2)}$  is given as follows,

$$\mathbf{W}_{i,i}^{(2)} = \mathbf{W}_{c-i-1,c-i-1}^{(2)}, \tag{2-7}$$

which indicates that each sub-matrix  $\mathbf{W}_{i,j}^{(2)}$  is identical with its mirror about the anti-diagonal.

According to the construction method of non-binary QC-LDPC codes, every submatrix  $\mathbf{W}_{i,j}^{(2)}$  is also self-symmetric about its own anti-diagonal:

$$\mathbf{w}_{(i,j)(k,l)}^{(2)} = \mathbf{w}_{(i,j)(n-l-1,n-k-1)}^{(2)}.$$

(2-8)

Table 2.1 Proposed surjective function example for  $F'_t$ .

|   | Polynor   | nial form   |             | Power form                     | Element                                    |

|---|-----------|-------------|-------------|--------------------------------|--------------------------------------------|

| 0 |           |             |             | 0                              | $oldsymbol{eta}_0$                         |

| 1 |           |             |             | 1                              | $oldsymbol{eta_{\!\scriptscriptstyle 1}}$  |

|   | $\alpha$  |             |             | $\alpha$                       | $oldsymbol{eta}_2$                         |

|   |           | $lpha^2$    |             | $lpha^2$                       | $oldsymbol{eta_3}$                         |

|   |           |             | $lpha^3$    | $lpha^{\scriptscriptstyle 3}$  | $oldsymbol{eta_4}$                         |

| 1 | $+\alpha$ |             |             | $lpha^{\scriptscriptstyle 4}$  | $oldsymbol{eta_{\scriptscriptstyle{5}}}$   |

| 1 |           | $+\alpha^2$ |             | $lpha^{8}$                     | $oldsymbol{eta_6}$                         |

| 1 |           |             | $+\alpha^3$ | $lpha^{14}$                    | $oldsymbol{eta_7}$                         |

|   | $\alpha$  | $+\alpha^2$ |             | $lpha^{\scriptscriptstyle 5}$  | $oldsymbol{eta_8}$                         |

|   | $\alpha$  |             | $+\alpha^3$ | $lpha^9$                       | $oldsymbol{eta_9}$                         |

|   |           | $lpha^2$    | $+\alpha^3$ | $lpha^{\scriptscriptstyle 6}$  | $oldsymbol{eta}_{\!10}$                    |

| 1 | $+\alpha$ | $+\alpha^2$ |             | $lpha^{10}$                    | $oldsymbol{eta}_{\!\scriptscriptstyle 11}$ |

| 1 | $+\alpha$ |             | $+\alpha^3$ | $lpha^7$                       | $oldsymbol{eta_{12}}$                      |

| 1 |           | $+\alpha^2$ | $+\alpha^3$ | $lpha^{13}$                    | $oldsymbol{eta_{13}}$                      |

|   | $\alpha$  | $+\alpha^2$ | $+\alpha^3$ | $lpha^{\scriptscriptstyle 11}$ | $oldsymbol{eta_{14}}$                      |

| 1 | $+\alpha$ | $+\alpha^2$ | $+\alpha^3$ | $lpha^{12}$                    | $oldsymbol{eta_{15}}$                      |

On the other hand, for Class-II codes, both the base matrix  $\mathbf{W}^{(2)}$  and its sub-matrix  $\mathbf{W}^{(2)}$  are self-symmetric about their diagonals. This can be verified according to the 4<sup>th</sup> step of the construction method of Class-II codes:

$$\mathbf{W}_{i,j}^{(2)} = [(\delta_i - \delta_j) + (\beta_k - \beta_l)]$$

$$= [(\delta_j - \delta_i) + (\beta_k - \beta_l)]$$

$$= \mathbf{W}_{j,i}^{(2)},$$

(2-9)

$$\mathbf{w}_{(i,j)(k,l)}^{(2)} = (\delta_i - \delta_j) + (\beta_k - \beta_l)$$

$$= (\delta_i - \delta_j) + (\beta_l - \beta_k)$$

$$= \mathbf{w}_{(i,j)(l,k)}^{(2)}.$$

(2-10)

In what follows, we will summarize all the proposed geometry properties of Class-II codes in **Proposition 2**:

**Proposition 2** The Class-II non-binary QC-LDPC codes satisfy the geometry properties at three different levels:

- 1. The base matrix  $\mathbf{W}^{(2)}$  is symmetric about its diagonal and anti-diagonal, i.e.,  $\mathbf{W}_{i,j}^{(2)} = \mathbf{W}_{j,i}^{(2)}$  and  $\mathbf{W}_{i,j}^{(2)} = \mathbf{W}_{c-j-1,c-i-1}^{(2)}$ ;

- 2. The sub-matrix  $\mathbf{W}_{i,j}^{(2)}$  is also symmetric about its diagonal and anti-diagonal, i.e., we have  $\mathbf{w}_{(i,j)(k,l)}^{(2)} = \mathbf{w}_{(i,j)(n-l-1,n-k-1)}^{(2)}$  and  $\mathbf{w}_{(i,j)(k,l)}^{(2)} = \mathbf{w}_{(i,j)(l,k)}^{(2)}$ ;

- 3. Each row of one CPM  $\mathbf{w}_{(i,j)(k,l)}^{(2)}$  is the right cyclic-shift of the row above it multiplied by  $\alpha$  and the first row is the right cyclic-shift of the last row multiplied by  $\alpha$ .

Since **Proposition 2.1** and **2.2** are similar, without loss of generality, we only give an example of the latter one. Suppose t = 3 and the minimal polynomial  $p(x) = 1 + x + x^3$ . According to the proposed index assignment scheme,  $\mathbf{W}_{0,0}^{(2)}$  can be constructed as follows:

$$\mathbf{W}_{0,0}^{(2)} = \begin{bmatrix} 0 & 1 & \alpha & \alpha^{2} & \alpha^{3} & \alpha^{6} & \alpha^{4} & \alpha^{5} \\ 1 & 0 & \alpha^{3} & \alpha^{6} & \alpha & \alpha^{2} & \alpha^{5} & \alpha^{4} \\ \alpha & \alpha^{3} & 0 & \alpha^{4} & 1 & \alpha^{5} & \alpha^{2} & \alpha^{6} \\ \alpha^{2} & \alpha^{6} & \alpha^{4} & 0 & \alpha^{5} & 1 & \alpha & \alpha^{3} \\ \alpha^{3} & \alpha & 1 & \alpha^{5} & 0 & \alpha^{4} & \alpha^{6} & \alpha^{2} \\ \alpha^{6} & \alpha^{2} & \alpha^{5} & 1 & \alpha^{4} & 0 & \alpha^{3} & \alpha \\ \alpha^{4} & \alpha^{5} & \alpha^{2} & \alpha & \alpha^{6} & \alpha^{3} & 0 & 1 \\ \alpha^{5} & \alpha^{4} & \alpha^{6} & \alpha^{3} & \alpha^{2} & \alpha & 1 & 0 \end{bmatrix}.$$

(2-11)

It can be observed that  $\mathbf{W}_{0,0}^{(2)}$  is symmetric about its diagonal and anti-diagonal. For **Proposition 2.3**, which is similar to **Proposition 2.1**, similar conclusion can be drawn.

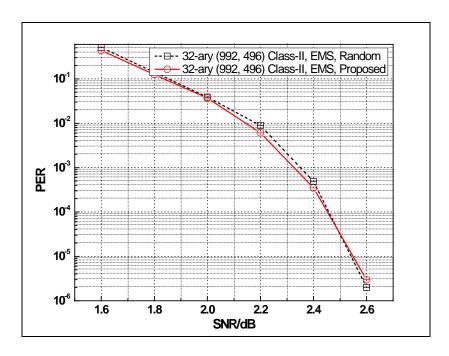

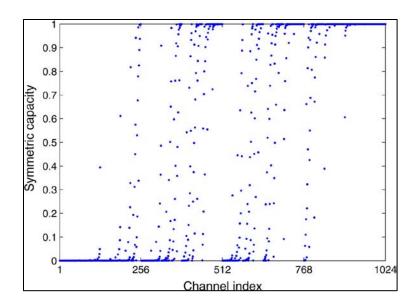

Figure 2.1 Performances of codes with different surjective functions.

We can also check that rows of the base matrix  $W^{(2)}$  constructed according to the proposed surjective function satisfy the  $\alpha$ -multiplied row-column constraints [49]. Assume m = 5 and t = 2. With the code construction steps and surjective function, we can construct a 32-ary (992, 496) rate-0.5 Class-II code. In order to guarantee the decoding performance of codes generated with the proposed surjective function, another Class-II code with random surjective function is employed for comparison. Figure 2.1 illustrates the decoding performances of this code and its random counterpart over AWGN channel with BPSK signaling. The conventional EMS decoding algorithm with maximum iteration number of 10 is used for both codes.

Shown in Figure 2.1, it is observed that the packet error rate (PER) performance of Class-II code with the proposed surjective function is similar as that of the one with random scheme. Therefore, the introduced geometry properties do not affect the algebraic architecture and the decoding advantage of Class-II codes.

# 2.4 Layer Partition Choice for Layered Decoding Algorithm

#### 2.4.1 Review of Layered Decoding Algorithm

The layered decoding approach [75-78] partition the check matrix  $\bf{H}$  into l layers:

$$\mathbf{H}^{\mathsf{T}} = [\mathbf{H}_{0}^{\mathsf{T}} \ \mathbf{H}_{1}^{\mathsf{T}} \cdots \mathbf{H}_{L}^{\mathsf{T}}]. \tag{2-12}$$

Each layer is associated with one super-code  $C_i$ , and the original code C can be treated as the intersection of all l super-codes [76]:

$$C = C_0 \cap C_1 \cap \dots \cap C_{l-1}. \tag{2-13}$$

It is required that the column weight of each layer is equal or less than 1.

The layered decoding message passing schedule with the Min-Max algorithm in the *k*-th iteration for layer *t* can be formulated as follows:

## Layered Decoding for Min-Max Algorithm

**1:**

$$L_{cv}^{k,t}(a) = L_{v}^{k,(t-1)}(a) - R_{cv}^{(k-1),t}(a)$$

;

**2:**

$$R_{cv}^{k,t}(a) = \min_{\substack{(a_{v'})_{v' \in \mathcal{H}(c)\setminus (v)} \\ \in \mathcal{L}(c|a,=a)}} (\max_{v' \in \mathcal{H}(c)\setminus (v)} L_{cv'}^{k,t}(a_{v'}));$$

3:

$$L_{v}^{k,t}(a) = L_{cv}^{k,t}(a) + R_{cv}^{k,t}(a)$$

.

Here,  $L_{cv}^{k,t}(a)$  is the *variable to check* message from layer t to the next layer during the k-th iteration which is associated with finite field element a. And  $R_{cv}^{k,t}(a)$  is the *check to variable* message. The message  $L_v^{k,t}(a)$  is the LLRs from layer t to the next layer during the k-th iteration. Define  $\mathcal{H}(c)$  be the set of variable nodes participating in check node c, and  $\mathcal{H}(c)\setminus (v)$  be the set excluded the variable node v.  $\mathcal{L}(c \mid a_v = a)$  denotes the set of finite sequences which satisfy check node c, given the value of the variable node v equals a. As mentioned above, each layer carries out its own decoding process with both channel inputs and the *extrinsic* output of last layer. Because of this novel updating schedule, the layered decoding propagates much faster than the conventional ones such as the two-

phase message-passing (TPMP) decoding algorithm [26]. Therefore, compared with conventional message passing algorithms, layered decoding performance is better within the same number of decoding iterations.

#### 2.4.2 Layer Partition and Related Decoding Performances

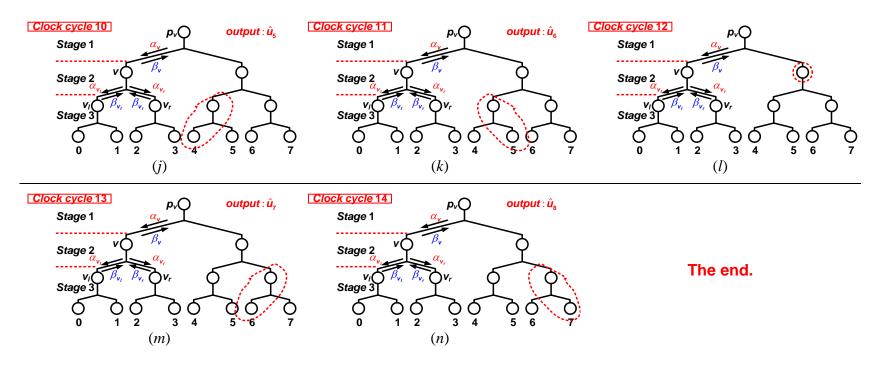

According to **Proposition 1** and **2**, nice algebraic construction enables both classes of non-binary QC-LDPC codes accommodated with the layered decoding algorithm. Inherently, their check matrix **H** can be split into layers. And each layer can naturally serve as a super LDPC code. Actually, we have two layer partition options listed as follows:

- 1. Choose each sub-block row of  $\mathbf{W}_{i,j}^{(1)}$  or  $\mathbf{W}_{i,j}^{(2)}$  as one layer, which consists of (q-1) rows. This option is defined as the *Layer-I* choice;

- 2. Choose each row of CPM within  $\mathbf{w}_{(i,j)(k,l)}^{(1)}$  or  $\mathbf{w}_{(i,j)(k,l)}^{(2)}$  as one layer, which consists of only one row. This option is defined as the *Layer-II* choice.

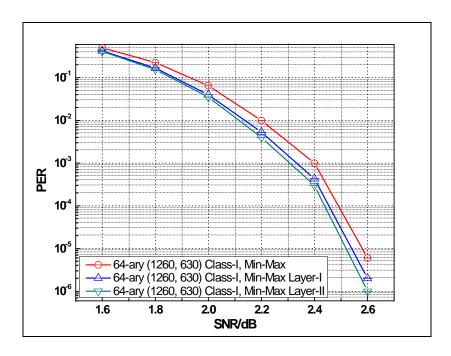

It can be observed that the constraint of at most 1 column weight within each layer is satisfied in both options. To demonstrate the advantages of the layered scheme for non-binary QC-LDPC codes, one decoding example is given as follows. For a 64-ary (1260, 630) rate-0.5 Class-I code, performances of three decoding approaches are compared in Figure 2.2. The maximum number of iterations is set to 10. Decoding performances of the conventional Min-Max algorithm and Min-Max algorithm with two different layer choices are illustrated. According to Figure 2.2, it can be seen that the layered decoding variations can attain more than 0.08 dB decoding gain than the conventional Min-Max algorithm. For the two different layer partition choices, the fewer rows in each layer, the better performance can be achieved. This is because compared with the *Layer-II* choice, more inter-layer *extrinsic* messages are utilized in each iteration of the *Layer-II* choice.

Figure 2.2 PER comparisons between different algorithms for a Class-I code.

# 2.5 A Reduced-Complexity Decoder Architecture

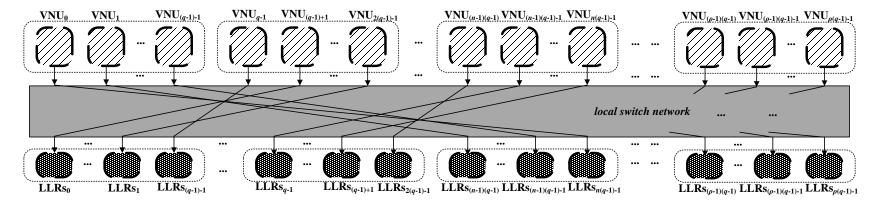

Although non-binary LDPC codes outperform their equivalent binary counterparts, the efficient implementation of non-binary LDPC decoders still remains challenging. Since the routing complexity and control memory size increase drastically with order of GF(q), how to implement low-complexity switch network connecting various processing nodes becomes a big problem. For the (u, v) non-binary QC-LDPC decoder, the straightforward implementation requires  $\rho p(q-1)\gamma$ -bit memory to store all the control signals. Here,  $u = \rho(q-1)$  is the code length, and  $u-v = \gamma(q-1)$  is the number of check bits. In the following part, we present a reduced-complexity decoder architecture based on the proposed geometry properties of non-binary QC-LDPC codes. The decoder is suitable for both serial and semi-parallel approaches. In addition, systematic algorithms to generate *local switch network* of VNUs are proposed for both classes of non-binary QC-LDPC codes.

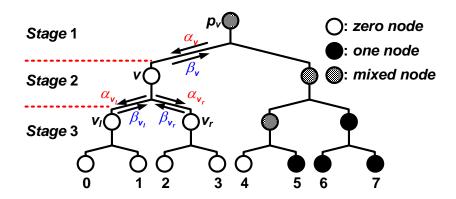

## 2.5.1 Overall Architecture of Reduced-Complexity Decoder

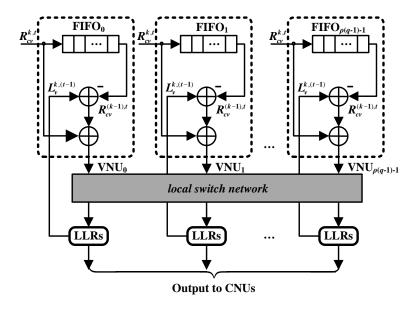

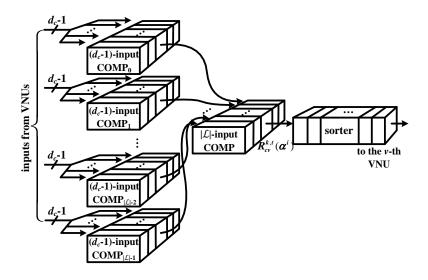

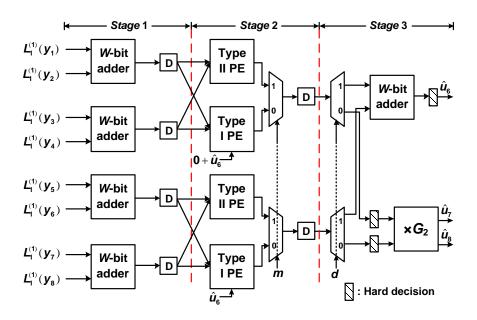

The overall block diagram of the proposed semi-parallel decoder is shown in Figure 2.3. We assume the code-word length and layer height of **H** to be  $\rho(q-1)$  and w, respectively. Illustrated in Figure 2.3, the proposed decoder architecture is composed of an array of  $\rho(q-1)$  VNUs with a *local switch network*, a set of l CNUs, a *global shuffle network*, and a permutation/de-permutation block which implements multiplication/division operation in *Galois* fields. All l rows in each layer are updated in parallel, and a total of  $\gamma(q-1)/w = l$  clock cycles are required per iteration.

Figure 2.3 Block diagram of proposed layered non-binary QC-LDPC decoder.

The most significant point of the *global shuffle network* is, it stays unchangeable in the whole decoding process rather than being reconfigured for each layer. Once the parity check matrix is determined, no more reconfiguring operation is required. The switch network reconfiguration for the remaining layers can be eliminated by employing the *local switch network*.

## 2.5.2 Algorithm for Generating Local Switch Network of VNUs

#### **Local Switch Network for Class-I Codes Cases**

With the shifting properties of Class-I codes in **Proposition 1.2** and **1.3**, the *local switch network* now can be constructed based on a specific circulant permutation algorithm. It is clear that **Proposition 1.2** and **1.3** only differ in the value of the multiplicand ( $\beta$  or  $\alpha$ ). Without loss of generality, here we chose the *Layer-I* decoding scheme as an example.

Intuitively, we can split the *local switch network* shuffling operation between two layers into two steps. Mentioned previously, Eq. (2-2) can be employed to implement the partition of *Layer-I*. In *Step One*, the double mod operation  $((k-1) \mod n, (l-1) \mod n)$  is carried out. The multiplication with  $\beta$ , which introduces another permutation at the level of CPM, is implemented in *Step Two*. The algorithm is given in detail:

#### Scheduling Algorithm for Local Shuffle Network - I

```

Step One

```

**1:** for all  $0 \le i < \rho(q-1)$  do

2: Pass the *extrinsic* result of last layer from

3:  $VNU_i$  to  $VNU_{[i-(q-1)] \mod \rho(q-1)}$

4: endfor

## Step Two

5: for all  $0 \le i < \rho$  do

**6: for all**  $0 \le j < q - 1$  **do**

7: Pass the *extrinsic* result of last layer from

**8:**  $VNU_{i(q-1)+j}$  to  $VNU_{i(q-1)+(j-c) \mod(q-1)}$

9: endfor

10: endfor

**Proof.** Assume the code length is  $\rho(q-1)$ . Therefore, we need the same number of VNUs. Indicated by Eq. (2-2), the interconnection among CNUs and VNUs of the last layer can be reused by the current layer. That is, the *extrinsic* result of the last layer can simply be

shuffled among existing VNUs before decoding the current layer. More specifically, since  $\mathbf{w}_{(i,j)(k,l)}^{(1)}$  is associated with  $\mathbf{w}_{(i,j)((k-1)\bmod n,(l-1)\bmod n)}^{(1)}$ , and the row index modulation can be eliminated if the decoding process is carried out layer by layer, it is only required to assign the *extrinsic* result of VNU<sub>i</sub> to VNU<sub>[i-(q-1)]mod \rho(q-1)</sub>. Also be aware that the jumping stride of *Step One* is *q*-1, which is exactly the size of CPM.

However, the two sub-matrices in Eq. (2-2) are actually not identical, because of the multiplication operation. Therefore, another permutation step named *Step Two* is required. According to the definition of CPM, the CPM of  $\mathbf{w}_{(i,j)(k,l)}^{(1)}$  can be obtained as follows. Firstly, we have to right cyclic shift the CPM of  $\mathbf{w}_{(i,j)((k-1)\bmod n,(l-1)\bmod n)}^{(1)}$  by  $\log_{\alpha}\beta$  steps. Then, we multiply the shifted CPM with  $\beta$ . It is Based on the construction method, we know that,

$$\beta = \alpha^c \Rightarrow \log_\alpha \beta = c. \tag{2-14}$$

Therefore, in *Step Two* an inner permutation with jumping stride of c is carried out. In this way, we assign the *extrinsic* result of  $VNU_{i(q-1)+j}$  to  $VNU_{i(q-1)+(j-c) \mod(q-1)}$ .

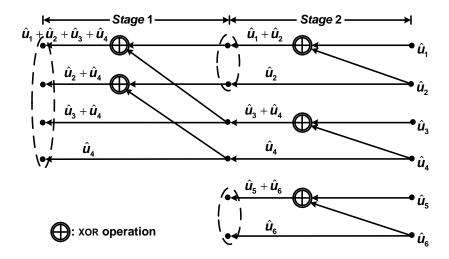

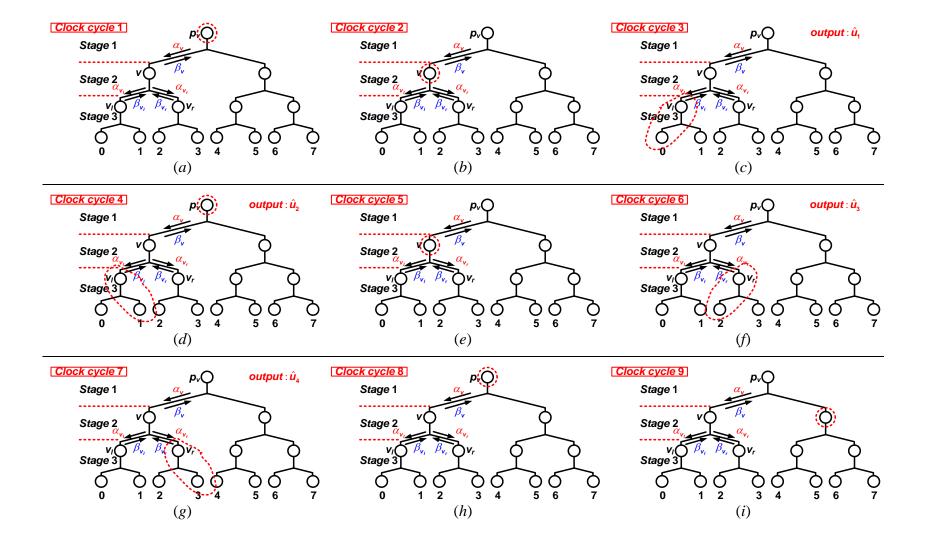

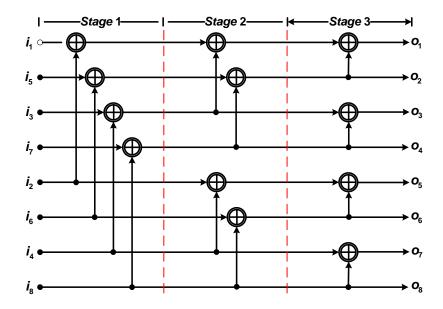

Take the layered decoding of the 4-ary (9, 3) rate- $\frac{1}{3}$  Class-I code shown in Figure 2.4 as an example. The factorization parameters are given as c = 1, n = 3. Therefore, we have  $\beta = \alpha^c = \alpha$  over  $GF(2^2)$ . For instance, as shown in Figure 2.4, VNU<sub>7</sub> is connected with CNU<sub>0</sub> during the 1<sup>st</sup> layer decoding, and with CNU<sub>1</sub> during the 2<sup>nd</sup> layer decoding. On the other hand, according to the decoding scheduling, the *extrinsic* result of VNU<sub>7</sub> is first passed to VNU<sub>4</sub> (*Step One*), then to VNU<sub>3</sub> (*Step Two*) after the 1<sup>st</sup> layer decoding. It is similar for other VNUs. Also it is observed that rather than establishing a new switch network for the 2<sup>nd</sup> layer, the *extrinsic* results of the 1<sup>st</sup> layer can be efficiently shuffled perfectly with the help of the *local switch network*.

Considering both *Step One* and *Step Two* involve the circulant permutations, we can further simplify the scheduling algorithm by removing redundant shifting operations. The resulting new scheduling algorithm merges the former two steps into a single step. The proof is given as follows:

**Proof.** Each VNU's index can be rewritten in the form of i(q-1)+j, where  $0 \le i < \rho$  and  $0 \le j < q-1$ . Therefore, every VNU can be represented with a new notation of (i, j). During *Step One*, whose jumping stride is q-1, the *extrinsic* result is transferred to the  $((i-1) \mod n, j)$  VNU. Thereafter, the message is shuffled to the  $((i-1) \mod n, (j-c) \mod (q-1))$  VNU in *Step Two*. That is, only one step is required to pass the *extrinsic* result of last layer from  $VNU_{i(q-1)+j}$  to  $VNU_{[(i-1) \mod n](q-1)+(j-c) \mod (q-1)}$ .

#### New Scheduling Algorithm for Local Shuffle Network - I

1: for all  $0 \le i < \rho$  do

2: **for all**  $0 \le j < q - 1$  **do**

**3:** Pass the *extrinsic* result of last layer from

**4:**  $VNU_{i(q-1)+j}$  to  $VNU_{[(i-1)\bmod n](q-1)+(j-c)\bmod (q-1)}$

5: endfor

6: endfor

For ease of explanation, the schedule shown in Figure 2.4 is employed as an example again. The index of VNU<sub>7</sub> can be changed into the new form (2, 1). Using the new scheduling algorithm, we can easily find out that the destination index is (1, 0). Therefore, the *extrinsic* message is transferred from VNU<sub>7</sub> to VNU<sub>3</sub> ( $1\times3+0=3$ ), which matches our previous analysis perfectly.

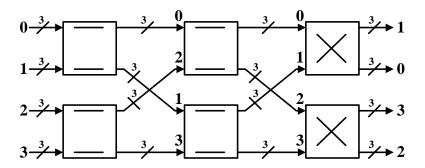

Figure 2.4 Layered decoding example of the 4-ary (9, 3) rate-1/3 Class-I code.

#### **Local Switch Network for Class-II Codes Cases**

Similarly, the *local switch network* for Class-II codes can be implemented based on the inherent symmetry properties in **Proposition 2.2** and **2.3**. At the same time, it is worth noting that, indicated by Eq. (2-7)-(2-10), we only need to take care of the symmetry execution rather than both symmetry and multiplication. The scheduling algorithm for Class-II codes can be derived as follows,

#### Scheduling Algorithm for Local Shuffle Network - II

```

1: for all 0 < v \le l, the beginning of decoding the vth layer do

```

- 2: for all  $0 \le i < \rho$  do

- **3: for all**  $0 \le j < q 1$  **do**

- 4: Pass result of VNU<sub> $(q-1)(index_{y-1,i mod n} + n[i/n])+j</sub>$ </sub>

- 5: to  $VNU_{(q-1)(\mathbf{index}_{v,i \mod n} + n\lfloor i/n \rfloor) + j}$

- **6:** endfor

- 7: endfor

- 8: endfor

The **INDEX**<sup>(n)</sup> matrix is an  $n \times n$  matrix defined as **INDEX**<sup>(n)</sup> = [**index**<sub>i,j</sub>]<sub> $0 \le i < n, 0 \le j < n$ </sub>. The entries of the first row of **INDEX** are determined by **index**<sub>0,j</sub> = j as default. Other entries can be derived from the index assignment of *surjective function* and symmetry properties of **Proposition 2.2** and **2.3**. For instance, **INDEX**<sup>(4)</sup> is given as follows,

INDEX<sup>(4)</sup> =

$$\begin{bmatrix} 0 & 1 & 2 & 3 \\ 1 & 0 & 3 & 2 \\ 2 & 3 & 0 & 1 \\ 3 & 2 & 1 & 0 \end{bmatrix}.$$

(2-15)

It is observed that the matrix **INDEX**<sup>(4)</sup> is symmetric about both its diagonal and anti-diagonal. The entries on the diagonal are 0's, and the entries on the anti-diagonal are all 3's (= n-1). The last row (column) is the reverse-order version of the first row (column), and *vice versa*. The proof is given as follows,

**Proof.** According to Eq. (2-8) and Eq. (2-10), the sub-matrix  $\mathbf{w}_{(i,j)(k,l)}^{(2)}$  is identical to both  $\mathbf{w}_{(i,j)(n-l-1,n-k-1)}^{(2)}$  and  $\mathbf{w}_{(i,j)(l,k)}^{(2)}$ . Therefore, the interconnection among CNUs and VNUs of the last layer is exactly the same as that of the current layer, and can be reused afterwards. Indicated by **Proposition 2**, the index of destination VNU can be obtained by using symmetry properties. Since there is no permutation for the very beginning row, the first row of **INDEX** is set as an array of n elements from 0 to n-1. Each column is associated with one specific VNU during a iteration. Since the dimension of **INDEX** is n, the same mapping scheme based on **INDEX** is performed by every n VNUs. Therefore, a modulo operation on the VNU index is required.

A simple example is employed to give a clear explanation. For the 4-ary (12, 6) rate-1/2 Class-II code illustrated in Figure 2.5, the factorization parameters can be obtained by choosing t = 1. Accordingly,  $c = 2^{m-t} = 2$ , and  $n = 2^t = 2$  over  $GF(2^2)$ . The subgroups are  $F'_t = \{0, \beta_1\} = \{0, 1\}$  and  $F''_{m-t} = \{0, \delta_1\} = \{0, \alpha\}$ . Therefore, the index matrix **INDEX**<sup>(4)</sup> is given as follows,

$$\mathbf{INDEX}^{(2)} = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}. \tag{2-16}$$

Figure 2.5 Layered decoding example of the 4-ary (12, 6) rate-½ Class-II code.

As illustrated in Figure 2.5, after the  $1^{st}$  layer decoding, the *extrinsic* message of VNU<sub>0</sub> is transferred according to the following direction:

$$VNU_{3\times(index_{0.0}+0)+0} \to VNU_{3\times(index_{1.0}+0)+0} = VNU_3.$$

(2-17)

For the other VNUs, similar permutations can be obtained accordingly. The permutations are listed as follows,

| $VNU_0 \rightarrow VNU_3$ , | $VNU_6 \rightarrow VNU_9$ ,    |

|-----------------------------|--------------------------------|

| $VNU_1 \rightarrow VNU_4$ , | $VNU_7 \rightarrow VNU_{10}$ , |

| $VNU_2 \rightarrow VNU_5$ , | $VNU_8 \rightarrow VNU_{11}$ , |

| $VNU_3 \rightarrow VNU_0$ , | $VNU_9 \rightarrow VNU_6$ ,    |

| $VNU_4 \rightarrow VNU_1$ , | $VNU_{10} \rightarrow VNU_7$ , |

| $VNU_5 \rightarrow VNU_2$ , | $VNU_{11} \rightarrow VNU_8$ . |

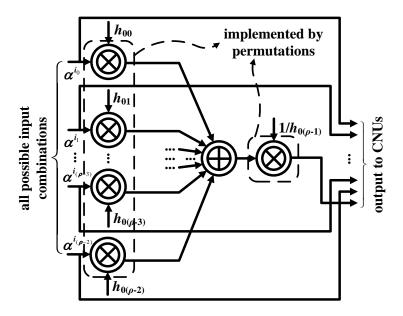

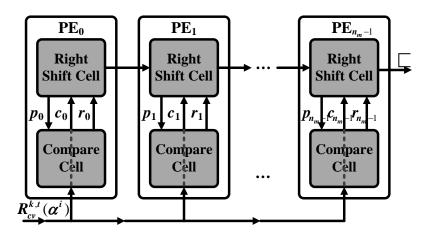

#### 2.5.3 Architectures of VNUs' Local Switch Network

## **Local Switch Network for Class-I Codes**