# EFFICIENT DYNAMIC PROGRAM MONITORING ON MULTI-CORE PLATFORMS

# ${\bf A~DISSERTATION}$ SUBMITTED TO THE FACULTY OF THE GRADUATE SCHOOL OF THE UNIVERSITY OF MINNESOTA

$\mathbf{BY}$

#### **GUOJIN HE**

# IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

ANTONIA ZHAI, ADVISOR

© GUOJIN HE 2012

ALL RIGHTS RESERVED

## Acknowledgements

First and foremost, I would cordially thank my advisor, Professor Antonia Zhai, for her great help, enduring patience, and invaluable advices throughout my entire doctoral program.

I also say thank you to Professor Mats Heimdahl, Professor David J. Lilja, and Dr. Michael Whalen for their generous help, encouragement, and suggestions during my thesis research. I also thank them for serving as members of my examination committee. Moreover, I would like to thank Professor Pen-Chung Yew and Professors Wei-Chung Hsu for their encouragement and help during my Ph.D studies and studies and for providing advice about my career.

I also appreciate my fellow co-workers: Jinpyo Kim, Shengyue Wang, Jin Lin, Venkatesan Packirisamy, Yangchun Luo, Vineeth Mekkat, Ragavendra Natarajan, Jieming Yin, and Anup P Holey for their friendship and technical help.

I am also indebted to my personal friends Professor Ziguo Zhong, and Dan Wang for their enormous help and encouragement in life and in research during my Ph.D studies.

Furthermore, I want to thank the people I have worked with during my internship and current employment, along with friends in China. Their creative minds and ideas inspired me in great measure.

Lastly, I would say thanks to my parents, my sister, and her family for their unconditional love and support.

#### Abstract

Software security and reliability have become increasingly important in the modern world. An effective approach to enforcing software security and reliability is to monitor a program's execution at run time. However, instrumentation-based implementation of a dynamic program monitor on single-core systems suffers significant performance overhead. As multi-core architecture becomes more mainstream, implementing efficient dynamic program monitoring by assigning monitoring activities onto separate processor cores and thus reducing performance overhead becomes not only a feasible but an appealing way to enforce software security and reliability. To achieve efficient and flexible multi-core based dynamic program monitoring, however, three challenging issues must be carefully considered and adequately addressed: the hardware support, the monitoring model, and the parallelization of monitoring tasks.

This dissertation proposes novel solutions to these challenging problems. The hardware support proposed in this dissertation, which is referred to as extraction logic, selectively extracts execution information from the monitored program and forwards it to a monitor running on a separate CPU core. The extraction logic is generic and configurable by the monitor so that it can support a large spectrum of monitoring tasks. Based on this generic hardware support, this dissertation proposes a novel monitoring model, referred to as the distill-based monitor model. Monitors in this execution model is generated by special compiler supports. The distill-based

monitor model is based on the observation that a monitor needs only partial information from the monitored execution and that of this needed information, some can be easily computed by the monitor from other information that has already been communicated. We implemented a code generator and optimization techniques to decide which set of information to forward and which set to compute so as to minimize the total execution time of the monitor. This compiler support can optimize a variety of monitors with diverse monitoring requirements, taking as input the control flow graph of the monitored program and the set of monitoring requirements.

To parallelize monitoring tasks, this dissertation proposes a novel parallelization paradigm built on General-purpose Computing on Graphics Processing Unit (GPGPU) architecture. In the following chapters, we first propose a generic, purely software-based GPGPU monitor framework that is flexible enough to support parallelization of various kinds of monitoring tasks. Furthermore, we propose software-based optimization techniques built on this framework that effectively take advantage of various characteristics of monitoring tasks such as taint-propagation and memory-bug detection, and thus achieve significant performance improvement.

This dissertation reports the performance improvement achieved by the proposed monitoring model and parallelization paradigm. Relative to the performance of traditional instrumentation-based monitor for taint-propagation and memory-bug-detection, the proposed compiler support is able to bring down performance overhead by 3.7 times and 2.2 times for SPEC2006INT benchmarks. The proposed GPGPU-based monitor with optimization even achieves more for memory-bug detection, reducing performance overhead by 5.2 times.

# Contents

| $\mathbf{A}$ | ckno                   | wledgements                                                 |     |

|--------------|------------------------|-------------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra                  | act                                                         | i   |

| Li           | st of                  | Tables                                                      | /ii |

| ${f Li}$     | $\operatorname{st}$ of | Figures                                                     | ix  |

| ${f Li}$     | $\operatorname{st}$ of | Abbreviations                                               | Х   |

| 1            | Inti                   | roduction                                                   | 1   |

|              | 1.1                    | Background of Dynamic Program Monitoring and Its Challenges | 2   |

|              | 1.2                    | Multi-core-based Dynamic Program Monitoring                 | 4   |

|              | 1.3                    | Major Research Efforts and Results in the Dissertation      | 6   |

|              | 1.4                    | Organization of the Manuscript                              | 6   |

| <b>2</b>     | Har                    | rdware Support for Dynamic Program Monitoring on Multi-core |     |

|              | Pla                    | tforms                                                      | 8   |

|              | 2.1                    | Overview of Hardware Support                                | 8   |

|              | 2.2                    | Table-Driven Extraction Logic                               | 11  |

|              | 2.3                    | Forward-Bit-Based Extraction Logic                          | 13  |

|              |                        | 2.3.1 Fetching Component                                    | 13  |

|              |                        | 2.3.2 Forwarding Component                                  | 15  |

| 3 | Exe | cution                                         | Models of Multi-core-based Program Monitor                                                                                                                                                                                                                                               | 18 |  |  |

|---|-----|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

|   | 3.1 | Exam                                           | xample of Monitor Models                                                                                                                                                                                                                                                                 |    |  |  |

|   | 3.2 | Dispat                                         | 2.2 Monitoring Functions                                                                                                                                                                                                                                                                 |    |  |  |

|   |     | 3.2.1                                          | Dispatching Routine  Monitoring Functions  Initialization and Update Routines  Key Idea of Distill-based Monitor  Generating Distill-based Monitor  3.3.2.1 Monitoring Functions  ualitative Analysis of Performance Overhead  Analysis of Performance Overhead of Distill-based Monitor |    |  |  |

|   |     | 3.2.2                                          | Monitoring Functions                                                                                                                                                                                                                                                                     | 22 |  |  |

|   |     | 3.2.3                                          | Initialization and Update Routines                                                                                                                                                                                                                                                       | 23 |  |  |

|   | 3.3 | Distill                                        | -based Monitor                                                                                                                                                                                                                                                                           | 23 |  |  |

|   |     | 3.3.1                                          | Key Idea of Distill-based Monitor                                                                                                                                                                                                                                                        | 24 |  |  |

|   |     | 3.3.2                                          | Generating Distill-based Monitor                                                                                                                                                                                                                                                         | 25 |  |  |

|   |     |                                                | 3.3.2.1 Monitoring Functions                                                                                                                                                                                                                                                             | 27 |  |  |

|   | 3.4 | A Qua                                          | 3.3.2.1 Monitoring Functions                                                                                                                                                                                                                                                             |    |  |  |

|   |     | 3.4.1                                          | Analysis of Performance Overhead of Distill-based Monitor                                                                                                                                                                                                                                | 29 |  |  |

|   |     | 3.4.2                                          | How Distill-based Monitor Reduces Performance Overhead                                                                                                                                                                                                                                   | 30 |  |  |

| 4 | Opt | imizat                                         | ion of Distill-based Monitor                                                                                                                                                                                                                                                             | 32 |  |  |

|   | 4.1 | General Ideas and Concepts of the Optimization |                                                                                                                                                                                                                                                                                          |    |  |  |

|   | 4.2 | Algori                                         | thm Overview                                                                                                                                                                                                                                                                             | 36 |  |  |

|   | 4.3 | Information Needed by the Algorithm            |                                                                                                                                                                                                                                                                                          | 37 |  |  |

|   |     | 4.3.1                                          | Reaching Definition                                                                                                                                                                                                                                                                      | 37 |  |  |

|   |     | 4.3.2                                          | Basic Dependence Set                                                                                                                                                                                                                                                                     | 39 |  |  |

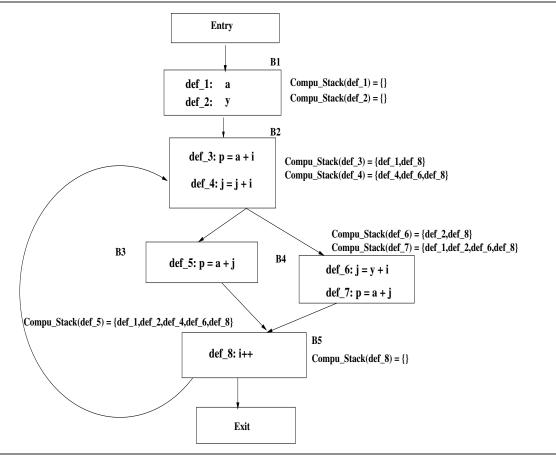

|   |     | 4.3.3                                          | Computation Stack                                                                                                                                                                                                                                                                        | 40 |  |  |

|   | 4.4 | Select                                         | Select OptCommu and OptCompute Set: Details of Algorithm                                                                                                                                                                                                                                 |    |  |  |

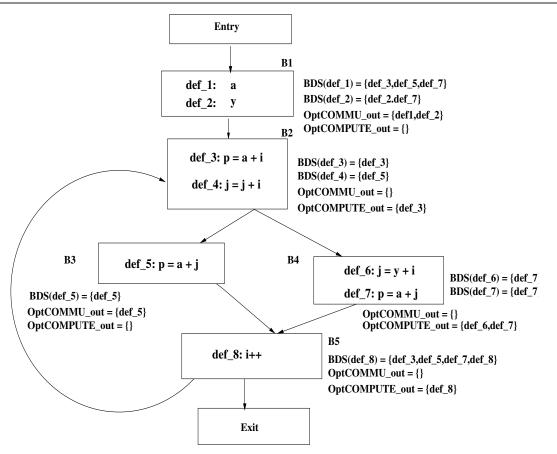

|   |     | 4.4.1                                          | Select $OptCommu$ and $OptCompute$ Set: Forward DFA Pass .                                                                                                                                                                                                                               | 41 |  |  |

|   |     | 4.4.2                                          | Estimation of Benefit and Cost                                                                                                                                                                                                                                                           | 43 |  |  |

|   | 4.5 | Discus                                         | ssion of Complexity of the Optimization                                                                                                                                                                                                                                                  | 47 |  |  |

|   |     | 151                                            | Complexity of Information Collection DFA Passes                                                                                                                                                                                                                                          | 47 |  |  |

|   |      | 4.5.2    | Analysis   | of Complexity of OptCommu and OptCompute Set           |      |    |

|---|------|----------|------------|--------------------------------------------------------|------|----|

|   |      |          | Selection  |                                                        | 49   |    |

|   | 4.6  | Perfori  | nance Ev   | aluation                                               | 51   |    |

|   |      | 4.6.1    | Infrastru  | cture                                                  | 52   |    |

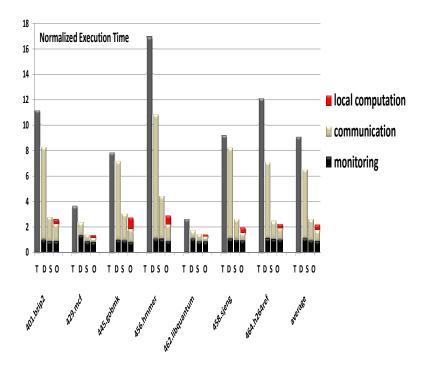

|   |      | 4.6.2    | Performa   | ance of Different Monitor Implementations              | 54   |    |

|   |      | 4.6.3    | Compari    | son with Hardware-Based Optimizations                  | 57   |    |

| 5 | Para | allelize | Program    | n Monitoring Using GPGPU                               | 60   |    |

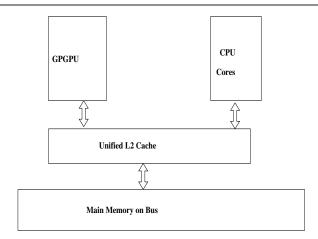

|   | 5.1  | GPGP     | U Archite  | ecture to Parallelize Dynamic Program Monitoring       | 62   |    |

|   |      | 5.1.1    | Integrati  | ng CPU and GPGPU Cores                                 | 63   |    |

|   |      | 5.1.2    | Characte   | eristics of Memory-Bug Detection and Taint Propagation | 64   |    |

|   |      |          | 5.1.2.1    | Memory-Bug Detection                                   | 65   |    |

|   |      |          | 5.1.2.2    | Taint Propagation                                      | 65   |    |

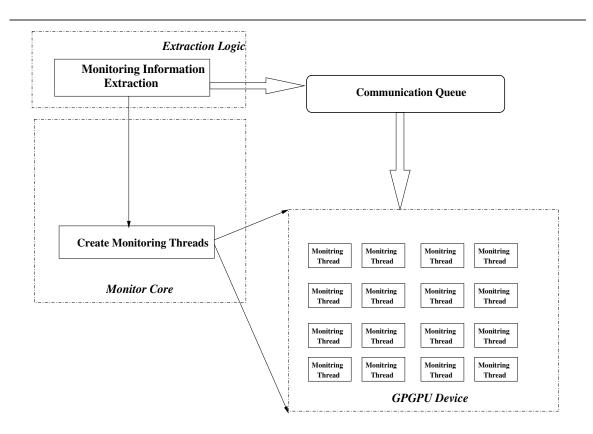

|   | 5.2  | Abstra   | ct Frame   | work of GPGPU-based Monitor                            | 67   |    |

|   |      | 5.2.1    | GPGPU-     | -based Monitoring                                      | 67   |    |

|   |      | 5.2.2    | Overview   | of the GPGPU-based Monitor                             | 71   |    |

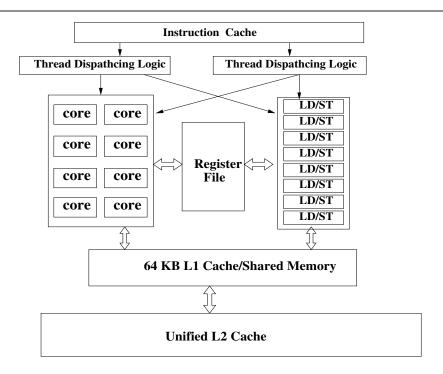

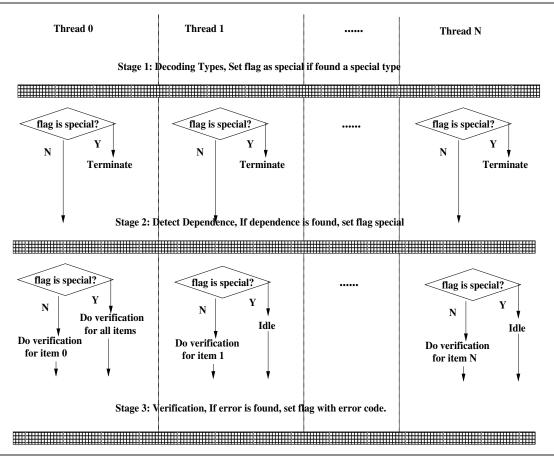

|   |      | 5.2.3    | Impleme    | ntation of Monitoring Thread                           | 73   |    |

|   |      |          | 5.2.3.1    | Abstract Framework of Monitoring Thread                | 74   |    |

|   |      |          | 5.2.3.2    | Implementation of Monitoring Thread for Memory-        |      |    |

|   |      |          |            | bug Detection                                          | 76   |    |

|   |      |          | 5.2.3.3    | Implementation of Monitoring Thread for Taint-Propagat | tion | 78 |

|   | 5.3  | Optim    | ization of | GPGPU-based Monitors                                   | 81   |    |

|   |      | 5.3.1    | Techniqu   | es of Optimizing GPGPU-based Monitor                   | 84   |    |

|   |      |          | 5.3.1.1    | Optimizing Memory-bug Detection Monitor on GPGPU       | 85   |    |

|   |      |          | 5.3.1.2    | Optimizing Taint Propagation Monitor on GPGPU .        | 89   |    |

|   | 5.4  | Perfori  | mance of   | Optimized GPGPU-based Monitor                          | 95   |    |

|   |      | 5.4.1    | Infrastru  | cture                                                  | 95   |    |

| Bi | Bibliography 11 |          |                                                         |     |

|----|-----------------|----------|---------------------------------------------------------|-----|

| 7  | Con             | ıclusioı | ns                                                      | 112 |

|    | 6.4             | Paralle  | el Monitors                                             | 110 |

|    | 6.3             | Monito   | ors on Multi-core Platforms                             | 108 |

|    | 6.2             | Monito   | ors with Task-specific Hardware Support                 | 107 |

|    | 6.1             | Instru   | mentation-based Monitors                                | 105 |

| 6  | Rela            | ated W   | Vork                                                    | 104 |

|    |                 |          | Memory-bug Detection                                    | 101 |

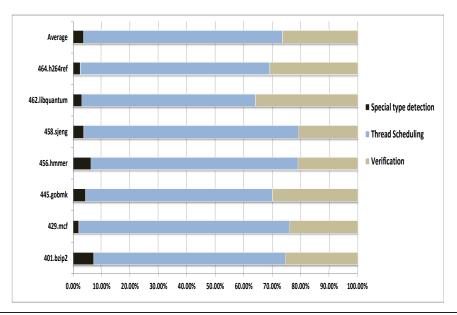

|    |                 | 5.4.4    | Performance Analysis of Optimized GPGPU-based Monitors: |     |

|    |                 |          | Taint Propagation                                       | 99  |

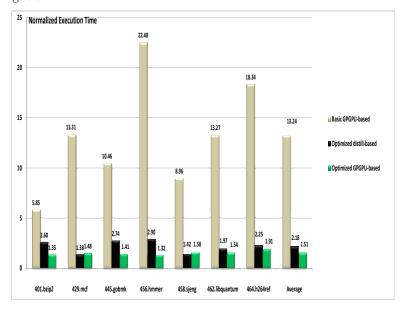

|    |                 | 5.4.3    | Performance Analysis of Optimized GPGPU-based Monitors: |     |

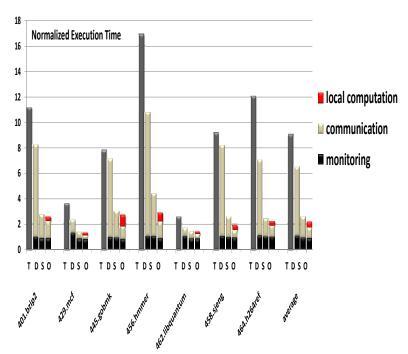

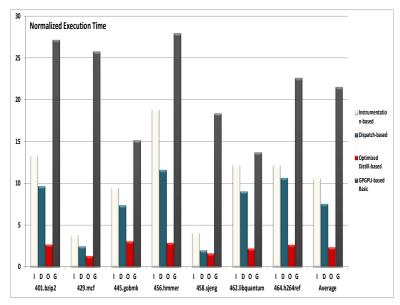

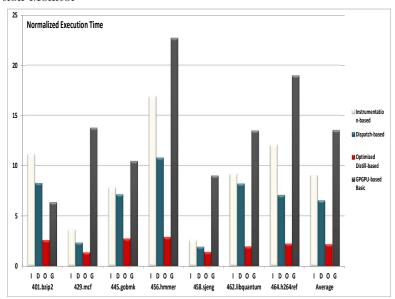

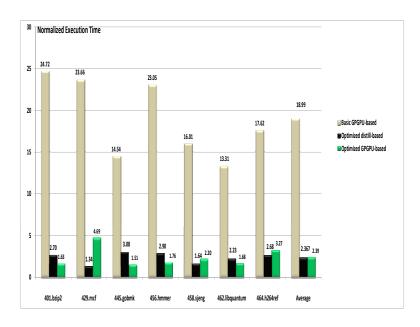

|    |                 | 5.4.2    | Performance of Optimized GPGPU-based Monitors           | 97  |

# List of Tables

| 4.1 | Benchmark Descriptions                                                  | 51  |

|-----|-------------------------------------------------------------------------|-----|

| 4.2 | Simulation Parameters                                                   | 52  |

| 5.1 | Comparisons of Characteristics of Different Implementations of Monitors | 72  |

| 5.2 | Dependence in Memory-bug Detection                                      | 76  |

| 5.3 | Behavior and Activities of Monitored Events in Taint Propagation        | 79  |

| 5.4 | Performance Statistics of Basic GPGPU-based Monitor                     | 82  |

| 5.5 | GPGPU-based Monitor Simulation Parameters                               | 96  |

| 5.6 | Statistics of Optimized GPGPU-based Taint Propagation Monitor           | 100 |

| 5.7 | Statistics of Optimized GPGPU-based Memory-bug Detection Monitor 1      | 102 |

# List of Figures

| 2.1 | Extraction Logic in Table-driven Mode                                 | 10 |

|-----|-----------------------------------------------------------------------|----|

| 2.2 | Extraction Logic in Forward Bit Mode                                  | 17 |

| 3.1 | Four different Implementations of the Memory-bug Detection Monitor.   | 19 |

| 3.2 | Dispatch-based Monitor for Memory-bug Detection                       | 21 |

| 3.3 | Performance Comparison of Dispatch-based Dynamic Monitors on Multi-   |    |

|     | core for Taint Propagation                                            | 23 |

| 3.4 | Overview of the Distill-based Monitoring System                       | 25 |

| 4.1 | Code Example of Using Compiler to Reduce Communication                | 33 |

| 4.2 | Control Flow Graph of the Sample Program and Results of Reaching      |    |

|     | Definition DFA                                                        | 34 |

| 4.3 | Results of Basic Dependence Set DFA Pass for the Sample Program $ . $ | 38 |

| 4.4 | Results of Computation Stack DFA Pass for the Sample Program $$ . $$  | 40 |

| 4.5 | Distill-based Monitor Optimization Algorithm                          | 42 |

| 4.6 | Results of Optimization DFA Pass                                      | 46 |

| 4.7 | Performance of Four Different Implementations of Monitors             | 55 |

| 4.8 | Performance Comparison with Additional Hardware Support               | 57 |

| 5.1 | A System Architecture Fusing CPU cores and GPGPU together             | 62 |

| 5.2 | Layout of a Stream Multiprocessor                                     | 64 |

| 5.3 | GPGPU-based monitoring                                                | 69 |

| 5 4 | Algorithm for a GPGPU-based Monitor                                   | 70 |

| 5.5  | General Framework of Monitoring Thread Implementation          | 73  |

|------|----------------------------------------------------------------|-----|

| 5.6  | Performance of Basic GPGPU-based Monitors                      | 83  |

| 5.7  | lem:lem:lem:lem:lem:lem:lem:lem:lem:lem:                       | 86  |

| 5.8  | Algorithm of Optimized Taint Propagation GPGPU-based Monitor   | 90  |

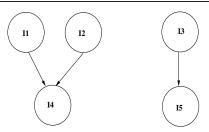

| 5.9  | Dependence Graph of the Instruction Sequence, Arrows come from |     |

|      | dependees to dependents                                        | 92  |

| 5.10 | Performance of Optimized GPGPU-based Monitors                  | 98  |

| 5.11 | Execution Time Breakdown of Optimized GPGPU-based Taint Prop-  |     |

|      | agation Monitor                                                | 101 |

## Chapter 1

#### Introduction

As computer systems have become necessities in virtually all important aspects of human life today, computer software plays an increasingly important role in the safety and welfare of modern societies. Consequently, the security and reliability of software are extremely critical issues in the modern world. In modern computer systems, there are two major approaches to enforcing software security and reliability: statically examining source code [1, 2, 4, 3] and dynamically monitoring program execution [5, 11, 12, 10, 6, 7]. The latter is becoming increasingly important and common due to several trends that make static approaches more expensive and less effective: first, rapid increases in the complexity of modern software systems; second, rapid increases in data size, and last but not the least, fast-changing and unpredictable environments where software programs are deployed.

Efficiency is the key issue for successful dynamic program monitoring systems. Since dynamic program monitoring systems must run side by side with monitored execution on the same hardware platform, the performance overhead of monitoring is added to the performance of monitored program execution. In the uniprocessor era, this overhead could be prohibitively high and thus prevented dynamic program

monitors from being widely deployed. Recently, however, the emergence of multicore architecture facilitates future dynamic program monitoring as it enables more efficient paradigms. This dissertation reports our research efforts on the design, implementation and evaluation of an efficient dynamic program monitoring system built on multi-core platforms.

# 1.1 Background of Dynamic Program Monitoring and Its Challenges

All dynamic program monitoring systems must implement the following key functionalities:

- 1. extracting information about the monitored program execution.

- 2. maintaining meta-data a.k.a shadow data to keep track of the status of monitored execution.

Based on the differences in implementation, dynamic monitoring systems can be classified into three categories: instrumentation-based monitoring systems [5, 11, 12, 10, 6, 7]; specialized-hardware-based monitoring systems [26, 27, 28, 29, 31, 32, 33, 34] and multi-core-based monitoring systems [53, 54].

The research reported in this dissertation falls into the multi-core-based category. Multi-core-based monitoring addresses challenges faced by the other two categories of dynamic program monitoring. This section briefly describes and compares basic ideas and key features of three different approaches. Details of multi-core-based monitoring proposed by our research is left to later chapters of this dissertation.

Instrumentation-based dynamic program monitoring tools use monitoring code to instrument the binary or the original source code of monitored program. The monitoring code tracks changes in the status of the monitored program and verifies compliance with security or reliability rules that are defined by the monitoring requirements. Many well-known instrumentation-based program monitoring tools allow instrumentation of the user program at a fine-grained level [5, 12, 10, 6, 7]. This way, they can support popular monitoring requirements such as taint-propagation and memory-bug-detection that require detailed run-time information such as referred memory addresses, sources and destinations of data movements, as well as targets of jump instructions.

The main disadvantage of instrumentation-based dynamic program monitoring tools is that their performance overhead is significant. Instruction-grained monitoring tasks such as taint-propagation or memory-bug-detection can slow monitored programs by 10-50 times [6, 7]. This disadvantage prevents instrumentation-based monitoring tools from being employed for wider applications. The root cause of this high performance overhead is that instrumentation code competes with its monitored execution for limited hardware resources during execution/monitoring time.

As an alternative to instrumentation-based approaches, researchers have proposed using specialized hardware support to accelerate dynamic program monitoring. [26, 27, 28, 29, 31, 32, 33, 34]. Dynamic program monitoring systems with these specialized hardware supports do not instrument the monitored program. Instead, the specialized hardware supports take over the tasks of information extraction, metadata maintaining and status checking. Depending on the monitoring requirements, these hardware supports extend the existing micro-architecture design in different ways: some add additional function units into the processor pipeline [26, 27], some augment the memory hierarchy [29, 32, 33], and others introduce new type of storage to accommodate meta-data [28, 32, 33]. Compared to instrumentation-based approaches, these specialized hardware supports significantly reduce the performance overhead of dynamic program monitoring.

The disadvantage of dynamic monitoring with specialized hardware support is that its application is limited to a specific type of monitoring activity. In other words, this approach is inflexible. Fundamentally, different monitoring tasks require different monitoring activities, and thus specialized hardware support must be customized to the characteristics of each monitoring activity to be effective.

# 1.2 Multi-core-based Dynamic Program Monitoring

The research reported by this dissertation is different from previous proposals in that it is built on multi-core platforms to keep the monitoring system both flexible and efficient. It is different from other multi-core-based monitoring systems [34, 39, 49], as other systems mainly rely on hardware approach to implement and accelerate monitoring. The research in this dissertation uses both hardware approach and software approach to implement efficient multi-core-based monitoring. As this will be elaborated upon later, in this section we focus on introducing the common characteristics of multi-core based dynamic program monitoring.

In typical multi-core based dynamic program monitoring systems, two software entities simultaneously execute on separate cores: the program to be monitored and the program that monitors. In this dissertation, they are referred to as the monitored program and the monitor, respectively. During a monitored execution, the execution information of the monitored program such as the addresses of accessed memory, updated values of registers, and branch direction are collected by a dedicated hardware circuit, referred to as extraction logic in this dissertation. The extraction logic forwards every piece of collected information to the monitor on another core in real time through a software queue implemented in the shared memory. The monitor obtains the forwarded information from the queue and uses it to track the progress of the

monitored execution and to check against security or reliability rules derived from the monitoring requirements. From the perspective of the shared memory, the monitored program and its monitor are the producer and consumers of the software queue. In this dissertation, the queue is referred to as the communication queue.

To make a multi-core based dynamic program monitoring system flexible, hard-ware support must be able to supply information needed by a large spectrum of monitoring requirements in real time. This issue is addressed by all research efforts on multi-core based program monitoring including ours [34, 38, 54].

The performance overhead in multi-core-based monitoring systems is caused by two types of stall in the monitored program. First, when the queue becomes full, the monitored program must stall to prevent information in the queue from being overwritten. Secondly, before doing a system call, the monitored program must stall to make sure all queue entries are verified by the monitor. This stall guarantees that the OS kernel is adequately protected by the monitor. In most heavy-load monitoring activities, the first type of stalls occurs far more frequently than the other, and thus is the predominant cause of performance overhead.

The research reported by this dissertation also diverges from other research proposals for multi-core-based program monitoring [34, 38] in its approach to reducing performance overhead caused by frequent queue stalls. While other proposals resort to introducing specialized hardware support to reduce the performance overhead, this dissertation proposes a novel monitor model that reduces communication between the monitored program and the monitor to improve performance. Furthermore, this dissertation reports our efforts on leveraging the emerging parallel architecture General Purpose Graphics Processing Units(GPGPU) to improve the performance of dynamic program monitoring.

# 1.3 Major Research Efforts and Results in the Dissertation

The goal of this dissertation is to present following research efforts and results:

- The proposal of a generic hardware support that enables efficient and flexible dynamic program monitoring on multi-core platforms.

- The proposal of an efficient multi-core based monitor model: the distill-based monitor model, and the compiler support that implements and optimizes it.

- The proposal of using General Purpose Graphical Processing Units(GPGPU) to parallelize dynamic program monitoring, and the software framework and optimization techniques that implements the proposed idea.

- A comprehensive performance evaluation of proposed technologies on a detailed simulation platform. Results of the performance evaluation show that the proposed technologies significantly reduce the performance overhead of dynamic program monitoring for generic monitoring requirements.

#### 1.4 Organization of the Manuscript

The rest of this dissertation is organized as follows. Chapter 2 presents the details of the generic hardware support used to achieve flexible monitoring on multi-core platforms. Chapter 3 presents two different types of monitor models, referred to as the dispatch-based model and the distill-based model on multi-core based dynamic program monitoring systems, emphasizing the more efficient of the two, the distill-based model. Chapter 4 describes the novel compiler support that implements code generation and the optimization of the distill-based model. Chapter 5 illustrates the design and implementation of parallel dynamic program monitoring with GPGPU

architecture. Chapter 6 lists previous research related to the scope of this dissertation, and Chapter 7 concludes the dissertation.

## Chapter 2

# Hardware Support for Dynamic Program Monitoring on Multi-core Platforms

This chapter presents the generic hardware support for the multi-core based dynamic program monitoring in the research reported by this dissertation. This hardware support is referred to as *extraction logic*. The chapter begins with an overview of the extraction logic, illustrating its functionality and its two different work modes. It then dedicates two sections to giving a detailed description of the hardware components that implement the two modes of the extraction logic, demonstrating how they accelerate dynamic program monitoring for a large spectrum of monitoring tasks.

#### 2.1 Overview of Hardware Support

The dynamic monitoring system proposed in this dissertation uses both hardware support and software support to implement multi-core-based monitoring. In this system, the hardware support is referred to as extraction logic, which selectively extracts information from the monitored process and sends it to the monitor running on a separate core. In the on-chip multi-core system that runs the dynamic monitoring, every core is augmented with this extraction logic so that the monitored process is not bounded to a specific core. For each core, its extraction logic is enabled only when it runs a monitored process.

The key feature of extraction logic is its ability to selectively forward execution information for the monitored process. In the context of this dissertation, the dynamic execution information includes instruction-related values such as referred memory addresses, updated destination register values, and instruction addresses(PC). These values are available at the commit stage of each dynamic instruction. Extraction logic obtains this information from the processor pipeline's Reorder Buffer (ROB) and Load-Store Queue(LSQ) where this information is stored when an instruction commits.

In extraction logic, selecting dynamic execution information is essentially extracting values generated when the instructions of interest are executed. For example, the extraction logic can be instructed to extract referred memory addresses for a specified read instruction and ignore all other instructions.

There are two different approaches to direct extraction logic what instructions should have their information extracted: one is driven by a table with a list of instructions and the other by per-instruction flag bit, referred to as the forward bit that indicates whether it is of interest to the monitor. To support the two approaches, extraction logic is configured to work in two different modes. The following two sections illustrate the components of extraction logic that support the two approaches.

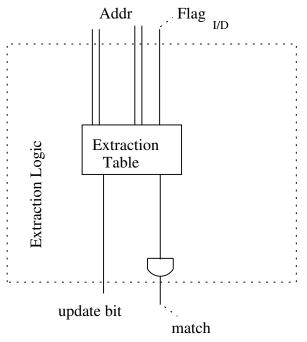

(a) Inside the extraction logic: Table-Driven Mode.

Figure 2.1: Extraction Logic in Table-driven Mode

#### 2.2 Table-Driven Extraction Logic

The key component of extraction logic in the table-driven mode is the extraction table, as shown in Figure 2.1(a). Inputs to the extraction table are the PC of the committing instruction or the referred address for committing memory instruction, along with a one-bit I/D flag. For a given input, if the I/D flag is set, it means that the rest of the input is the instruction address of a committing instruction. Otherwise, the rest of the input is the memory address of data referred by a committing memory instruction. Outputs of the extraction table include a one-bit valid signal and a one-bit suspension signal. The valid signal indicates whether the input address has a match on the table; the suspension signal indicates whether the committing instruction corresponds to a monitored event that should suspends the use of the extraction table. We describe the concept of suspending the extraction table later in this section.

The structure of the extraction table is shown in Figure 2.1(b). The extraction table consists of two components. The TAG component and the DIRECTION component. the TAG component is used to specify whether an input address is of interest, and the DIRECTION component stores and sends output bits for all instructions that the TAG component found of interest to the monitor.

The TAG component is implemented with content-addressable-memory (CAM) [58]. Each entry of the CAM corresponds to an address (could be a PC or data address) and a one-bit I/D flag. The DIRECTION component of the extraction table is implemented as a small cache. Each word line of this cache is driven by the corresponding output from the CAM. When an instruction commits, the PC of this instruction is sent to the CAM and the I/D flag is set to 1; if a block in the CAM matches the input, the corresponding word line is set and DIRECTION bits are retrieved from the small cache. If the instruction is a memory instruction, it goes through the same process except the input address to the table is the referred memory address and

the I/D flag is set to D. By checking the valid bit output from the DIRECTION component, the extraction logic is able to determine whether to forward the result of the committing instruction. To support simultaneous look-ups of the table, this structure can be extended with multiple ports.

Since the size of the extraction table is limited and many monitor activities require monitoring contiguous memory addresses, extraction logic leverages the property of ternary CAM [58] to accommodate the address range. In a ternary CAM, a storage cell represents "0", "1" or "X" indicating "dont care" [58]. For example, to monitor all access to the elements of an array located between 0x8000a000 and 0x8000afff, only one entry with the address of 0x8000aXXX needs to be entered to the table.

For some segments of execution, the monitor software may require the extraction logic to forward all instructions and thus bypass the extraction table. For example, when the software is updating the extraction logic by loading a new set of interested instruction or memory addresses, the extraction table becomes temporarily inconsistent and its use should be prohibited until the update is done. To implement bypassing of the extraction table, Ex-Mon uses a one-bit suspension register to control the use of the extraction table, and the extraction table is bypassed when the suspension register is set. The mechanism of updating the extraction table is the following: when the monitoring system initializes the extraction logic, the suspension register is initially clear. The monitor software then sets the suspension bit of every extraction table entry that might trigger a table update. During the monitored execution time, each time an extraction table entry is found to match the TAG component, its suspension bit is copied by the DIRECTION component to the suspension register. If a committing instruction matches an entry that has the suspension bit as "1", the extraction logic notifies the monitor software that the monitor should start updating the extraction table. Moreover, from the next committing instruction, the extraction logic bypasses the extraction table and forwards every instruction's PC and data memory address to the monitor until the monitor resets the suspension register at the end of the update.

The table-driven mode is not efficient when there is a large number of instructions that are of interest to the monitor. In that case, the monitoring system ends up suspending the extraction table so often so that extraction table becomes less efficient. To overcome this disadvantage, we have designed a forward bit mode of extraction logic, as a supplementary or alternative way to select dynamic instruction information. The following section introduces the hardware components used for that mode.

#### 2.3 Forward-Bit-Based Extraction Logic

When the extraction logic operates in forward-bit-based mode, it assumes that the binary of the monitored program is augmented with an annotation. The annotation of the monitored program is an array of forward bits. Each bit corresponds to an instruction of the monitored program, indicating whether the result generated by the instruction should be extracted and forwarded. The extraction logic selects which instructions' results to forward based on their forward bit value.

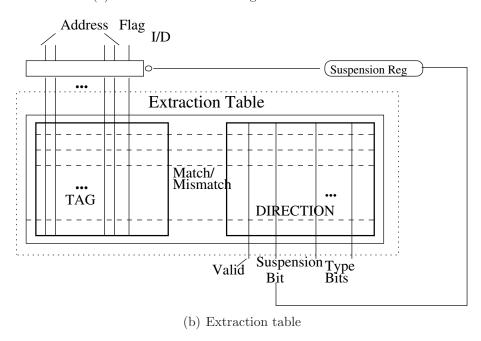

Two hardware components of the extraction logic are essential to implement the forward bit mode of extraction logic: (1) the fetching component that fetches the forward bits from memory and matches these bits with the corresponding instructions; and (2) the forwarding component that extracts and forwards the results of selected instructions whose forward bits are set. The following two subsections introduce the fetch component and the forward component in detail.

#### 2.3.1 Fetching Component

The fetching component is integrated into the fetching stage of the CPU pipeline. It fetches forward bits of monitored execution from user memory and copies forward bit of each instruction into the pipeline at the time when the instruction is fetched into the pipeline. Forward bits are generated by the monitoring compiler as a special annotation section in the binary of the monitored program. Every instruction in the code section of the binary of the monitored program has its own corresponding forward bit in the annotation section, indicating whether the instruction should have its result forwarded. When a monitored process is created, the content of the annotation section is mapped into the memory space of the monitored process. As the monitored process runs, the fetching component fetches the forward bit for each instruction that is fetched into the pipeline. Forward bits fetched by the fetching logic are later read by the forwarding component to decide whether the instruction should have its result written into the communication queue on the shared memory upon its commitment.

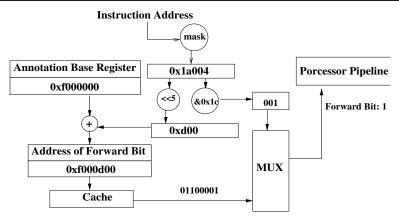

The key to the fetching component's reading forward bits is to calculate the address of the forward bit for every fetched instruction. To achieve this, the fetching component uses a special register, referred to as the Annotation Base Register (ABR), to keep the physical address of the base of annotation section in the memory space of the monitored process. ABR is initialized with that address when a monitored process is created by the monitoring system, and synchronized with any change in the annotation bases physical address.

When an instruction is fetched, its address is used as the input to a simple mapping function implemented by the hardware to calculate the offset of its corresponding forward bit. The fetching component adds this offset with its ABR value to compute the address of the byte in the annotation that contains the forward bit. Several lower bits of the instruction address are used to select the exact forward bit from the byte of forward bits fetched from annotation. This mechanism of calculating the address of meta-data is similar to that presented in MemTracker [32] with the exception that we calculate the meta-data address for instructions rather than for memory locations. Figure 2.2(a) shows the fetch logic that is implemented in SPARC architecture where

each instruction is 32-bit long. The example instruction has the offset 0x1a004 to the start of the code section, and its forward bit is the bit 1 of the byte fetched from the address from the physical address 0xf0000d00.

Some instructions executed by a monitored process, such as ones in dynamically loaded library codes, do not have forward bits because they do not appear in the monitored program's binary. These instructions are either all ignored or all forwarded, depending on monitoring requirements. If all of them ought to be forwarded, the extraction logic has to switch to the table-driven mode because their instruction body has to be sent to the monitor for interpretation. If they are to be ignored and extraction logic is in the forward bit mode, thee fetching component always assumes that their forward bits are all clear and does not calculate their address. The OS loader is changed to notify the extraction logic when the library code is loaded and unloaded.

Forward bit fetched by the fetching component are kept in the pipeline until the corresponding instruction retires. In order to keep forward bits in the pipeline, every entry of the reorder buffer (ROB) in the pipeline is augmented with a forward bit flag. The fetching component copies the forward bit of a fetched instruction to that flag when the instruction is inserted into ROB. For architectures such as X86 that translates an instruction into multiple micro operations in ROB, all the micro operations have the same forward bit as the instruction's forward bit.

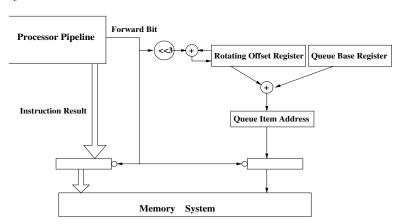

#### 2.3.2 Forwarding Component

The forwarding component is attached to the commit stage of a CPU pipeline. It uses forward bits fetched by the fetching component to decide whether the result or pertained memory address of an instruction should be forwarded to the monitoring running on another core through the communication queue. The communication queue is part of the shared memory between the monitor process and the monitored

process.

The key to writing the results or referred memory addresses of instructions to the communication queue is calculating the address of the queue entry to write. This is achieved by the forwarding component using two special registers: the queue base register (QBR) and the rotating offset register (RQR). QBR keeps the base physical address of the communication queue and RQR is a saturated counter that indicates the offset of the current available entry to write and is incremented after each forwarding. QBR and RQR are initialized at start-up time. The entries in the communication queue are synchronized at the entry level using full/empty bits. Figure 2.2(b) shows the implementation of the extraction logic in which each queue entry is 8 bytes long.

(a) Fetching Component: For each instruction, the address of its forward bit is calculated using the Annotation-Base Register(ABR) and the offset of the instruction in the code section. The instruction offset is calculated by masking the instruction address. In this example, each instruction is 32 bits in size, and thus the offset of the forward bit is calculated by left shifting the instruction offset by 5, and the highest 3 bits of the lowest 5 bits (32-bit long instruction is 4-byte aligned) of the offset are used to select the forward bit from a byte of forward bits.

(b) Forwarding Component: The forward bit associated with each instruction determines whether the result of this instruction should be forwarded through the communication queue. The address of the queue entry is calculated from the queue-base register (QBR) and the rotating-offset register (RQR). RQR is incremented after each forwarding.

Figure 2.2: Extraction Logic in Forward Bit Mode

## Chapter 3

#### Execution Models of

# Multi-core-based Program Monitor

This chapter presents two main execution models for implementing the multi-core-based dynamic program monitor: the dispatch-based model and the distill-based model. The program monitors implemented using these two models are significantly different from each other in the utilization of hardware support, the use of extracted information, and the performance. We begin this chapter with an example to give a straightforward illustration of dispatch-based and distill-based models, and show how both of them differ from the instrumentation-based monitor that is widely used on uniprocessor platforms. Then, we describe details of the basic execution model: the dispatch-based model and the more advanced distill-based model. Finally, we conclude the chapter by providing a qualitative analysis of the performance overhead associated with the two models and reasons for why the distill-based model is more efficient than the dispatch-based model.

```

foo(int* p, int y) {

int* q;

msg = receive();

int i,j,k;

switch(msg.type) {

i = 0:

do {

case LOAD:

VERIFY_LOAD(msg.body);

q = p + i;

VERIFY\_LOAD(q);

break;

k = *q;

case STORE:

VERIFY_STORE(msg.body);

j = k*k + i;

VERIFY\_STORE(q);

break:

*q = j + y;

default:

break:

} while(i<1024)

} while(...)

(a) Instrumentation-based monitor:

(b) Dispatch-based monitor:

calls to the verifying routines are

patcher invokes the appropriate verifi-

inserted in the original program.

cation routine based on the forwarded

record.

foo(int* p, int y) {

foo(int p, int y) {

int* q;

int q;

p = receive();

i = 0;

i = 0;

do {

do {

q = receive();

q = p + i;

VERIFY\_LOAD(q);

VERIFY_LOAD(q);

VERIFY\_STORE(q);

VERIFY\_STORE(q);

i = receive();

} while(i<1024)

} while(i<1024)

(c) Distill-based

monitor

(unop-

(d) Distill-based monitor (optimized):

timized):

the monitor executes a

the monitor executes an optimized dis-

distilled version of the program.

tilled version of the program.

```

Figure 3.1: Four different Implementations of the Memory-bug Detection Monitor.

#### 3.1 Example of Monitor Models

In this section, we use an example to show the differences between the distill-based monitor model, the dispatch-based monitor on multi-core, and the instrumentationbased monitor on uniprocessor.

Figure 3.1(a) shows the sample program with instrumentation for monitoring. The monitoring requirement is to examine all memory access through pointers to ensure that there is no access to unallocated memory and uninitialized memory for load operation. Therefore, instrumentation invokes monitoring functions VER-IFY\_STORE and VERIFY\_LOAD immediately before the examined store and load.

Figure 3.1(b) shows the dispatch-based monitor for the sample program that performs the same check as the instrumentation-based monitor does in Figure 3.1(a). It features a dispatch routine that continuously reads the execution records forwarded from the monitored code, and dispatches them to monitoring functions.

Figure 3.1(c) shows the distill-based monitor for the sample program that performs the same monitoring work. The monitor comprises of invocations to the function receive that fetches the value of q and i and the monitoring functions VER-IFY\_STORE and VERIFY\_LOAD with values of q as argument. The control flow statement while(i<1024), upon which the invocations to monitoring functions depend, is preserved.

In this example, there is a notable performance advantage of multi-core-based monitor models over single-core-based instrumentation-based monitor. Multi-core-based monitors, both dispatch-based and distill-based, can execute monitoring code in parallel to the monitored execution. This fact indicates that there is no competition with monitored execution for hardware resources in a core, such as the pipeline, physical registers in the latter two monitors.

#### 3.2 Dispatch-Based Monitor

A dispatch-based monitor consists of three essential elements: (i) a dispatching routine that retrieves and decodes messages and dispatches them to appropriate monitoring functions that perform monitoring tasks; (ii) a set of monitoring functions; and (iii) routines to initiate and update the extraction table so that hardware support can capture events that are related to the monitored execution. In this section, we describe these three elements in detail.

```

data declarations:

typedef struct message_struct

{Type, Address, Value, I/D flag }

message_struct msg;

List of events for initializing and

updating the extraction table.

message_struct Msg_List[];

algorithm DispatchRoutine:

InitializeExtractionTable(Msg_List);

while (true)

msg = ReadQueue();

switch (msg.Type))

case ALLOC:

verify_alloc(msg);

break;

case FREE:

verity_free(msg);

break;

case LOAD:

verity_load(msg);

break;

case UPDATE:

UpdateExtractionTable(msg);

break;

. . .

case EXIT:

monitor_exit(msg);

break;

end switch

end while

end algorithm

(a) Dispatching routine.

verify\_free(message)

begin

if (AllocatedBlockLookup(message.Address))

AllocatedBlockRemove(message.Address);

return;

else

ReportIllegalFree(message);

end if

end

```

(b) a monitoring function to verify call to FREE.

Figure 3.2: Dispatch-based Monitor for Memory-bug Detection

#### 3.2.1 Dispatching Routine

The dispatching routine is usually structured as a while loop whose body is mainly a switch-case structure. Each iteration of the loop decodes a message fetched from the communication queue, and processes it by dispatching it to the appropriate monitoring function. Messages that are not relevant to monitoring purpose are dispatched to the default case. When a special message EXIT is processed, that corresponds to the termination of the monitored program, the loop will end. The algorithm that implements the dispatching routine for memory-bug-detection is shown in Figure 3.2(a). In addition, Figure 3.2(b) shows an example of the monitoring function that checks whether there is a double free bug. The details of the double free bug as one type of memory bug can be found in [62, 63].

#### 3.2.2 Monitoring Functions

Monitoring functions perform the actual monitoring tasks manually written by programmers or automatically generated by compiler according to the monitoring requirements. Monitoring requirements can be specified in the format of mathematical logic rules that unequivocally express the requirements an execution has to satisfy for safety and reliability reasons. For example, in the task of memory-bug-detection, in order to prevent memory leakage, we may have the following requirement statement: an address passed as an argument to a *free* function call must be the return value of a function of allocation. This statement can be formalized as a CTL(Computational Tree Logic) [46, 47] rule as the following:  $\mathbf{AG}(free(addr) \to addr = alloc(\_))$ . Here  $\mathbf{A}$  and  $\mathbf{G}$  are operators of CTL-FV, indicating that the formula it follows must be true on all possible execution paths of the program.  $\mathbf{addr}$  is a free variable that can be substituted by all applicable addresses.  $alloc(\_)$  can represent any function with any type of parameter that does memory allocation.

#### 3.2.3 Initialization and Update Routines

There are two types of routines in a dispatch-based monitor that are in charge of instructing the hardware support in the table-driven mode to extract information that is relevant to the monitoring purposes. In this dissertation, we refer to these as InitializeExtractionTable and UpdateExtractionTable, respectively. InitializeExtractionTable initializes the extraction table and fills it with addresses or address ranges of PCs and data memory locations that are interested by monitor. UpdateExtractionTable is used to update the extraction table as described in Chapter 2.

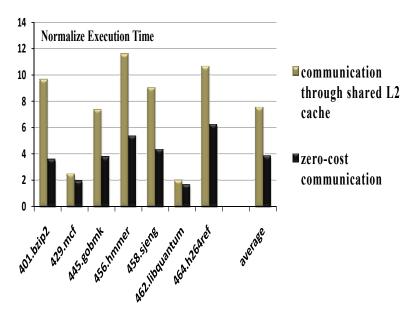

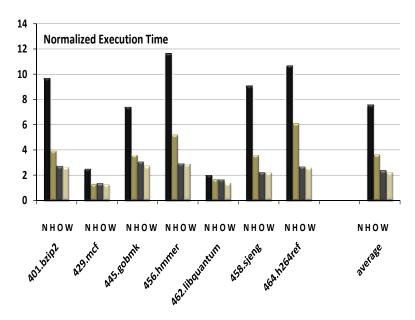

Figure 3.3: Performance Comparison of Dispatch-based Dynamic Monitors on Multi-core for Taint Propagation:left bar represents performance with communication through a shared L2 cache, right bars represent performance of zero-cost communication

#### 3.3 Distill-based Monitor

This section presents a different monitor model, referred to as the distill model, that takes full advantage of the extraction logic, described in Chapter 2. Monitors in the distill model, referred to as distill-based monitors, achieve significant performance

improvements, compared to the dispatch-based monitors.

We start this section with an brief introduction to the key idea of the distill-based monitor model, elucidating how it accelerates dynamic program monitoring. After that we demonstrate how to generate distill-based monitor from monitored code.

#### 3.3.1 Key Idea of Distill-based Monitor

The key idea of the distill-based monitor model is that the compiler could generate monitor code targeting individual monitored program. This way, the monitor is customized to the monitored program by the monitoring compiler as it has the knowledge of what values are needed to conduct the monitoring activity during the execution of the monitored code. With this knowledge, the monitoring system can instruct the extraction logic to forward only the values that are relevant to monitoring purpose. As a result, the distill-based monitor model is able to reduce communication between the monitored and monitoring cores, and in turn improve performance significantly for heavy load monitoring tasks that require a large quantity of information.

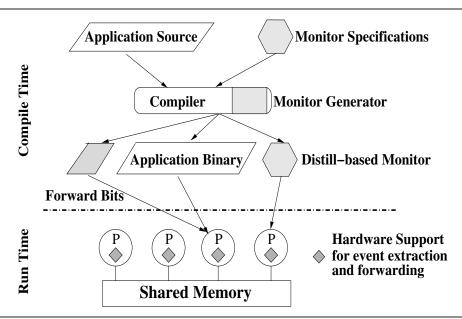

Figure 3.4: Overview of the Distill-based Monitoring System: the shaded boxes represent monitor related components. From user-defined monitor specifications, the monitor generator creates the distill-based monitor. The monitored application is annotated with forward bits, that are interpreted by the underlying hardware support to forward results of selected instructions.

### 3.3.2 Generating Distill-based Monitor

The distill-based monitor is generated by distilling the monitored code. In this section, we focus on how the monitor code generator generates the distill-based monitor without optimization, and we introduce the optimization in the next section.

The workflow of generating the distill-based monitor is illustrated in Figure 3.4. The input to the monitor code generator consists of two parts: the original source code of the monitored program and the monitoring specifications. These specifications can be expressed as annotations to the original monitored program marking where and what instrumentation of the monitoring function would occur if an instrumentation-based monitor was implemented. The output of the monitor code generator is the distill-based monitor and an annotation section in the monitored code's binary where

each instruction has a bit indicating whether the result of the instruction needs forwarding.

The monitor code generator generates code at the procedure level. For each procedure, it identifies invocations to the monitoring functions and all branch instructions on which the invocations depend. For each argument used in the invocation of monitoring functions, if its value cannot be known at compilation time, a fetch from the communication queue operation is inserted as an invocation to receive() function in the distill-based monitor. The code generator also marks each instruction that generates a value that should be fetched, indicating that the result of the instruction should be forwarded during the monitored execution. Similarly, for each value used to decide the direction of an identified branch, a receive() is generated and the instruction generating the value is marked, as well. Finally, the code is distilled by removing instructions other than the identified branch instructions, the invocations to monitoring functions and the receive() operations. This distilled code is the monitor used in the distill-based monitoring system. The marks that are generated by the monitor code generator form an annotation section and is inserted into the binary of monitored program.

The distill-base monitor generated by the code generator (without optimization) consists of two types of operations: invocations of the monitoring functions and invocations of the communication function, a.k.a receive() function. The monitoring functions perform monitoring operations and the communication function fetches values for monitoring functions from the communication queue. In addition, a value returned by the communication function could used to decide the outcome of a branch instruction that controls the invocation of monitoring functions.

#### 3.3.2.1 Monitoring Functions

In this chapter, for the purpose of performance evaluation, we report the implementation of monitoring functions for two intensive monitoring tasks: taint-propagation and memory-bug-detection.

The details of taint-propagation can be found in [64, 65]. In our implementation, the distill-based monitor maintains a taint status bit for each byte of the monitored program's user memory space, as well as a taint status bit for each architectural register used in the program. These taint status bits are kept in the monitor's memory space as a shadow memory of the memory space of the monitored execution. A monitored execution may invoke system calls such as read or recv that writes to user memory with data from untrustworthy sources. When such invocations occur, the monitor invokes the Taint\_Init function to set the corresponding taint status bits in the shadow memory. For each dynamic instruction in the monitored execution, the monitor executes a corresponding status propagation operation to propagate taint status around shadow locations accordingly. Taint status bits of indirect jump targets, format strings, and system call arguments are checked by the monitor to detect potential security breaches. Overall, the monitor needs to know all the referred data memory addresses and the directions of all conditional branches in the monitored program to conduct correct verification without false negative and false positive.

It is noteworthy that using the distill-based taint-propagation monitor, a large amount of monitoring function invocations do not need to be forwarded because their parameters are register numbers that are known at compile time. For example, arithmetic operations such as Add\$R1,\$R2, can be translated into corresponding taint-propagation monitoring functions such as TaintRegProp(1, 2), that propagates the taint bit of register R1 to the taint bit of register R2. Since the parameters are the register numbers known at compilation time, this type of monitoring function requires

no communication. In contrast, a dispatch-based monitor has to generate communication for these operations. This optimization alone gives a significant performance advantage to the distill-based taint-propagation monitor since a large portion of taint propagation are between registers.

We also implemented monitoring functions for memory-bug-detection. The monitoring functions are similar to those used in the MemTracker [32], except that the state bits in our implementation are maintained at word granularity rather than bit granularity. Moreover, when there is a read to uninitialized data, our monitoring function issues a warning immediately rather than wait until the value read is actually used.

The distill-based program monitoring system enables users to apply their knowledge about the code to make monitors even more efficient. For the example program in Figure 3.1(c), if the user knows in advance that pointer q points to an area whose size is always greater than the size of 512 integers, then half of the monitoring activities and their correspondent communication can just be eliminated.

# 3.4 A Qualitative Analysis of Performance Overhead

In this section, we start with a qualitative analysis of performance overhead associated with the dispatch-based model, pointing out sources of the performance overhead. Then we show how the distill-based monitor eliminates some of the sources of performance overhead and the distill-based model. The result of the analysis indicates that the performance overhead of the distill-based model should be lower than the dispatch-based model. This conclusion will be vindicated by the experimental results presented in Chapter 4.

### 3.4.1 Analysis of Performance Overhead of Distill-based Monitor

Performance overhead caused by a dispatch-based monitor is lower than that of instrumentation-based monitor, because a separate processor core is used and thus the monitor runs in parallel to the monitored execution. However, this overhead is still fairly significant. The causes of this high performance overhead are the unnecessary communication and dispatching related to irrelevant messages. In a dispatch-based monitoring system, the monitored process may forward data that are irrelevant by the monitor. In the sample program in Figure 3.1, if we are interested only in verifying memory operations by the pointer, the monitor does not need execution results from other types of operations, thus communication for these results is unnecessary. It is true that a dispatch-based monitor can use the extraction table of the hardware support to select data to be forwarded, but at a cost of possibly frequent updating of the extraction. The more frequent the extraction table is updated, the more the irrelevant information to be forwarded because the extraction logic forwards everything during the period of update. Furthermore, in the dispatch-based monitor model, the type of information of the message has to be communicated, which is solely for dispatching purpose and thus can be considered unnecessary.

Communication is the bottleneck of performance. Figure 3.3 presents the results of a study on the impact of communication on the performance for multi-core-based program monitoring using dispatch-based monitors. Here monitors perform taint propagation [64, 65] and memory-bug-detection [66, 62, 66, 67] for SPEC2006INT [68] benchmarks, respectively. The bars represent the execution time of monitors normalized to that of the benchmarks without monitoring. The communication queue between cores is implemented in shared memory and resides in the shared L2 cache most of time during monitoring. We also assume that each core has a private L1

data cache, and therefore communication of a value may incur a coherence miss that requires a fetch of the data from the shared L2 cache. This causes L2 cache access latency. Using the above assumptions, the slowdown to the benchmarks with the two-process dispatch-based monitoring is represented by the left bars. The right bars represent the slowdown of the dispatch-based monitoring in an ideal situation where the communication is latency-free. The figure suggests that a significant portion of performance overhead is caused by communication.

In addition to the communication cost, dispatching a message consumes a certain number of CPU cycles of the monitor core. It involves decoding a message to get its type, extracting the value from the message, and jumping to the place where the appropriate monitoring is invoked.

### 3.4.2 How Distill-based Monitor Reduces Performance Overhead

Figure 3.1(c) demonstrates, with an example, how the distill-based monitor reduces communication for dynamic program monitoring. The sample program communicates only values of q and i. It leverages the forward-bit mode of the hardware support extraction logic to selectively forward values. Communication of values that are not relevant to the monitoring purpose is eliminated in the distill-based monitor. Since most, if not all, monitoring tasks need only a portion of all values generated by the monitored execution, this reduction is significant.

The distill-based monitor is optimized by replacing the communication operation with less expensive computation operations on the monitor side. For example, in Figure 3.1(c), the communication of data value q and i can be replaced by local computations of simple integer add operations. If the monitor compiler initiates only the communication of the value of p, then all subsequent values of q and i can be

computed locally in the monitor code. Therefore, in Figure 3.1(d) the number of invocations to the communication function receive() for the while loop is reduced from 2048 to 1. As communication is a notable source of performance overhead, this optimization leads to an even greater performance overhead. This optimization of distill-based monitor is the main focus of the next chapter, Chapter 4.

# Chapter 4

# Optimization of Distill-based

### Monitor

The distill-based monitor can be optimized by eliminating the communication of values that can be computed by the monitor locally. In this chapter, we present details of algorithms that implement this optimization of reducing communication by computing values locally. The chapter starts with an introduction to general ideas and concepts about the optimization, then we give an overview of the algorithm that implements the optimization. Following that, we describe the different kinds of information needed by the algorithm and the ways in which they are collected. After that, we describe the details of the algorithm along with discussion of the optimality and complexity of the algorithm. Finally, we present detailed results of the performance evaluation of the optimized distill-based monitor, comparing it with the basic distill-based monitor, the dispatch-based monitor and the instrumentation-based monitor. To illustrate the optimization in a more lucid way, we use a sample program shown in Figure 4.1 that is slightly more sophisticated than the example shown in 3.1. The sample program with instrumentation, the unoptimized distill-based monitor, and optimized version of the distill-based monitor are shown in Figure

```

foo(int* a, int y) {

foo(int* a, int y) {

foo(int* a, int y) {

int *p;

int *p;

int *p;

int i=0, j=0;

int i=0, j=0;

int i=0, j=0,;

do \{

y = receive();

a = receive();

p = a + i;

do {

y = receive();

VERIFY\_STORE(p);

p = receive();

do \{

*p = i;

VERIFY\_STORE(p);

p = a + i;

j = j + i;

VERIFY\_STORE(p);

\mathbf{if}\ (i{=}{=}y)\ \{

if (i==y) {

p = receive();

if (i==y) {

p = a + j;

\mathbf{VERIFY\_STORE}(p);

p = receive();

VERIFY\_STORE(p);

VERIFY\_STORE(p);

*p = 0;

else {

}

}

p = receive();

else {

else {

VERIFY\_STORE(p);

j = y + i;

j = y + i;

p = a + j;

p = a + j;

i = receive();

VERIFY\_STORE(p);

\mathbf{VERIFY\_STORE}(p);

} while (i<1024)

*p = y;

i++;

}

} while (i<1024)

i++;

} while (i<1024)

```

(a) Sample monitored code: original (b) Unoptimized monitoring code (c) Optimized monitoring code: code with instrumentation communication are replaced by local computations

Figure 4.1: Code Example of Using Compiler to Reduce Communication

4.1(a), 4.1(b), and 4.1(c), respectively.

# 4.1 General Ideas and Concepts of the Optimization

Essentially, the optimization of the distill-based monitor in the context of this thesis reduces overall communication volume between cores by replacing the communication of some values required by monitoring purposes with local computation on the monitor side. In this section, we introduce ideas and concepts that lead to a better

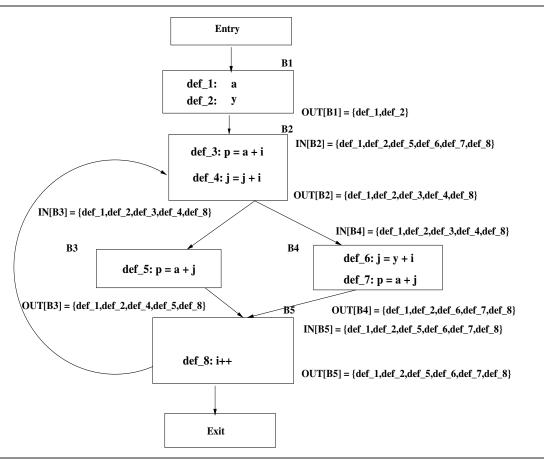

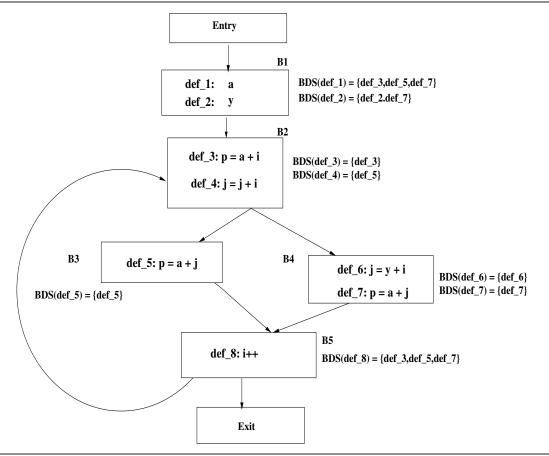

Figure 4.2: Control Flow Graph of the Sample Program and Results of Reaching Definition DFA

understanding of the optimization.

We start with studying the correctness requirement and the effectiveness requirement of the optimization. In the context of dynamic program monitoring, the correctness of the optimization means that the optimized distill-based monitor must perform exactly the same monitoring operations in exactly the same order as the monitor without optimization. Thus, if a value is communicated in the unoptimized monitor, it must be either computed or communicated in its corresponding optimized monitor. In a program, values are generated at points of variable definitions. In this section, we use BasicCommu set to denote the set of variable definitions whose values are communicated in the unoptimized distill-based monitor. For the sample program

in Figure 4.1 with its control flow graph shown in Figure 4.2, the BasicCommu set is  $\{def\_2, def\_3, def\_5, def\_7, def\_8\}$ .

Making the optimization effective means that optimized monitors must outperform their corresponding unoptimized monitors. To guarantee this, two constraints must be met: first, computations introduced in the optimized monitor must compute only those variable definitions that one or more variable definitions in the BasicCommu set are directly or indirectly dependent. For example, in Figure 4.2,  $def\_3$  and  $def\_8$  are in BasicCommu and are dependents of  $def\_8$ , therefore, computing  $def_{-}8$  on the monitor side may eliminate communication for  $def_{-}3$  and  $def_{-}8$ . In this dissertation, we use OptCompute set to denote the set of these computed definitions. Second, the cost of computing values locally must not exceed the cost of communicating them. This is guaranteed by comparing the cost of computations involved in deducing those values against the cost of communicating them. It is worthy pointing out that the optimization may replace a communicated value with local computations and communication of a value that is not defined in the BasicCommuset. This may seem like a performance degradation at the first glance. It is possible for the additional communication to achieve better performance by eliminating other communications. In this dissertation, we refer to the set of the communicated variable definitions in an optimized monitor as the OptCommu set.

Thus, in the context of this dissertation, to optimize the distill-based monitor is to find the OptCompute set and the the OptCommu set that minimize the overall performance overhead associated with the monitor. In the example shown in Figure 4.2, these two sets are:

$$OptCompute = \{def\_3, def\_6, def\_7, def\_8\}$$

$$OptCommu = \{def\_1, def\_2, def\_5\}$$

### 4.2 Algorithm Overview

The algorithm that implements the optimization is based on the data flow analysis (DFA) framework. Inputs of the algorithm are the control flow graph (CFG) of the monitored program and the BasicCommu set of the monitored program. The algorithm traverses CFG, visiting each basic block to decide the OptCompute and OptCommu sets for the entire CFG. While visiting each basic block, the algorithm examines every variable definition in the block, decides whether it should go into the OptCompute, the OptCommu set, or be ignored if it does not contribute to any value needed by monitoring function.

The algorithm makes decisions for all variable definitions in a basic block corporately rather than individually. It actually evaluates the cost and the benefit of combinations of possible choices for each variable definitions and choose the combination with the highest overall benefit as its decision for the basic block. In the context of the algorithm, the benefit and the cost of the decision are measured in the execution time of the monitor. Since the optimization reduces monitor execution time solely through reducing communication, a decision's benefit is estimated by counting the number of communications that can be eliminated by the decision. The cost is the cost of additional computations and communications the optimization introduces into the monitor.

Through the DFA framework, the decision made for a basic block will be propagated to successor basic blocks to help them make decisions. All the variable definitions on CFG marked for communication form the OptCommu set, and those marked for computation form the OptCompute set. For all definitions in the OptCommu set, the compiler generates communication functions in the optimized monitor and sets the forward bit of the corresponding instructions in the monitored program. Computation instructions that generate definitions in the OptCompute are preserved in the

distill-based monitor program, and all other instructions are removed.

### 4.3 Information Needed by the Algorithm